# Technical Reference Manual P/N: GCS-C03500 Rev 2.03

© 1997 ATI Technologies Inc.

The information contained in this document has been carefully checked and is believed to be entirely reliable. No responsibility is assumed for inaccuracies. ATI reserves the right to make changes at any time to improve design and supply the best product possible.

All rights reserved. This document is subject to change without notice and is not to be reproduced or distributed in any form or by any means without prior permission in writing from ATI Technologies Inc.

ATI, VGA Wonder, mach8, mach32, mach64, 3D RAGE, 8514ULTRA, GRAPHICS ULTRA, GRAPHICS VANTAGE, GRAPHICS ULTRA+, GRAPHICS ULTRA PRO, GRAPHICS PRO TURBO 1600, GRAPHICS PRO TURBO, GRAPHICS XPRESSION, WINTURBO, and WINBOOST are trademarks of ATI Technologies Inc. All other trademarks and product names are properties of their respective owners.

#### **Record of Revisions**

| Release | Date     | Description of Changes                   |

|---------|----------|------------------------------------------|

| 1.00    | Oct. 96  | First Release                            |

| 1.01    | Nov. 96  | Preliminary Draft                        |

| 1.02    | Jan. 97  | Preliminary Draft                        |

| 1.03    | Feb. 97  | Preliminary Draft                        |

| 1.04    | Mar. 97  | Preliminary Draft                        |

| 1.05    | May 97   | Final Draft                              |

| 2.00    | June 97  | Second Release Draft                     |

| 2.01    | June 97  | Second Release Final                     |

| 2.02    | Aug. 97  | Release                                  |

| 2.03    | Sept. 97 | Updates to DAC Interface; format changes |

# **Technical Reference Manuals**

#### 3D RAGE PRO series

- 3D RAGE PRO<sup>TM</sup> Register Reference Guide (RRG-GO3500)

- 3D RAGE PRO<sup>TM</sup> Graphics Controller Specifications (GCS-C03500)

# Table of Contents

| Chap | ter 1: I | ntroduction                  |       |

|------|----------|------------------------------|-------|

| 1.1  | About T  | This Manual                  | 1-1   |

| 1.2  | Conven   | tions                        | 1-1   |

|      | 1.2.1    | Mnemonics                    | 1-1   |

|      | 1.2.2    | Numeric Representation       |       |

|      | 1.2.3    | Acronyms                     |       |

| Chap | ter 2: ( | Overview                     |       |

| 2.1  | Unique   | Features                     | 2-1   |

|      | 2.1.1    | AGP 2X mode                  |       |

|      | 2.1.2    | Floating-Point Set-up Engine | 2-1   |

|      | 2.1.3    | 100 MHz SGRAM                | 2-1   |

|      | 2.1.4    | DVD and Video Support        | 2-2   |

| 2.2  | Feature  | List                         | 2-2   |

|      | 2.2.1    | General Features             | 2-2   |

|      | 2.2.2    | 2D Acceleration              | 2-3   |

|      | 2.2.3    | 3D Acceleration              | 2-3   |

|      | 2.2.4    | Motion Video Acceleration    | 2-4   |

|      | 2.2.5    | AMC Operation                | . 2-5 |

| 2.3  | Product  | t Family                     | . 2-5 |

|      | 2.3.1    | Chip Packaging Options       |       |

|      | 2.3.2    | Add-on Cards                 |       |

| 2.4  | Softwar  | re Support                   | . 2-6 |

| 2.5  | Market   | Orientation                  | . 2-7 |

|      | 2.5.1    | Corporate PC Market          |       |

|      | 2.5.2    | Consumer PC Market           | . 2-7 |

| Cnapter 3: F  | unctional Description                          |      |

|---------------|------------------------------------------------|------|

| 3.1 3D Graph  | nics Coprocessor                               | 3-2  |

| 3.2 2D Engin  | e                                              | 3-2  |

| 3.3 Video Co  | processor                                      | 3-3  |

| 3.4 Host Bus  | Interface                                      | 3-3  |

| 3.5 Memory    | Controller and Interface                       | 3-4  |

| 3.6 Extended  | VGA Graphics Controller                        | 3-4  |

|               | ntroller (CRTC)                                |      |

|               | Controller                                     |      |

| - •           | AC                                             |      |

|               | ple Clock Synthesizer                          |      |

| _             | re Cursor                                      |      |

|               | ultimedia Channel (AMC)                        |      |

|               |                                                |      |

| Chapter 4: In | nterfaces                                      |      |

|               | I Bus Interface                                |      |

|               | The AGP Bus Interface                          |      |

|               | The PCI Bus Interface                          |      |

|               | Interfaces                                     |      |

|               | SDRAM Interface                                |      |

|               | SGRAM Interface with 128x32x2 (8 Mbit) SGRAMs  |      |

|               | SGRAM Interface with 256x32x2 (16 Mbit) SGRAMs |      |

|               | SGRAM Interface with 512x32x2 (32 Mbit) SGRAMs |      |

| 4.2.6         | SO-DIMM Module Interface                       | 4-11 |

|               | External DAC Interface for WRAM                |      |

|               | WRAM Interface                                 |      |

|               | EPROM Interface                                |      |

| 4.2.10        | Flash Memory Interface                         | 4-15 |

| 4.3 EEPRON    | M Interface                                    | 4-16 |

| 4.4 General   | Purpose I/O Control                            | 4-17 |

| 4.5 ATI Mul   | timedia Channel 2.0 Interface (AMC)            | 4-18 |

| 4.6 Analog (  | Output Section                                 | 4-19 |

|               |                                                |      |

| Chapter 5: Controller Configuration                                                                 |     |

|-----------------------------------------------------------------------------------------------------|-----|

| 5.1 Strap Resistors Summary                                                                         | 5-1 |

| 5.2 Strap Resistor Description                                                                      | 5-4 |

| Chapter 6: Pin Descriptions                                                                         |     |

| 6.1 Table Conventions                                                                               | 6-1 |

| 6.2 AGP/PCI Bus Interface Implementation                                                            | 6-2 |

| 6.3 Memory Interface                                                                                | 6-3 |

| 6.4 Monitor Interface                                                                               | 6-4 |

| 6.5 External Crystal Interface                                                                      | 6-4 |

| 6.6 Optional ATI Multimedia Channel Interface                                                       |     |

| 6.7 I2C Interface (BGA only)                                                                        |     |

| 6.8 External DAC Interface                                                                          | 6-6 |

| 6.9 SCAN Testing and Modes                                                                          | 6-6 |

| 6.10 Optional EEPROM Interface                                                                      |     |

| 6.11 Optional EPROM Interface                                                                       |     |

| 6.12 Flash Memory for ROM                                                                           |     |

| 6.13 Monitor ID for DDC Support                                                                     |     |

| 6.14 Power and Ground Pins                                                                          |     |

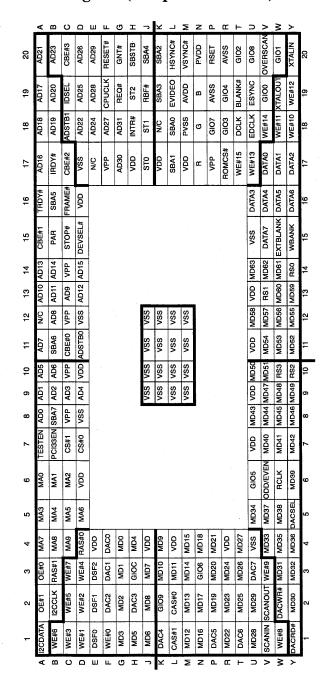

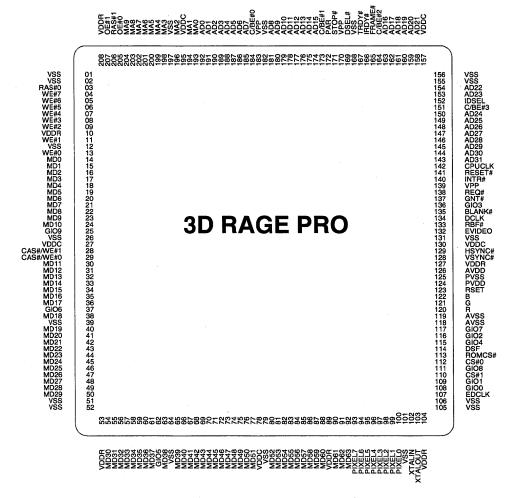

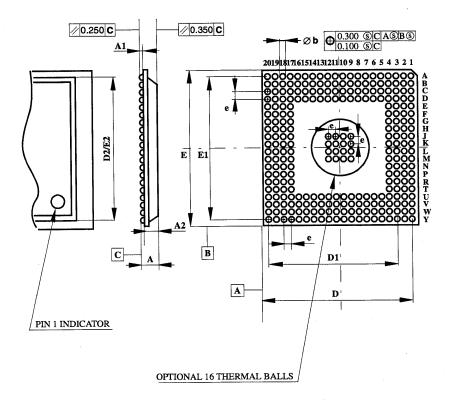

| 6.15 3D RAGE PRO Pin Listings (256-pin BGA)                                                         | 6-8 |

| 6.16 3D RAGE PRO Pin Listings (208-pin PQFP)                                                        |     |

| Chapter 7: Timing Specifications                                                                    |     |

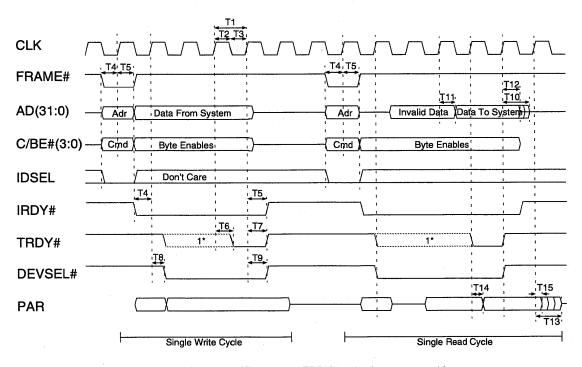

| 7.1 3D RAGE PRO Bus Timing                                                                          |     |

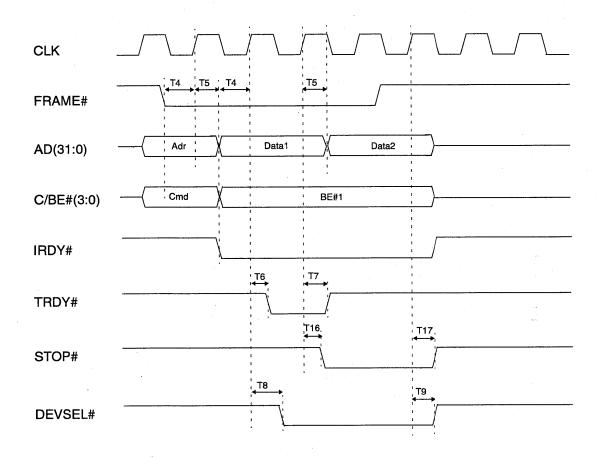

| 7.1.1 Single Read/Write Cycle Timing                                                                |     |

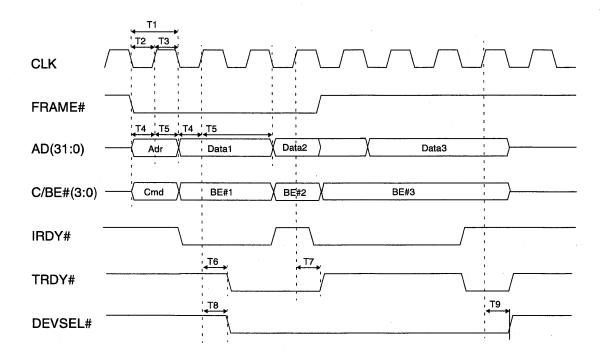

| <ul><li>7.1.2 Disconnect On Burst Cycle - PCI Bus</li><li>7.1.3 Burst Access Timing - PCI</li></ul> |     |

| 7.1.3 Burst Access Timing - PCI                                                                     |     |

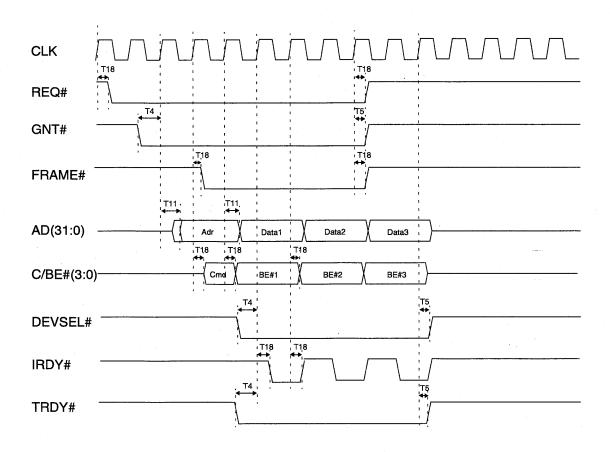

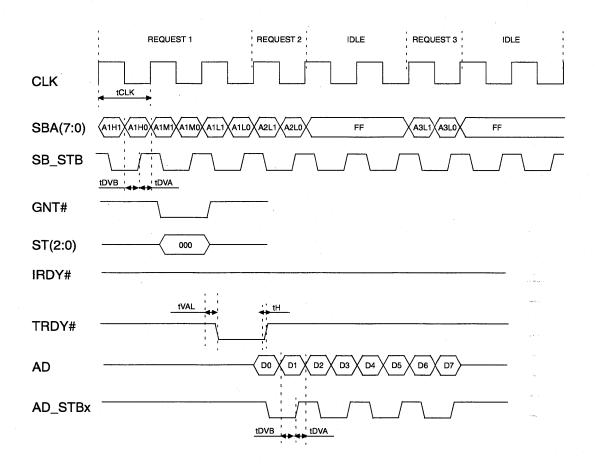

| 7.1.5 AGP Timing                                                                                    |     |

| 7.2 Memory Timing                                                                                   |     |

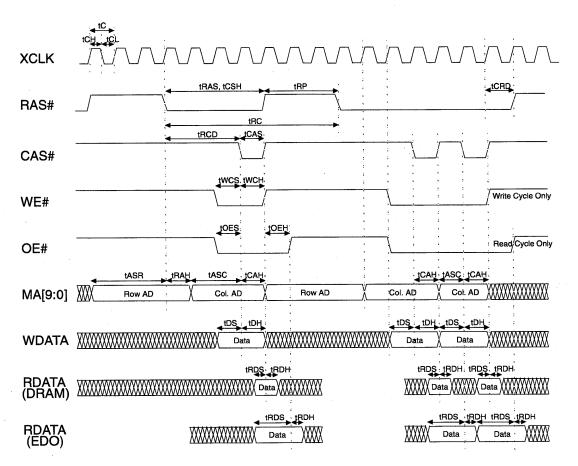

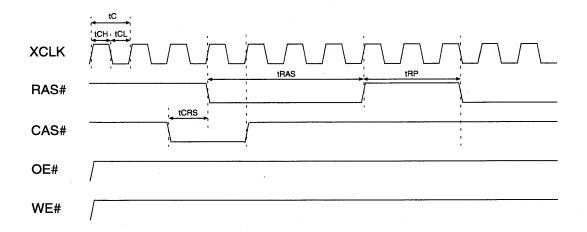

| 7.2.1 DRAM/EDO DRAM Cycle Timing                                                                    |     |

#### Table of Contents

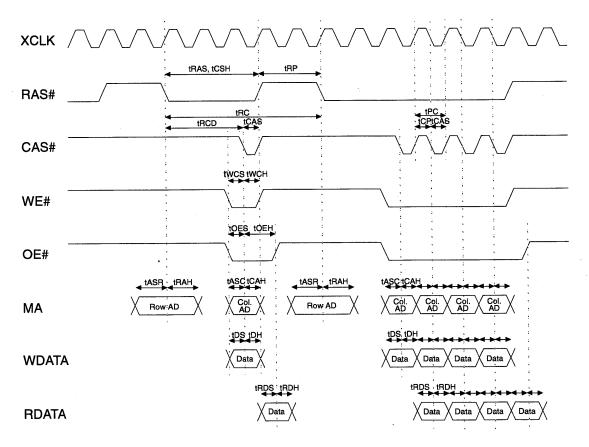

|       | 7.2.2    | Hyperpage EDO DRAM Cycle Timing             | 7-12 |

|-------|----------|---------------------------------------------|------|

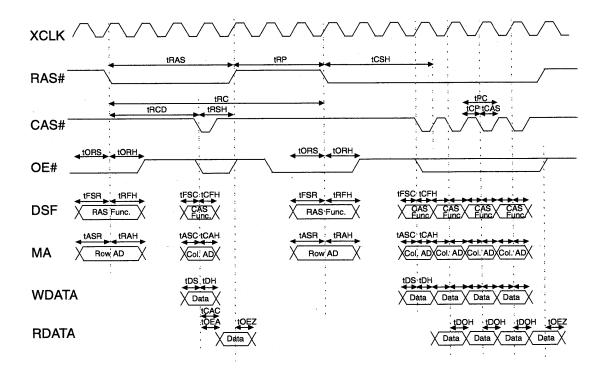

|       | 7.2.3    | WRAM Cycle Timing                           | 7-14 |

|       | 7.2.4    | DRAM Refresh Cycle Timing                   |      |

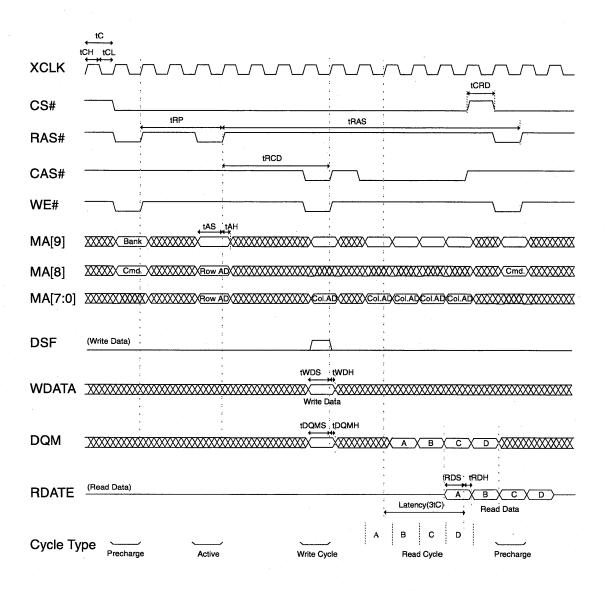

|       | 7.2.5    | SDRAM/SGRAM Cycle Timing                    |      |

| 7.3   | Memor    | y Controller Register Programming Examples  | 7-19 |

|       | 7.3.1    | DRAM, EDO DRAM                              |      |

|       | 7.3.2    | Hyperpage EDO DRAM                          | 7-20 |

|       | 7.3.3    | WRAM                                        | 7-21 |

|       | 7.3.4    | SDRAM/SGRAM                                 | 7-22 |

| Chapi | ter 8: ( | Chip Specifications                         |      |

| 8.1   | Electric | al Characteristics                          | 8-1  |

|       | 8.1.1    | Maximum Rating Conditions                   | 8-1  |

|       | 8.1.2    | Recommended DC Operating Conditions         | 8-1  |

|       | 8.1.3    | AC Characteristics                          |      |

|       | 8.1.4    | DC Characteristics                          | 8-2  |

|       | 8.1.5    | Input/Output Specifications                 | 8-3  |

|       | 8.1.6    | DAC Characteristics                         |      |

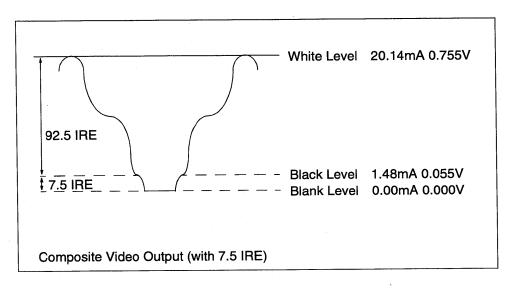

|       | 8.1.7    | Calculating RSET Resistance (DAC Interface) | 8-6  |

|       | 8.1.8    | Analog Output Specification                 | 8-8  |

| 8.2   | Therma   | ıl Characteristics                          | 8-9  |

|       | 8.2.1    | Maximum Ambient Temperature                 | 8-9  |

|       | 8.2.2    | Junction Temperature                        | 8-9  |

| 8.3   | Power a  | and Case Temperature Measurements           | 8-10 |

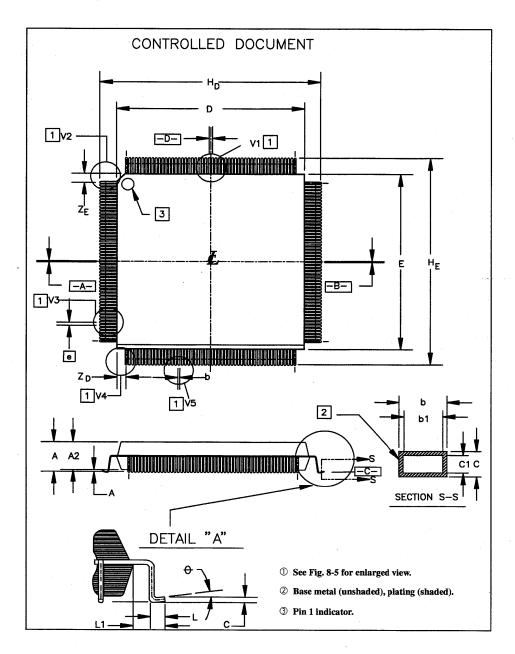

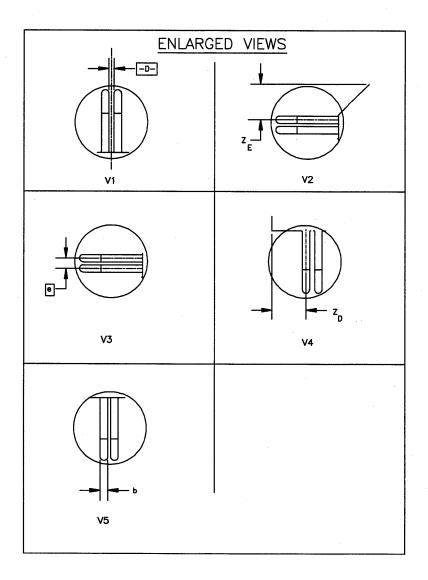

| 8.4   | Physica  | al Dimensions                               | 8-11 |

| 8.5   | Enviro   | nmental Requirements                        | 8-15 |

|       | 8.5.1    | Ambient Temperature                         |      |

|       | 8.5.2    | Relative Humidity                           |      |

|       |          |                                             |      |

# Appendix A: Layout Considerations

| A.1 AGP S  | Signal Routing                  | A-1 |

|------------|---------------------------------|-----|

|            | Trace Length                    |     |

| A.1.2      | AGP signal grouping and Routing | A-2 |

| A.1.3      | Signal Guarding and Trace Pitch | A-2 |

|            | Layout Considerations           |     |

| A.3 Routin | ng and Layer Assignments        | A-5 |

| A.3.1      | Star Grounding                  | A-5 |

|            | Local Bypassing                 |     |

|            | Signal Referencing              |     |

|            |                                 |     |

# Index

This page intentionally left blank.

#### 1.1 About This Manual

This manual is part of a set of reference documents which provide information necessary to design the 3D RAGE PRO into a graphics subsystem. These documents are listed in the System Publications Index at the beginning of this manual.

The electrical and thermal characteristics described in this document are specific to the 3D RAGE PRO manufactured using UMC's 0.35µm process — which has voltages of 3.3V core, 5.0V PCI I/O, 3.3V AGP, and 3.3V memory interface. Please contact ATI to obtain information on how to support all of ATI's graphics controllers, steppings, and foundries in one PCB design.

#### 1.2 Conventions

#### 1.2.1 Mnemonics

Mnemonics are used throughout this manual in place of external strap pin resistor names and signal names. Active-low signal names are identified by the # character.

The following example is the mnemonic for the VFC Sense strap signal:

VFC\_SENSE#

The example below refers to the Product Type Code field that occupies bit positions 0 through 15 within the 16-bit vendor ID register in PCI configuration space:

SUBSYS\_VEN\_ID[15:0]

#### 1.2.2 Numeric Representation

Hexadecimal numbers are appended with "h" (Intel assembly-style notation) whenever there is a risk of ambiguity. Other numbers are assumed to be in decimal.

Several signals of identical function are sometimes described by a single expression in which the part of the signal name that differs is shown in parenthesis (). For example, the four Select signals — SEL#0, SEL#1, SEL#2, and SEL#3 — are represented by the single expression SEL#(0:3).

# 1.2.3 Acronyms

Standard acronyms used in the literature are presumed known and will not be explained. When in doubt, the reader can refer to the following table for a quick check. Less frequently used or ATI-specific acronyms will have the full definition alongside in parenthesis when they appear the first time in the document.

**Table 1-1 Standard Acronyms**

| Acronym          | Full Expression                                                                                                                    |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AGP              | Accelerated Graphics Port                                                                                                          |  |  |  |

| ALU              | Arithmetic Logic Unit                                                                                                              |  |  |  |

| AMC              | ATI Multimedia Channel                                                                                                             |  |  |  |

| BGA              | Ball Grid Array                                                                                                                    |  |  |  |

| CRC              | Cyclic redundancy check                                                                                                            |  |  |  |

| DVS              | Digital Video System                                                                                                               |  |  |  |

| EPROM            | Erasable Programmable Read Only Memory                                                                                             |  |  |  |

| FIFO             | First In, First Out                                                                                                                |  |  |  |

| I <sup>2</sup> C | Bus Protocol (Philips Specification)                                                                                               |  |  |  |

| MDP              | MPEG Data Port                                                                                                                     |  |  |  |

| MPP              | Multimedia Peripheral Port                                                                                                         |  |  |  |

| PEROM            | Flash Programmable and Erasable Read Only Memory                                                                                   |  |  |  |

| PQFP             | Plastic Quad Flat Pack                                                                                                             |  |  |  |

| UV               | Chrominance (also CrCb). Corresponds to the color of an image pixel.                                                               |  |  |  |

| VBI              | Vertical Blank Interval                                                                                                            |  |  |  |

| VFC              | VGA Feature Connector                                                                                                              |  |  |  |

| YUV              | The method of video signal color encoding. Includes luminance (Y, black and white component) and chrominance (UV, color component) |  |  |  |

The 3D RAGE PRO Graphics Accelerator sets the standard on 2D/3D and video performance for the new generation of AGP graphics accelerators. Designed to take full advantage of Intel's AGP (Accelerated Graphics Port) high-speed interface, 3D RAGE PRO features 100MHz SGRAM or WRAM memory support, floating-point set-up engine, 4K texture cache, a host of unique 3D features, 230MHz DAC and enhanced MPEG-2 motion compensation. The 3D RAGE PRO is the industry's first accelerator to unleash the full potential of AGP for advanced processors such as the Pentium II.

# 2.1 Unique Features

#### 2.1.1 AGP 2X mode

Unlike competing solutions, which use AGP 1X mode only, the DVD-enabled 3D RAGE PRO AGP 2X, with three times the 3D performance of the previous generation chip, is the first demonstrated AGP accelerator to support the AGP 2X (133MHz) mode. The AGP 2X mode offers a peak bandwidth in excess of 500 MB/s, which is twice the throughput of the AGP 1X (66MHz) mode. The PCI graphics devices are limited to a 33MB/s bandwidth which must be shared with other PCI devices. The 3D RAGE PRO also supports AGP's pipeline and sideband protocols. These significantly improve the sustained bandwidth that is critical to the enhanced 3D and video performance.

# 2.1.2 Floating-Point Set-up Engine

The 3D RAGE PRO integrates a floating-point set-up engine capable of processing up to 1.2 million triangles per second. By off-loading the set-up function from the CPU, allowing it to focus on 3D geometry and lighting transformations, the 3D RAGE PRO dramatically improves the performance of the entire 3D pipeline.

Compared with competing first generation set-up engines which only accept fixed-point parameters, requiring the CPU to perform float-to-fixed conversions that can take up to 100 CPU clocks, ATI's floating point architecture opens the door to the highest level of 3D performance.

#### 2.1.3 100 MHz SGRAM

Frame buffer bandwidth is another important factor affecting 3D and 2D graphics performance. 3D RAGE PRO's 64-bit, 100MHz SGRAM interface delivers 800 MB/s of low-latency frame buffer bandwidth, the highest achieved by any mainstream graphics controller.

It is the ideal complement to the high bandwidth AGP 2X mode interface. By contrast, single-channel, non-concurrent RAMBUS designs used by others are limited to 600 MB/s of high-latency bandwidth.

ATI can provide design assistance, including IBIS models, to allow OEMs to design 100MHz memory upgrades on motherboards using the new industry standard SGRAM SO-DIMMs.

#### 2.1.4 DVD and Video Support

DVD and video features include enhanced motion compensation acceleration and a 4-tap horizontal and 2-tap vertical high quality DVD video scaler, providing smooth images without the "jaggies" (jagged edges) common to today's video products. The scaler provides true color video display, independent of the graphics mode used.

3D RAGE PRO also features a de-interlacing filter, video on graphics overlay, multi-stream video, color-space conversion, scatter-gather bus-master, planar YUV mode, ATI Multimedia Channel (AMC) video input port and support for high quality NTSC and PAL TV-out with the ATI ImpacTV chip.

By off-loading the motion compensation step from an MMX processor, 3D RAGE PRO improves software DVD/MPEG-2 frame rate by 20 to 30%. 3D RAGE PRO provides full motion MPEG-2 playback on Pentium II processors, without the need for DVD hardware.

#### 2.2 Feature List

#### 2.2.1 General Features

- High integration results in a low cost, small footprint graphics subsystem, ideal for motherboard designs.

- PCI version 2.1 with full bus mastering and scatter/gather support.

- Bi-endian support for compliance on a variety of processor platforms.

- Fast response to host commands:

- 128-level command FIFO

- 32-bit wide memory-mapped registers

- Programmable flat or paged memory model with linear frame buffer access

- Triple 8-bit palette DAC with gamma correction for true WYSIWYG color. Pixel rates up to 230MHz.

- Supports DRAM, EDO DRAM, SDRAM and SGRAM at up to 100MHz memory

- clock providing bandwidths up to 800MB/sec across a 64-bit interface.

- Supports WRAM and 128-bit external DAC for ultra-high end configurations.

- Flexible graphics memory configurations: 2MB up to 8MB EDO/SDRAM/SGRAM,

4MB to 16MB WRAM.

- Memory upgrade via industry standard SGRAM SO-DIMM, for reduced board area and higher memory speeds.

- DDC1 and DDC2B+ for Plug-and-Play monitors.

- Power management with full VESA DPMS and EPA Energy Star compliance.

- Integrated hardware diagnostic tests performed automatically upon initialization.

- High quality components through built-in SCAN, Iddq, CRC and chip diagnostics.

- Single chip solution in 0.35μm, 3.3V CMOS technology, with multiple package options.

- Comprehensive HDKs, SDKs and utilities augmented by full engineering support.

- Complete local language supports (contact ATI for current list).

#### 2.2.2 2D Acceleration

- Hardware acceleration of Bitblt, Line Draw, Polygon / Rectangle Fill, Bit Masking, Monochrome Expansion, Panning/Scrolling, Scissoring, full ROP support and h/w cursor (up to 64x64x2).

- Game acceleration (including support for Microsoft's DirectDraw): Double Buffering, Virtual Sprites, Transparent Blit, Masked Blit and Context Chaining.

- Acceleration in 8/16/24/32 bpp modes. Packed pixel support (24bpp) enables true color in 1MB configurations.

#### 2.2.3 3D Acceleration

- Integrated 1 million triangle/s set-up engine reduces CPU and bus bandwidth requirements and dramatically improves performance of small 3D primitives

- 4K on-chip texture cache dramatically improves large triangle performance.

- Complete 3D primitive support: points, lines, triangles, lists, strips and quadrilaterals and BLTs with Z compare.

- Comprehensive enhanced 3D feature set:

- Full screen or window double buffering for smooth animation

- Hidden surface removal using 16-bit Z-buffering

- Edge anti-aliasing

- Sub-pixel and sub-texel accuracy

- Gouraud and specular shaded polygons

- Perspectively correct mip-mapped texturing with chroma-key support

- Support for single pass bi- and tri-linear texture filtering, vastly improving bi- and trilinear performance

- Full support for Direct3D texture lighting

- Texture compositing

- Special effects such as complete alpha blending, fog, video textures, texture lighting, reflections, shadows, spotlights, LOD biasing and texture morphing

- Dithering support in 16bpp for near 24bpp quality in less memory

- Texture compression of up to 8:1 using vector quantization

- Extensive 3D mode support:

- Draw in RGBA32, RGBA16, and RGB16

- Texture map modes: RGBA32, RGBA16, RGB16, RGB8, ARGB4444, YUV444

- Compressed texture modes: YUV422, CLUT4 (CI4), CLUT8 (CI8), VQ

#### 2.2.4 Motion Video Acceleration

- Smooth video scaling and enhanced YUV to RGB color space conversion for full-screen / full-speed video playback.

- Front and back end scalers support multi-stream video for video conferencing and other applications.

- Filtered horizontal/vertical, up/down scaling enhances playback quality.

- Enhanced line buffer allows vertical filtering of native MPEG-2 size (720x480) images.

- DVD / MPEG-2 decode assist provides dramatically improved frame rate without incurring cost of dedicated hardware.

- Special filter circuitry eliminates video artifacts caused by displaying interlaced video on non-interlaced displays.

- Bi-directional bus mastering engine with planar YUV to packed format converter for superior MPEG-2 and video conferencing.

- Hardware mirroring for flipping video images in video conferencing systems.

- Supports graphics and video keying for effective overlay of video and graphics.

- YUV to RGB color space converter with support for both packed and planar YUV:

- YUV422, YUV410, YUV420

- RGB32, RGB16/15, RGB8, Mono

# 2.2.5 AMC Operation

- 16-bit, bi-directional video port allows direct connection to popular video upgrades such as:

- Video capture / video conferencing

- Hardware MPEG-2 / DVD player

- TV Tuner with Intercast support

- Interface to ATI's ImpacTV chip

# 2.3 Product Family

#### 2.3.1 Chip Packaging Options

The 3D RAGE PRO is available in five AGP and PCI packaging options with different levels of AGP support, giving manufacturers maximum flexibility to differentiate products and upgrade existing design. The table below indicates the several configurations in which the 3D RAGE PRO is available.

| Table 2-1 3 | D RAGE PRO | packaging and | l identification | codes |

|-------------|------------|---------------|------------------|-------|

|-------------|------------|---------------|------------------|-------|

| Chip ID | Description                       |

|---------|-----------------------------------|

| GB      | BGA package, AGP: both 1X and 2X  |

| GD      | BGA package, AGP: 1X support only |

| GI      | BGA package, PCI 33MHz only       |

| GP      | PQFP package, PCI 33MHz           |

#### **3D RAGE PRO AGP 2X**

- Incorporates AGP 2X mode (133MHz) and 230MHz DAC support

- Triple 8-bit palette DAC supporting pixel rates up to 230MHz

- Available in 256-pin BGA for optimal electrical characteristics in the demanding AGP environment.

#### 3D RAGE PRO AGP 1X

- Incorporates AGP 1X (66MHz) support with pipelining and sideband address support.

- Triple 8-bit palette DAC supporting pixel rates up to 200MHz

- Available in 256-pin BGA package. This is a pin-compatible alternative to 3D RAGE PRO AGP 2X for cost-sensitive implementations.

#### 3D RAGE PRO PCI

• Incorporates 33MHz PCI revision 2.1 support.

Available in 208-pin PQFP package and pin-compatible with 3D RAGE II /II+. An ideal upgrade to extend the life of existing motherboards, and the most economical solution for non-AGP systems, the PCI version incorporates the same performance enhancements and new features found in the AGP 3D RAGE PRO versions.

#### 2.3.2 Add-on Cards

ATI Multimedia Channel (AMC) add-on cards for 3D RAGE PRO include ATI's existing line of TV tuners, video capture and hardware DVD/MPEG-2.

# 2.4 Software Support

Table 2-2 Workstation Class / Arcade Level 3D Accelerator

| Software Support                 | DOS               | Win 3.x | Win 95 | Win NT | Mac OS | OS/2                                    |

|----------------------------------|-------------------|---------|--------|--------|--------|-----------------------------------------|

| 2D Software Support <sup>1</sup> |                   | 1       |        |        |        |                                         |

| Accelerated driver support       | VESA <sup>2</sup> | *       | *      | *      | *      | *                                       |

| AutoCAD / MicroStation           |                   |         |        |        |        |                                         |

| Video Software Support           |                   |         |        |        |        |                                         |

| Microsoft DirectDraw             |                   | -       | *      |        |        |                                         |

| Microsoft ActiveMovie            |                   |         | *      |        |        |                                         |

| MPEG-1 software playback         | *                 | *       | *      |        |        |                                         |

| MPEG-2 software playback         |                   |         | *      |        |        |                                         |

| 3D Software Support              |                   | ·       |        |        |        |                                         |

| Microsoft Direct3D               |                   |         | *      |        | ·      |                                         |

| QuickDraw 3D RAVE                |                   |         | *      | *      | *      | *************************************** |

| OpenGL <sup>3</sup>              |                   |         | *      | *      |        |                                         |

| Heidi                            | 1                 |         |        | *      |        |                                         |

| ATI 3D CIF <sup>4</sup>          |                   |         | *      |        |        |                                         |

<sup>1 -</sup> Additional 3rd parties (including SCO Unix and UNIXWARE);

<sup>2 -</sup> Direct BIOS support;

- 3 Includes NT 3.51ICD and NT4.0 MCD;

- 4 ATI's 3D API for the 3D RAGE family

#### 2.5 Market Orientation

#### 2.5.1 Corporate PC Market

ATI designed the 3D RAGE PRO to be the ideal corporate PC accelerator, with the performance, reliability, and software support that corporate users demand today along with the 3D features and performance needed to use the upcoming wave of corporate 3D applications.

3D RAGE PRO is available with an integrated 230MHz DAC that supports 1600x1200 resolution at the 85Hz refresh rate specified by the European market. Industry-leading 2D performance is provided by 100MHz SGRAM, faster 2D engine speed, a deeper command FIFO, AGP 2X mode and optimized drivers.

For PC workstations, the 3D RAGE PRO can be configured with WRAM memory and an external 250MHz DAC that will provide unmatched 2D and 3D performance at high resolutions and color depths. 3D RAGE PRO is the first mainstream part to incorporate edge anti-aliasing, deemed a necessity by CAD users.

Drivers are available for all corporate operating systems and API's (see section 2.4), including Windows NT 4.0/5.0, Windows 95, Memphis, OS/2, Mac OS, DirectX, Open GL, Heidi and QuickDraw3D. This allows support for 3D applications such as SGI's Cosmo Player VRML 2.0 browser, which will be bundled with ATI products.

#### 2.5.2 Consumer PC Market

With games in mind, ATI has enhanced the 3D performance of the 3D RAGE PRO by a factor of three over the previous generation chip. In addition, the 3D RAGE PRO incorporates advanced 3D features to allow greater realism. These include texture compositing, single pass trilinear filtering, specular highlights, video textures and VQ (vector quantization) texture decompression.

In AGP 2X mode, fast direct access to large amounts of main memory allows for large textures, which result in much greater graphical detail. The 4KB on-chip texture cache reduces the memory bandwidth requirements and latency, providing benefits in either AGP or PCI modes.

With a rendering engine capable of 1.2 million triangles/second and a peak fill rates of 75 million textured pixels/second, the 3D RAGE PRO surpasses even high-end 3D game add-in boards on the market today.

This page intentionally left blank.

# Chapter 3 Functional Description

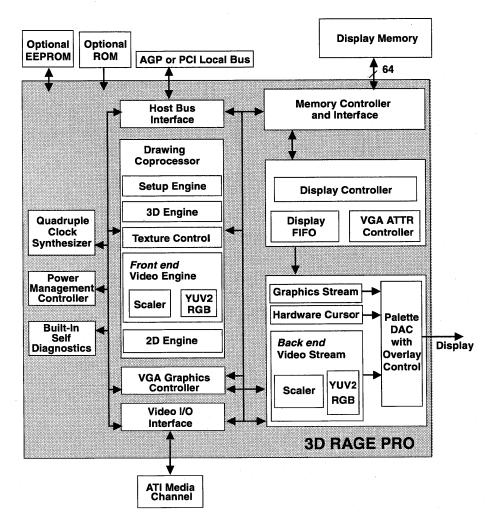

The 3D RAGE PRO controller comprises several major subsystems and interfaces as shown in the figure below. This chapter describes them briefly from a functional point of view.

Figure 3-1. 3D RAGE PRO Functional Block Diagram

# 3.1 3D Graphics Coprocessor

The 3D graphics coprocessor offers a number of orthogonal pixel processing features associated with the rendering of 3D images. These coprocessor functions were chosen to accelerate features of both Microsoft's D3D and Apple's QuickDraw 3D RAVE interfaces. Drivers will be available for all major operating systems and APIs (see Section 2.5).

The 3D RAGE PRO graphics processor includes a triangle setup engine, which needs only color, alpha, Z, U and V information at vertices of triangles to successfully draw Gouraud shaded, or perspectively correct texture mapped triangles. The setup engine significantly reduces the CPUs load in 3D graphics applications, giving applications more CPU time to perform non-setup related tasks.

Pixels to be displayed can be further modified by alpha blending with pixels in the destination, by fogging pixels with a fog color, and in the case of texture mapping, by lighting them. Depth buffering is achieved by associating a 16-bit Z value with each pixel. The Z, alpha, and fog color for each new pixel is supplied from interpolators within the 3D coprocessor. In case of texture mapping, the alpha factor may even be stored in the texture map on a pixel-by-pixel basis.

Pixels in the 3D coprocessor are always operated on as 24-bit entities (8 bits each of Red, Green, and Blue). Other pixel sizes, i.e., 8-bit and 16-bit, are dithered by the 3D graphics subsystem to output at the desired pixel size.

The 3D coprocessor contains a powerful texture mapping engine. This engine takes a series of precomputed maps (mip maps) and selects texels from these maps in a way that allows them to look perspectively correct. Texels can be filtered in a number of ways, and then lit (lightened or darkened). Once the texel is formed by filtering and lighting, any of the pixel processing modes mentioned previously can be applied to the texel.

A newly added 4K texture cache greatly reduces the memory bandwidth needed to support texture mapping.

With AGP support, texture maps can be stored in system memory and pulled into the local texture cache as needed. This rids the system of the need to add significant amount of local frame buffer memory in order to support multiple detailed texture maps, and allows applications to support a richer and more realistic environment.

# 3.2 2D Engine

The is a fixed-function subunit that runs concurrently to the host processor. It is dedicated to draw operations which include rectangle fill, line draw, polygon boundary lines, and polygon fill. A sophisticated pixel data path allows monochrome-to-two-color expansion,

solid color fill, screen-to-screen bitblts, fixed pattern fill, general pattern fill, general patterns with rotation, and host-to-screen data transfers. Flexible bitblt trajectories allow hyper-efficient off-screen memory management, effectively increasing bitmap and font cache sizes and improving performance.

Other features include GUI engine quick setup which off-loads draw engine setup from the host CPU. A 16-function ALU and a four-function source/destination color comparator allow source and destination to be combined in a multitude of ways, useful for operations such as image overlaying or transparent blits. Bit masking and scissoring can protect memory regions from being written.

All internal draw engine data paths are 64-bit wide. Full drawing features are available in 8, 15, 16, 24, and 32 bits-per-pixel (bpp) modes.

All draw engine registers are 32-bit wide. A 128x32 command FIFO improves throughput over the expansion bus. Additional 64 entries are dedicated to busmastering16x64 source and destination FIFOs improving memory bandwidth throughput.

# 3.3 Video Coprocessor

The video coprocessor has an optimized data path designed for scaling, filtering, and color space conversion. Dual 768-pixel line buffer has been integrated into this block to provide superior vertical scaling and interpolation. Graphics and video keying capabilities and a window controller allow for overlaying of the graphics and video data streams. This enables simultaneous display of 24bpp video and 8/16/24/32bpp graphics.

# 3.4 Host Bus Interface

The Host Bus Interface supports both AGP and PCI 2.1 standards. Support for AGP includes both sideband and mixed address modes. Texture map data for 3D objects can be obtained directly from system memory. Similarly the AGP can be used to accumulate MPEG-2 playback.

With PCI 2.1, functions such as bus control, data flow control, address/data signal generation, signal timings, and address decoding are supported. Data flow control is enhanced by a 6x64-bit write-through FIFO available in both VGA and direct memory modes.

Bus mastering functions between (1) system memory and frame buffer, (2) system memory and MPP, and (3) system memory and GUI engine, allow all data transfer operations to be off-loaded from the host processor onto the motherboard chip set.

# 3.5 Memory Controller and Interface

The memory controller subsystem arbitrates requests from the direct memory interface, the VGA graphics controller, the drawing coprocessor, the display controller, the video scaler, and the hardware cursor. Requests are serviced in a manner that ensures display integrity and maximum CPU/coprocessor drawing performance.

A dedicated DRAM frame buffer can be 2MB or 4MB in size using Fast Page or EDO DRAM. A dedicated synchronous DRAM frame buffer can be 2MB, 4MB, or 8MB in size using SDRAM or SGRAM. A dedicated WRAM frame buffer can be 8MB or 16MB in size.

**Table 3-1 Memory Controller**

| Memory Type       | 2MB       | 4MB       | 8MB       | 16MB    |

|-------------------|-----------|-----------|-----------|---------|

|                   | -         | -         | -         | -       |

| DRAM,<br>EDO DRAM | 256Kx8    | -         | -         | -       |

| EDO DRAIVI        | 256Kx16   | 256Kx16   | -         | -       |

| SDRAM,<br>SGRAM   | 128Kx16x2 | 128Kx16x2 | · -       | -       |

|                   | 128Kx32x2 | 128Kx32x2 | -         | -       |

|                   | 256Kx32x2 | 256Kx32x2 | 256Kx32x2 | · -     |

| WRAM              | -         | 256Kx32   | 256Kx32   | 256Kx32 |

# 3.6 Extended VGA Graphics Controller

The VGA portion of the graphics controller is fully register compatible with the VGA standard and is BIOS-compatible with VESA super VGA drivers.

# 3.7 CRT Controller (CRTC)

The CRTC subsystem has additional enhancements such as support for overscan, video memory sizes up to 8MB, and screen resolutions up to 1600x1200 non-interlaced.

# 3.8 Display Controller

The display controller subsystem consists of four subunits as follows:

- Display FIFO to manage the memory interface for displayed pixel data.

- Enhanced attribute controller for VGA.

- The display controller.

- 128 bit external RAMDAC supported with WRAM.

This display controller subsystem supports VGA graphics modes up to 1600x1200 (85Hz), VGA text modes up to 132-column on a PS/2 monitor, and accelerator display modes up to 1600x1200 (85Hz).

#### 3.9 Palette DAC

The internal palette DAC subsystem consists of a triple 256x8 SRAM palette and a triple 8-bit DAC. It supports the following features:

- Pixel clock rates up to 230MHz for resolutions up to 1600x1200.

- Refresh rates up to 200Hz.

- Built-in DAC reference generation.

- Monitor detection.

- Direct 24-bit color.

- Separate or composite horizontal and vertical Sync signals.

- Optimized slew rate control for the RGB analog output for low EMI emission.

# 3.10 Quadruple Clock Synthesizer

The internal clock synthesizer consists of four independent phase locked loops (PLL) capable of synthesizing any frequency up to 230MHz. All PLLs have been optimized for low jitter graphics applications.

- The first PLL generates clocks for the CRTC, display controller, and palette DAC.

This PLL can be reprogrammed by the BIOS for each display mode.

- The second PLL generates the clock for the drawing coprocessor.

- The third PLL is used to generate the 66 MHz and 133 MHz internal clock synchronous AGP bus operations.

- The fourth PLL generates the clock for the memory controller.

#### 3.11 Hardware Cursor

The hardware cursor logic supports a 64x64x2 memory-mapped cursor that is also XGA function compatible. The hardware cursor may be used in any display mode supported by this controller. Transparent, complement, and two solid colors are available.

# 3.12 ATI Multimedia Channel (AMC)

The AMC represents a collection of hardware and software components designed to facilitate the use of ATI products for multimedia applications. It consists of a non-chip audio bus, and three ports into the graphics controller - the DVS port for video input into the graphics controller, the MPP port for video input and output from the graphics controller, and the I<sup>2</sup>C port for controlling attached devices. It is backward compatible with the VFC interface.

The Multimedia Peripheral Port (MPP) Mode supported by AMC allows interface with external I/O devices. For example, compressed data can be transferred by means of MPP from the host (CPU) to the MPEG-2 decoder for DVD applications.

Display data can also be streamed out from *3D RAGE PRO* to the device (e.g. TV-Out chip). For such applications, an ATI external encoder, such as ImpacTV, can be attached to generate NTSC/PAL video for a TV-type display.

The Digital Video Stream (DVS) port accepts industry standard video formats, and allows easy attachment of video decoders and hardware MPEG-2 decoders. The DVS port provides for decoded video data to stream back to the graphics controller.

The I<sup>2</sup>C is an industry standard serial bus that allows control and programming of a wide range of peripherals. The 3D RAGE PRO incorporates an I<sup>2</sup>C interface to allow programming of peripherals such as video decoders, TV tuners, teletext decoders, and volume control.

The VGA Feature Connector (VFC) is VESA compatible. The VFC-compatible peripherals can be attached directly to the AMC/VFC port.

# Chapter 4 Interfaces

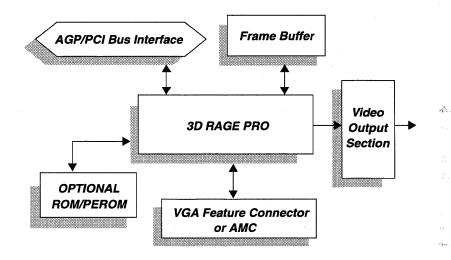

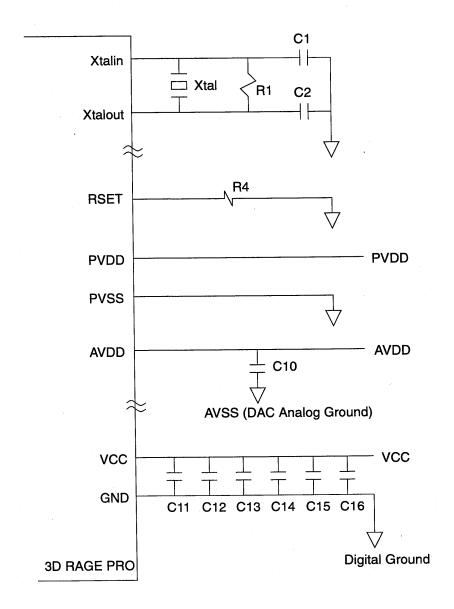

The following block diagram depicts the major interfaces required in a typical design based on the 3D RAGE PRO. These interface blocks are further described in later sections of this chapter. Please note that the interface diagrams are generic. You are invited to refer to the reference schematics for this chip for the latest information.

Figure 4-1. Controller Interface

#### 4.1 AGP/PCI Bus Interface

The 3D RAGE PRO controller supports the Accelerated Graphics Port (both AGP 66MHz and 133MHz). Addressing modes include sideband address support. This AGP enabled controller can access large texture maps, stored in system memory, directly. Applications that make use of large numbers of 3D objects can reduce the amount of memory required in the frame buffer.

Together with PCI Version 2.1, the *3D RAGE PRO* controller acts as a target device, supporting 32-bit memory and I/O operations and byte lane swapping. With full 32-bit address decoding available in PCI, it can map the Direct Memory Interface to 4GB of memory space on a 16MB boundary.

The controller achieves zero wait-state memory read/write burst cycles with burst access. It also supports Block I/O decoding and DAC palette snooping.

Bus mastering allows data transfer operations without CPU intervention. In bus master mode, the controller will take control of the PCI bus by driving the address and control signals.

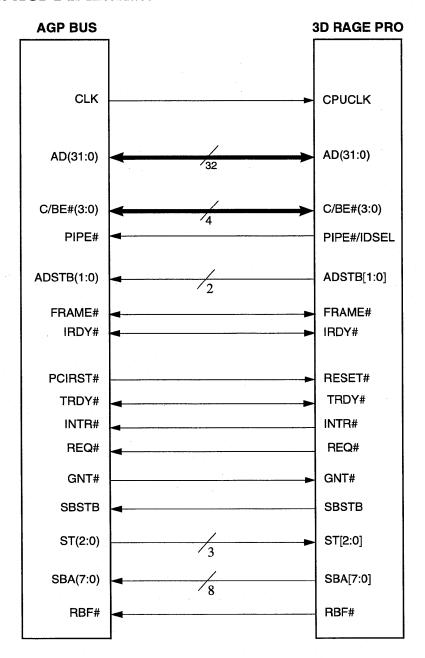

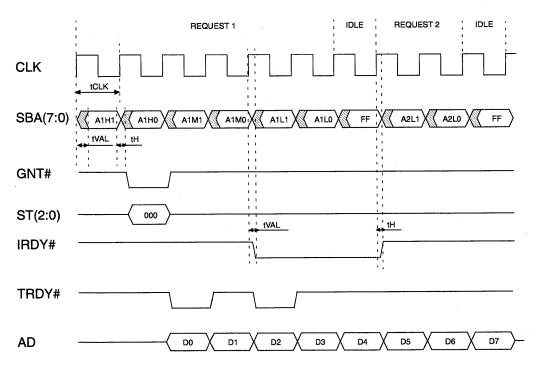

AGP Bus Configuration is shown in Figure 4-2.

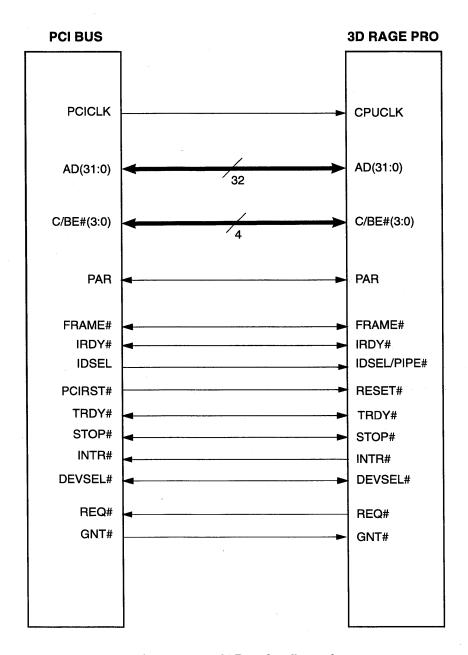

PCI Bus Configuration is shown in Figure 4-3.

#### 4.1.1 The AGP Bus Interface

Figure 4-2. AGP Bus Configuration

#### 4.1.2 The PCI Bus Interface

Figure 4-3. PCI Bus Configuration

# **4.2** Memory Interfaces

The memory interface of this controller supports the following memory devices:

**SDRAM, SGRAM** and **WRAM** — 128x16x2, 128x32x2, 256x32x2 and 512x32x2.

**DRAM** and **EDO DRAM** — 256x4, 256x8, and 256x16.

Memory configurations range from 2MB to 8MB (see table below). This interface supports only a full 64-bit memory path.

This interface supports mixing of memory component sizes — 256x4, 256x8, and 256x16 — within one design. However it does not support mixing of memory types, e.g., the mixing of DRAM and EDO DRAM.

The table below lists the supported memory configurations, and the number of memory parts required:

| Table 4-1 Memory | Interface Support |

|------------------|-------------------|

|------------------|-------------------|

| Memory Size | 256x8<br>(2Mb)  | 256x16/<br>128x16x2<br>(4Mb) | 128x32x2<br>(8Mb) | 256x32x2      |

|-------------|-----------------|------------------------------|-------------------|---------------|

| 2MB         | 8               | 4                            | 2                 | Not supported |

| 4MB         | Not recommended | 8                            | 4                 | 2             |

| 6MB         | -               | Not recommended              | 6                 | -             |

| 8MB         | -               | Not recommended              | 8                 | 4             |

Supported memory interface types include "Dual CAS" DRAM, EDO DRAM, WRAM (symmetrical types), SDRAM, and SGRAM devices. Strap resistors are installed on pins MD[48:50] to identify which of these memory types are in use. See Chapter 5, "Controller Configuration", for details on strap resistors usage. This scheme allows your design to support multiple memory implementations using one BIOS.

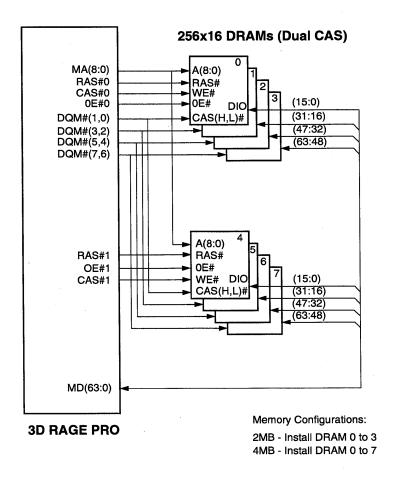

Figure 4-4 shows a 256x16 Dual CAS memory implementation.

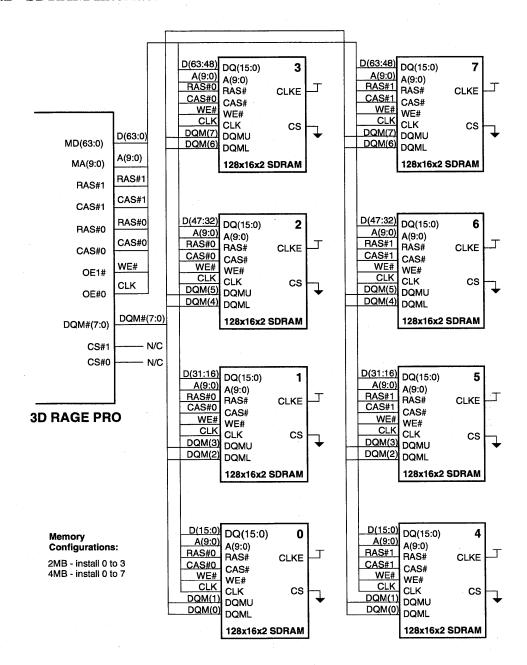

An SDRAM memory implementation example using 128x16x2 SDRAM devices is shown in *Figure 4-5*.

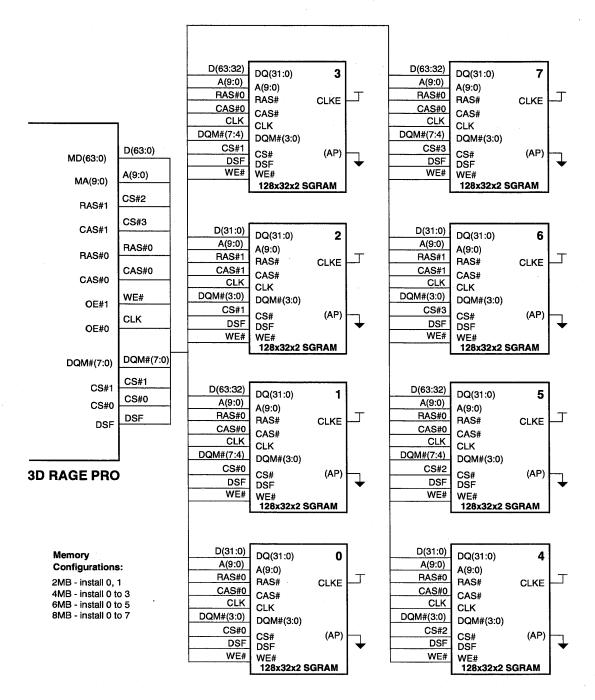

An SGRAM memory implementation example using 128x32x2 SGRAM devices is shown in *Figure 4-6*.

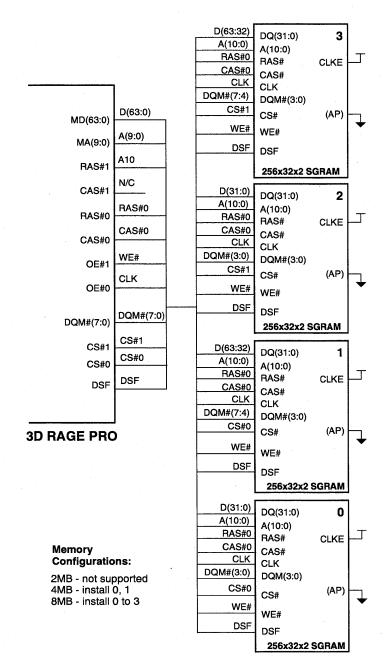

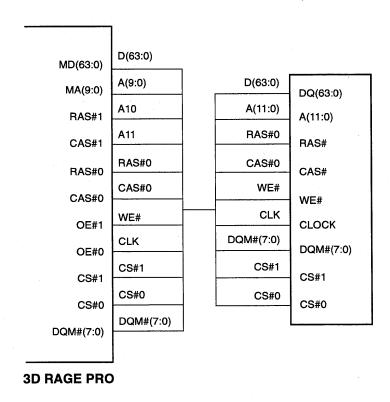

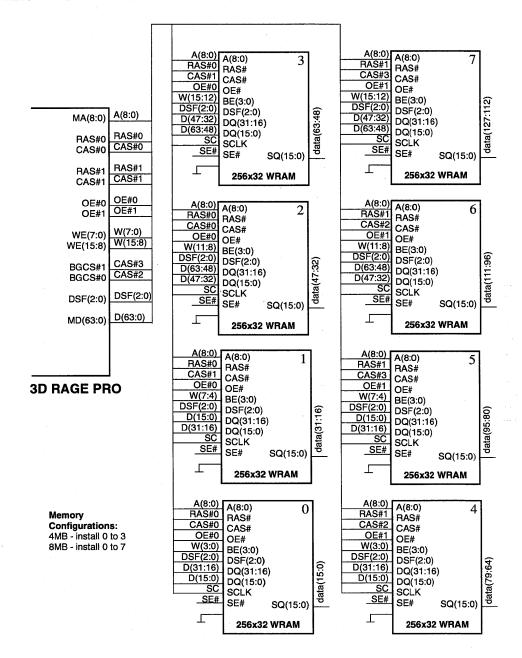

An SGRAM example with 256x32x2 is implemented on *Figure 4-7* SGRAM example using 512x32x2 SGRAM devices is shown in *Figure 4-8*.

Figure 4-9 shows an example of SO-DIMM Module Interface implementation.

Examples of WRAM memory implementation using 256x32 WRAM devices and external DAC interface for WRAM are shown in *Figure 4-10* and *Figure 4-11*.

#### 4.2.1 DRAM Interface

Figure 4-4. DRAM Implementation

#### 4.2.2 SDRAM Interface

Figure 4-5. SDRAM Implementation

### 4.2.3 SGRAM Interface with 128x32x2 (8 Mbit) SGRAMs

Figure 4-6. SGRAM Implementation (8 Mbit)

#### 4.2.4 SGRAM Interface with 256x32x2 (16 Mbit) SGRAMs

Figure 4-7. SGRAM Implementation (16 Mbit)

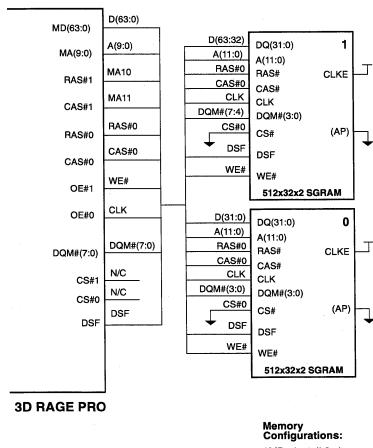

# 4.2.5 SGRAM Interface with 512x32x2 (32 Mbit) SGRAMs

8MB - install 0, 1

Figure 4-8. SGRAM Implementation (32 Mbit)

# **4.2.6 SO-DIMM Module Interface**

Figure 4-9. SO-DIMM Module Implementation

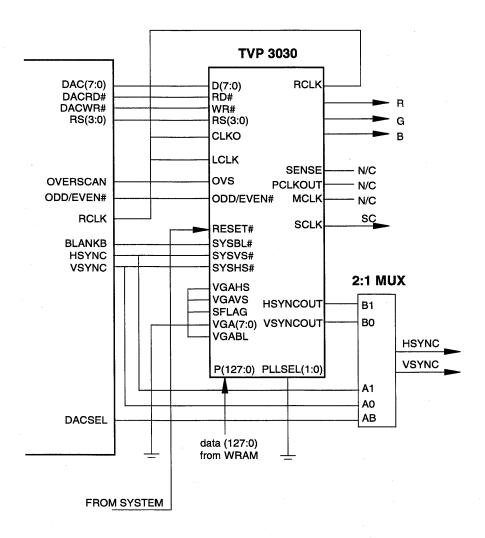

#### 4.2.7 External DAC Interface for WRAM

Figure 4-10. External DAC Implementation

#### 4.2.8 WRAM Interface

Figure 4-11. WRAM Implementation

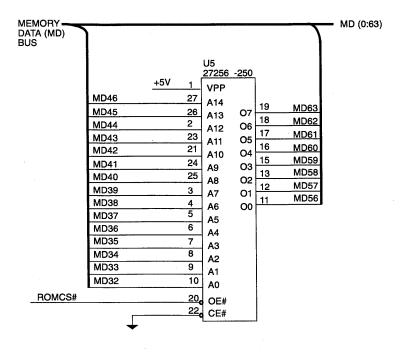

#### 4.2.9 EPROM Interface

The video BIOS may be stored in either a 32K or a 64K EPROM (27256/27512), or integrated into the system BIOS. ATI offers a BIOS kit which is used for BIOS customizing or integration of the video BIOS with the system BIOS (see *Figure 4-12*). This kit allows certain BIOS options to be created, for example:

- 32K or 36K non-paged (linear) BIOS, or

- 64K BIOS

- 128K BIOS

Please refer to the *mach64 BIOS Kit* (*BIO-G01000*) manual for additional information on the differences and trade-offs of the various options.

Figure 4-12. EPROM Interface

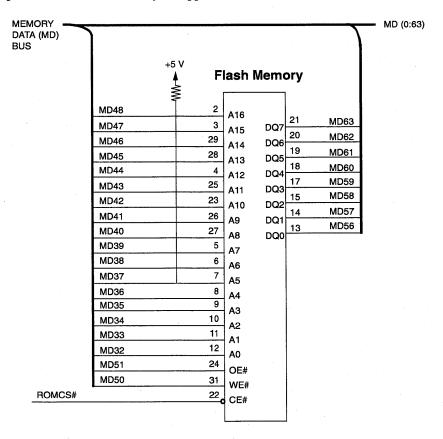

### 4.2.10 Flash Memory Interface

Up to 128K of flash memory is supported.

Figure 4-13. Flash Memory Interface

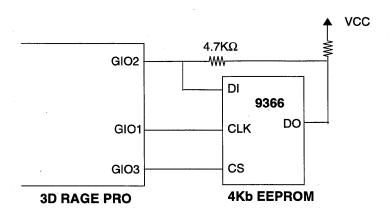

#### 4.3 EEPROM Interface

An optional EEPROM may be added for non-volatile storage of programmable graphics subsystem parameters. It is an alternative to the software-only method of storing timing parameters in a file on a hard drive. However, it is becoming more popular to store parameters in a file for cost reasons. All ATI drivers and utilities support both EEPROM and software-only implementations.

If an EEPROM is present (see Figure 4-14), it is re-loaded with user-defined power-on defaults and monitor parameters whenever modifications are made. Users can therefore customize display sizes and positions of various video modes, then store the settings in the EEPROM. When the user selects a customized video mode, the BIOS accesses the EEPROM instead of a monitor timing table of fixed parameters to support that mode. The EEPROM is not supported when the AMC is used for DVS or MPP functions.

Figure 4-14. EEPROM Interface

The EEPROM used is a 4Kb serial device (P/N 9366) organized as 256 registers of 16 bits. The interface to the EEPROM is straight forward. When the EECS signal from the controller enables access to the EEPROM, data is clocked into the DI port or clocked out from the DO port on the positive edge of the clock signal. The DO/DI, CLK, and CS ports on the EEPROM are connected to the GIO2, GIO1, and GIO3 controller pins respectively.

### 4.4 General Purpose I/O Control

Within the 3D RAGE PRO there are two general purpose I/O buses used to control optional interfaces — GIO[4:0] and GPIO[F:0]. The GIO is used to support the interfaces for EEPROM, monitor ID, and  $I^2C$  bus control. The GPIO is used for the ATI Multimedia Channel interface which is described on the following page (see Figure 4-15).

Table 4-2 GIO Bus

| GIO  | GIO Pin Name Description    |                             |  |  |

|------|-----------------------------|-----------------------------|--|--|

| GIO0 | GIO0 MONID1-DDC serial data |                             |  |  |

| GIO1 | GIO1                        | EECK                        |  |  |

| GIO2 | GIO2                        | EEDIO, I <sup>2</sup> L-SDA |  |  |

| GIO3 | GIO3                        | EECS                        |  |  |

| GIO4 | GIO4                        | MONID2-DDC serial clock     |  |  |

| GIOC | GIOC                        | MONID0                      |  |  |

Table 4-3 GPIO Bus

| GPIO  | Pin Name   | VFC<br>Mode | DVS Mode | MPP Mode |

|-------|------------|-------------|----------|----------|

| GPI00 | BLANK#     | BLANK#      | -        | SAD0     |

| GPIO1 | GIO6       | VFC H SYNC  | -        | SAD1     |

| GPIO2 | GIO5       | VFC V SYNC  |          | SAD2     |

| GPIO3 | GI07       | -           | -        | SAD3     |

| GPIO4 | GIO2       | -           | SDA      | SAD4     |

| GPIO5 | GIO9       | -           | -        | SAD5     |

| GPIO6 | GIO8       | -           | -        | SAD6     |

| GPIO7 | GIO3       | -           | -        | SAD7     |

| GPIO8 | EVIDEO     | EVIDEO      | -        | SIOR     |

| GPIO9 | ESYNC      | ESYNC       | -        | SIOW     |

| GPIOA | EDCLK      | EDCLK       | -        | SRDY/IRQ |

| GPIOB | GIO1       | -           | SCL      | -        |

|       | PDATA[7:0] | data[7:0]   | YUV[7:0] | -        |

| -     | DCLK       | DCLK        | CLK      | -        |

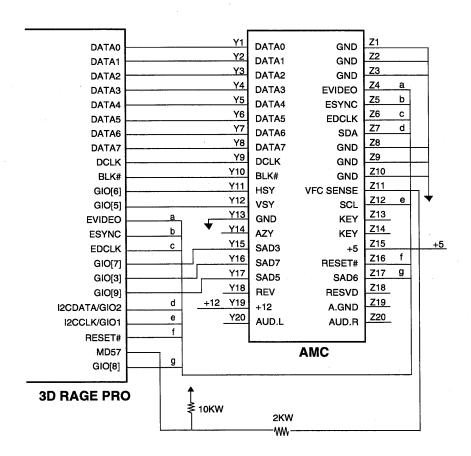

# 4.5 ATI Multimedia Channel 2.0 Interface (AMC)

Figure 4-15. ATI Multimedia Channel 2.0

The AMC is a 40-pin connector which can be added to a design based on the 3D RAGE PRO. The AMC can operate in various modes under different conditions. AMC pins have different functions under different modes, as follows:

VFC Mode — VESA VGA Feature Connector Mode supports various overlay peripherals such as MPEG cards. Output from the VFC may be enabled in all VGA modes as well as accelerated display modes with a display clock below 80MHz.

**DVS Mode** — Digital Video Stream Mode supports a direct connection to a Brooktree Bt829, Bt827, Bt819, Bt817, or Bt815, and Philips SAA7112 or SAA7111 video decoder. Connection to a Samsung KSO122 or ITT VPC32xx video decoder requires some additional logic.

Depending on the package type, PQFP or BGA, I<sup>2</sup>C pins on the AMC connector are driven by different sources.

In PQFP package, the I<sup>2</sup>C pins are driven by GIO1 and GIO2 directly, provided there is no TV-out chip on board. If there is TV-out chip, I2C\_CLK and I2C\_DAT from TV-out chip will be the drivers.

In the BGA package, there are specially dedicated pins — I2CCLK and I2CDATA — to drive the AMC I<sup>2</sup>C pins.

MPP Mode — Multimedia Peripheral Port Mode can stream data from the host memory out of this port. Timing and protocol can be programmed to support peripheral chips. By connecting this port to an external NTSC/PAL encoder, the display screen can be modulated to an NTSC/PAL TV signal.

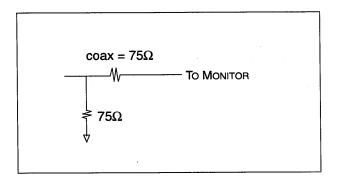

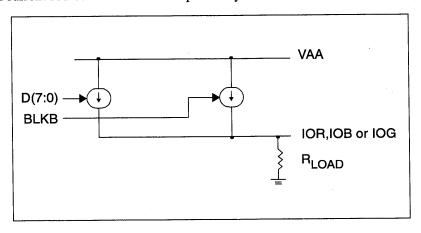

### 4.6 Analog Output Section

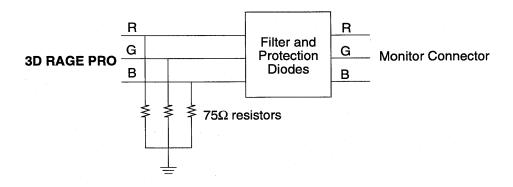

Each of the R, G, B lines on the board (see Figure 4-16) is to be loaded with a  $75\Omega$  resistor. Diodes can be used to protect the controller from any large transient voltages which may enter from the connector when the monitor is connected.

Bypass capacitors can also be placed on all lines in order to filter the output. The RGB lines may also have inductors (ferrites) placed in series. This may be required in order to comply with FCC Class B requirements for radio frequency emissions. The proper value is determined as a trade-off between filtering the signals for FCC requirements and video signal clarity.

Figure 4-16. Analog Output

This page intentionally left blank.

### 5.1 Strap Resistors Summary

External strap resistors may be used to configure various aspects of the 3D RAGE PRO graphics subsystem. Logic levels at the strap pins are sensed and latched into registers at the first PCI command. The 3D RAGE PRO contains internal pull-down resistors on strap pins to provide a default strap value of logic zero. By pulling the strap pin high via an external pull-up resistor, the strap value can be forced to logic one. In some cases, the registers which hold the strapped values are writable by video BIOS. The table below summarizes the strap pins on the controller. It is followed by a section which provides a detailed explanation of each strapping option.

Table 5-1 3D RAGE PRO Strap Resistors

| Signal<br>Name   | Strap Name | BIOS<br>Configurable | Description                                                            |

|------------------|------------|----------------------|------------------------------------------------------------------------|

| MD63             | reserved   | n/a                  | 0 = normal operation (default)<br>1 = reserved                         |

| MD62             | MD62 IDSEL |                      | 0 = connect IDSEL to AD16 (default)<br>1 = connect IDSEL to AD17       |

| MD61 ROM_REMAP   |            | No                   | 0 = No ROM Remap (default) 1 = If VGA disabled, remap top 8K to bottom |

| MD60             | reserved   | n/a                  | 0 = normal operation (default)<br>1 = reserved                         |

| MD59 ENINT#      |            | No                   | 0 = interrupt enable<br>1 = interrupt disable (default)                |

| MD58 VGA_DISABLE |            | No                   | 0 = VGA enable (default)<br>1 = VGA disable                            |

| MD57 VFC_SENSE#  |            | No                   | 0 = VFC mode<br>1 = AMC mode                                           |

| MD56             | reserved   | n/a                  | 0 = normal operation (default)<br>1 = reserved                         |

Table 5-1 3D RAGE PRO Strap Resistors (Continued)

| Signal<br>Name | Strap Name         | BIOS<br>Configurable | Description                                                                                                                                                                                                 |

|----------------|--------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD55           | TESTEN             | No                   | 0 = normal operation (default)<br>1 = test mode enabled                                                                                                                                                     |

| MD54           | reserved           | n/a                  | 0 = normal operation (default)<br>1 = reserved                                                                                                                                                              |

| MD53           | PREFETCH_EN        | No                   | 0 = disable prefetch<br>1 = enable prefetch                                                                                                                                                                 |

| MD52           | reserved           | n/a                  | 0 = normal operation (default)<br>1 = reserved                                                                                                                                                              |

| MD51           | ID_DISABLE         | No                   | 0 = normal operation (default)<br>1 = disable controller                                                                                                                                                    |

| MD(50:48)      | CFG_MEM_TYPE (2:0) | Yes                  | (xxxb) = Memory Type<br>(000) = reserved<br>(001) = WRAM<br>(010) = SGRAM<br>(011) = SDRAM<br>(100) = hyper page DRAM or EDO<br>(101) = EDO DRAM<br>(110) = FP DRAM<br>(111) = disable memory access        |

| MD47           | MEM_CS_EN          | No                   | 0 = tristate CS#0 and CS#1<br>1 = enable chip select (default)                                                                                                                                              |

| MD(46:44)      | X1CLKSKEW (2:0)    | No                   | AGP X1 clock phase adjustment with respect to X2.  (000) = 0.0 nsec (default)  (001) = 0.5 nsec  (010) = 1.0 nsec  (011) = 1.5 nsec  (100) = 2.0 nsec  (101) = 2.5 nsec  (110) = 3.0 nsec  (111) = 3.5 nsec |

Table 5-1 3D RAGE PRO Strap Resistors (Continued)

| Signal<br>Name | Strap Name                 | BIOS<br>Configurable | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD(43:41)      | AGPSKEW (2:0)              | No                   | AGP X1 clock feedback phase adjustment with respect to refclk (cpuclk) (000) = refclk 1 tap earlier than X1 (feedback). Default (001) = refclk 2 taps earlier than X1 (feedback) (010) = refclk 3 taps earlier than X1 (feedback) (011) = agp pll testmode, X2 is used as feedback (100) = feedback (X1) 3 taps earlier than refclk (101) = feedback (X1) 2 taps earlier than refclk (110) = feedback (X1) 1 tap earlier than refclk (111) = feedbacl (X1) and refclk are aligned each tap is worth 5 nsec roughly |

| MD40           | BUS_TYPE                   | No                   | 0 = normal bus type (default)<br>1 = alternated bus type                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MD(39:38)      | AGPVCOGAIN                 | No                   | VCO filter gain control (00) = (10) to VCO gain (default), no strap installed (01) = (11) to VCO gain (10) = (00) to VCO gain (11) = (01) to VCO gain                                                                                                                                                                                                                                                                                                                                                              |

| MD(37)         | ROMWRTEN                   | No                   | 0 = EPROM used for video BIOS -<br>PEROM (default)<br>1 = Flash Memory used for video BIOS                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MD(36:32)      | reserved - not used        | n/a                  | (xxxxxxb) = don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MD(31:29)      | SO-DIMM Strap<br>Resistors | No                   | (xxxb) = determined by SO-DIMM; see SO-DIMM specification                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MD(28:24)      | reserved - not used        | n/a                  | (xxxxxb) = don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MD(23:8)       | SUBSYS_VEN_ID(15:0)        | Yes                  | (xxxxh) = PCI subsystem vendor ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MD(7:0)        | SUBSYS_DEV_ID(7:0)         | Yes                  | (xxh) = LSB of PCI subsystem device ID register                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PCI33EN        | BUS_CLK_SELECT             | No                   | 0 = normal bus clock (default).<br>1 = alternate bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

**Note:** Strap resistors do not need to be installed on X1CLKSKEW and AGPSKEW (MD(46:44) and MD(43:41) respectively).

#### 5.2 Strap Resistor Description

MD62 IDSEL No 0 = connect IDSEL to AD16 (default)

1 = connect IDSEL to AD17

This strap has only significance for AGP devices since IDSEL is not a signal in the AGP interface. In an AGP implementation, the initialization device select signaling is provided on AD16 as per the AGP specification. The IDSEL strap allows the alternate AD17 signal to be selected. This alternate IDSEL provides a method of initializing a second graphic controller on the AGP bus in some future application. This strap is not used for the PCI variant of 3D RAGE PRO since a dedicated IDSEL signal is provided in the PCI bus interface.

MD61 ROM \_REMAP No 0 = No ROM Remap (default)

1 = If VGA disabled, remap top 8K to bottom

If VGA is disabled, this strap permits the remapping of the top 8K of the ROM to the bottom. This strap is only applicable to add-in cards which use a separate video BIOS ROM.

MD59 ENINT# No 0 = interrupt enable 1 = interrupt disable (default)

The interrupt strap permits enabling or disabling of interrupts. The 3D RAGE PRO has the capability of generating an interrupt request via the INTA# signal. Strapping MD59 to logic zero places the value 01h in the read-only Interrupt Pin register and enables interrupts. Strapping MD59 to logic one places the value 00h in the interrupt Pin register and disables interrupts. However, disabling the request for an interrupt resource does not prevent the graphics controller form asserting the INTA# signal if it is programmed to do so.

MD58 VGA\_DISABLE No 0 = VGA enable (default)

1 = VGA disable

The VGA disable strap provides a method of disabling the VGA portion of the graphics controller. This feature has possible application in systems containing more than one graphics controller.

MD57 VFC\_SENSE# No 0 = VFC mode1 = AMC mode

This strap signal is used for detecting the class of peripheral connected to the ATI Multimedia Connector, and configuring the AMC interface for either the AMC or VFC mode of operation. The 3D RAGE PRO reference design provides an external pull-up resistor on MD57 which forces AMC mode as the default. All VFC peripherals pull MD57 low through a 10K resistor to assert VFC\_SENSE#.

MD55 TESTEN No 0 = normal operation (default)

1 = test mode enabled

This strap is used to place the 3D RAGE PRO into test mode. Since test mode is only applicable for out-of-circuit testing, the provision for an external strap resistor is not required.

MD53 PREFETCH\_EN No 0 = disable prefetch 1 = enable prefetch

This strap permits the setting of bit 3 in the memory base address register to mark the range as prefetchable (see the description in the PCI specification in Chapter 6). A device can mark a range as prefetchable if there are no side effects on speculative reads, the device returns all bytes on reads regardless of the byte enables, and a host bridge can merge processor writes into this range without causing errors. The 3D RAGE PRO complies with these requirements.

MD51 ID\_ DISABLE No 0 = normal operation (default)

1 = disable controller

Allows the controller to be deactivated as far as the AGP or PCI bus is concerned. Strapping to disable the controller forces the internal logic for IDSEL to zero which prevents initialization of the device. The device will not respond to any PCI or AGP transactions, and will not drive signals on the AGP or PCI bus when disabled in this way.

|           |                    |     | (xxxb) = Memory Type           |

|-----------|--------------------|-----|--------------------------------|

|           |                    |     | (000) = reserved               |

|           |                    |     | (001) = WRAM                   |

|           |                    |     | (010) = SGRAM                  |

| MD(50:48) | CFG_MEM_TYPE (2:0) | Yes | (011) = SDRAM                  |

|           |                    |     | (100) = hyper page DRAM or EDO |

|           |                    |     | (101) = EDO DRAM               |

|           |                    |     | (110) = FP DRAM                |

|           |                    |     | (111) = disable memory access  |

|           |                    |     |                                |

The memory type straps provide the option of configuring the memory type through external hardware straps. Since most graphics subsystems use a single memory type, the memory type strap resistors are not used. Instead, the video BIOS is designed to load the required value for the memory type in the CFG\_MEM TYPE register during system initialization. Video BIOS binary and configuration files are available for the full range of memory types. Note that if external strapping is used, the CFG\_MEM\_TYPE filled in the CONFIG\_STAT0 register contains the inverse of the strapped values.

| MD47 MEM CS EN | MEM CS EN | No | 0 = tristate CS#0 and CS#1       |

|----------------|-----------|----|----------------------------------|

| WID47          | MEM_CS_EN | NO | 1 = enable chip select (default) |

The MEM\_CS\_EN strap provides a means of enabling or disabling the output buffers for CS#0 and CS#1. The default setting for MEM\_CS\_EN is enabled. An external pull-up resistor is required on this strap pin. This strapping enables memory bank selection via the CS#0 and CS#1 signals.

The tristate option is provided for backward compatibility of the 3D RAGE PRO with designs based on the original 3D RAGE I component.

| MD40 | BUS_TYPE | No | 0 = normal bus type (default) 1 = alternated bus type |

|------|----------|----|-------------------------------------------------------|

This strapping has meaning for all 3D RAGE PRO product variants. For devices in a 256 BGA package, the normal bus type is AGP and the alternate bus type is PCI. For devices in a 208 PQFP package, the normal bus type is PCI and the alternate bus type is AGP. For 256 BGA devices, selecting the alternate bus type (i.e., PCI) permits a WRAM-based graphics subsystem to be provided for PCI system. Only the 256 BGA device has a sufficient number of pins to support a WRAM-based frame buffer.

The 3D RAGE PRO G supports an AGP 66MHz interface in a 208-pin package without sideband addressing. In this configuration, the bus type is strapped as alternate.

| ilter gain control<br>(10) to VCO gain (default), no strap<br>ed<br>(11) to VCO gain<br>(00) to VCO gain<br>(01) to VCO gain |

|------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              |

These strap pins define the gain of the voltage controlled oscillator (VCO) in the PLL subsystem which generates the internal X1 and X2 AGP clock signals. The gain in the VCO circuit does not necessarily increases with increasing binary values of the strap setting. The default gain strapping of (00b) is the target implementation (i.e., no external resistors). However, the foot print for strap resistor on MD39 and MD38 should be provided on all new 3D RAGE PRO designs in order to permit future adjustment of the gain control, if required.

| MD(37) | ROMWRTEN | No 1 = | writable Flash memory not installed writable Flash Memory installed for |

|--------|----------|--------|-------------------------------------------------------------------------|

|        |          | Via    | eo BIOS                                                                 |

The ROMWRTEN strap is installed to indicate that writable Flash memory (PEROM) is being used for the video BIOS.

| MD/26:22\ | received net used | n/a | (vvvvvh) - don't care |  |

|-----------|-------------------|-----|-----------------------|--|

|           |                   |     |                       |  |

|           |                   |     |                       |  |

|           |                   |     |                       |  |

These strap pins are not used. They are reserved for possible future use.

MD(31:29) SO-DIMM STRAP No (xxxb) = determined by SO-DIMM; see SO-DIMM specification

These three bits are mandatory straps on all SO-DIMM modules and indicate the synchronous clock frequency or cycle time of the SO-DIMM. See the SO-DIMM specification for the definition of the strap resistors.

MD(28:24) reserved - not used n/a (xxxxxb) = don't care

These five strap pins are not used. They are reserved for possible future use.

MD(23:8) SUBSYS\_VEN\_ID(15:0) Yes (xxxxh) = PCI subsystem vendor ID

The subsystem vendor ID is a 16-bit register in PCI configuration space and used to uniquely identify subsystem manufactured by different vendors but with the same PCI or AGP device. The subsystem vendor ID for individual vendors is obtained from the PCI SIG.

The 3D RAGE PRO supports two methods for loading the subsystem vendor ID register. The first involves writing the register with a customizable value stored in the video BIOS. This is the preferred approach and the one which is generally used. The second method involves strapping the MD(28:8) signals to set the desired vendor ID register value.

**MD(7:0)** SUBSYS\_DEV\_ID(7:0) Yes (xxh) = LSB of PCI subsystem device ID register

The subsystem device ID is a 16-bit register in PCI configuration space and is used to identify a vendor's implementation of a particular subsystem. The subsystem device ID is supplied by the vendor. The 3D RAGE PRO supports two methods for loading the subsystem device ID register. The first involves writing the register with a customizable value stored in the video BIOS. This is the preferred approach and the one which is generally used. The second method involves strapping the MD(7:0) signals for the desired register value. The strapped values on MD(7:0) are mapped to the lower byte of the subsystem device ID register.

PCI33EN BUS\_CLK\_SELECT No 0 = normal bus clock (default) 1 = alternate bus clock

For AGP versions of 3D RAGE PRO, selecting normal bus clock sets the internal clock to the PLL. Selecting alternate bus clock, sets the internal clock to the external bus clock.

For PCI versions of 3D RAGE PRO, selecting normal sets the internal clock to the PCI bus clock. Selecting alternate sets the internal clock to the PLL generated clock. The normal setting is the default strapping for both AGP and PCI components. Since the alternate bus clock strapping may be useful during system checkout, initial 3D RAGE PRO designs should provide the foot print for this strap resistor.

### **6.1** Table Conventions

Controller pins have different operational characteristics. The assigned codes for each of these pin types are listed below. For electrical characteristics please refer to *Chapter 7* "Timing Specifications".

**Table 6-1 Conventions**

| Code Pin Type / Operational Characterist |                    |  |

|------------------------------------------|--------------------|--|

| ı                                        | Input pin          |  |

| 0                                        | Output pin         |  |

| 1/0                                      | Bi-Directional pin |  |

| M                                        | Multifunction pin  |  |

| Pwr                                      | Pwr Power pin      |  |

| Gnd Ground pin                           |                    |  |

| Α                                        | Analog pins        |  |

Pin numbers and signal names are sorted by interface and by pin number on the following pages.

All active-low signal names are identified by the succeeding # character throughout this document, e.g. BLANK#.