# $ProMotion^{(R)}-AT3D$

Integrated 3D graphics MultiMedia User Interface Accelerator

Technical manual

PRELIMINARY NDA Confidential

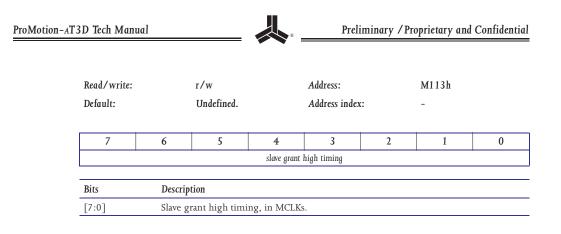

## ALLIANCE SEMICONDUCTOR

Document ID 11-50002 Rev. \*\*-06. Printed 6/97.

Copyright ©1997 Alliance Semiconductor; All rights reserved

Copyright © 1997 Alliance Semiconductor Corporation. All rights reserved. Document ID 11-50002 Rev. \*\*-06. Printed 6/97.

Alliance Semiconductor reserves the right to make changes to the data described herein at any time to supply the best product possible.

The company cannot assume responsibility for circuits shown or represent that they are free from patent infringement.

ProMotion® and the Alliance logo are registered trademarks of Alliance Semiconductor. ProMotion-AT3D<sup>TM</sup>, DitherFill<sup>TM</sup>, vWindow<sup>TM</sup>, BetterHalf<sup>TM</sup>, ProMotion-3210<sup>TM</sup>, ProMotion-6422<sup>TM</sup>, ProMotion-AT24<sup>TM</sup>, ProMotion-AT3D<sup>TM</sup>, ProMotion Director's Chair<sup>TM</sup>, ProMotion Director's Tools<sup>TM</sup>, No-cost motion video<sup>TM</sup>, and the ProMotion logo are trademarks of Alliance Semiconductor Corporation. Other trademarks are the property of their respective holders.

Manual researched and written by M. Gadzikowski and M. Shanmugasundaram. Contributors include S. Greene, A. Daniel, G. Tsztoo, J. Washburn, N. Taneja, C. Nguyen, V. Reddy, B. Schnaitter. L. Poitras.

| Τc | ıble of | contents                                |

|----|---------|-----------------------------------------|

| 1  | Intr    | oduction1                               |

|    |         | Features1                               |

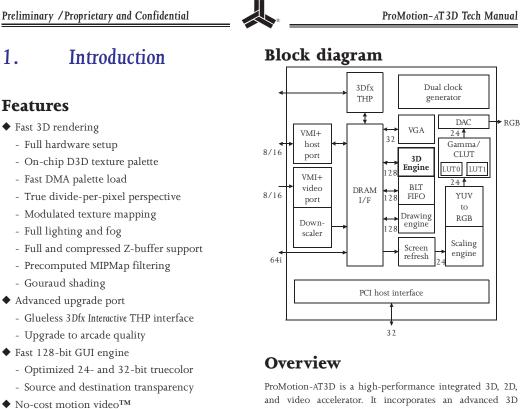

|    |         | Block diagram                           |

|    |         | Overview1                               |

|    |         | Software drivers and BIOS2              |

|    |         | Flexible memory interface               |

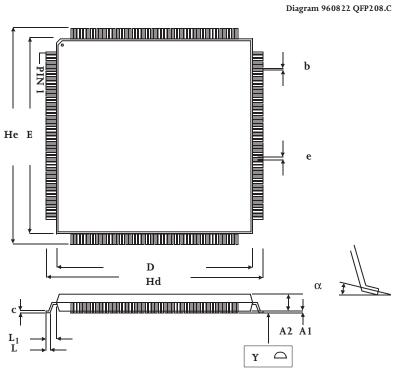

|    |         | Manufacturing package                   |

|    |         | 3Dfx Interactive THP interface          |

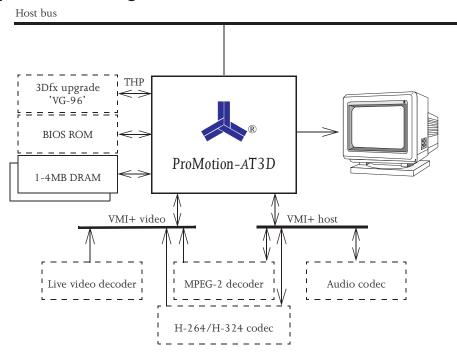

|    |         | System block diagram                    |

| 2  | Fun     | ctional description5                    |

|    | 2.1     | 3D rendering accelerator                |

|    | 2.2     | THP coprocessor interface               |

|    | 2.3     | 2D graphics accelerator                 |

|    | 2.4     | Motion video accelerator                |

|    | 2.5     | VGA controller                          |

|    | 2.6     | Clock generator and DAC 7               |

|    | 2.7     | VGA modes 7                             |

|    | 2.8     | PCI host interface 14                   |

|    | 2.9     | ROM BIOS interface 14                   |

|    | 2.10    | DRAM interface                          |

|    | 2.11    | Monitor and feature connector interface |

|    | 2.12    | VMI+ video interface                    |

|    | 2.13    | VMI+ Host interface                     |

|    | 2.14    | DDC 2.0B support                        |

| 3  | VGA     | registers19                             |

|    | 3.1     | VGA attribute controller registers      |

|    | 3.2     | VGA general registers 19                |

|    | 3.3     | VGA sequencer registers                 |

|    | 3.4     | VGA graphics controller registers 19    |

|    | 3.5     | VGA CRTC registers                      |

|    | 3.6     | VGA palette DAC registers               |

i

$\oplus$

Preliminary Information

¢

ProMotion-AT3D Databook

L ProMotion-AT3D Databook Preliminary Information ProMotion-AT3D extended registers......23 4.14.2 4.3 4.44.54.64.7 4.8 4.9 4.10 4.11VMI+ host port registers ...... 41 4.12 4.13 4.14 4.15 4.16 4.17 Pin description ......49 5.1 5.2 5.3 5.4 5.5 Feature connector interface: VSVPC mode ...... 51 5.6 Feature connector interface: VAFC mode ...... 51 5.7 VMI+ video input port...... 51 5.8 5.9 General purpose I/O interface ...... 53 5.10 5.11 5.12 5.13

ii

4

5

| Prel | iminary | / Information                               | ProMotion-AT3D Databook |

|------|---------|---------------------------------------------|-------------------------|

| 6    | Con     | figuration straps                           | <b>6</b> 1              |

|      | 6.1     | ProMotion-AT3D configuration straps         |                         |

|      | 6.2     | Reserved AT3D configuration straps          |                         |

|      | 6.3     | ProMotion family configuration strap deltas |                         |

| 7    | Elec    | trical characteristics                      |                         |

|      | 7.1     | Absolute maximum ratings                    |                         |

|      | 7.2     | Recommended operating conditions            |                         |

| 8    | AC 1    | timing                                      |                         |

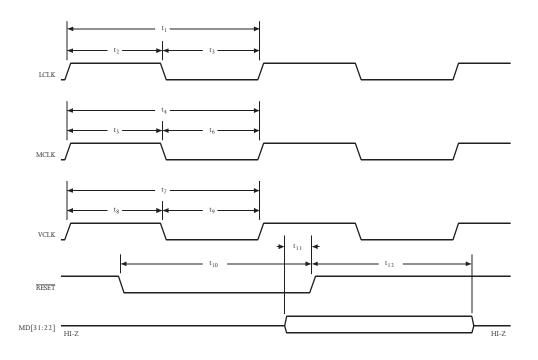

|      | 8.1     | Clock and reset timing                      |                         |

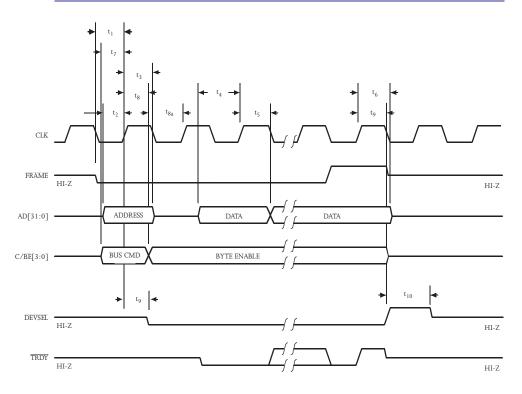

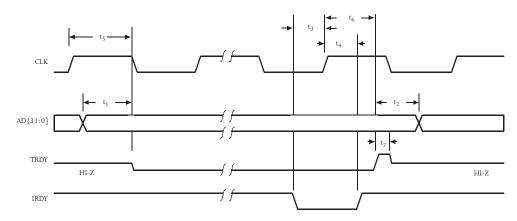

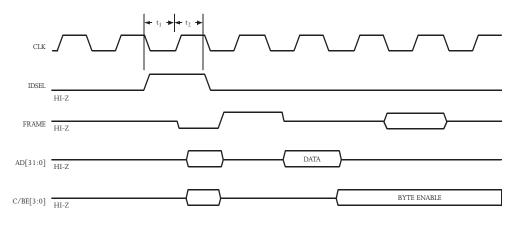

|      | 8.2     | Host interface timing                       |                         |

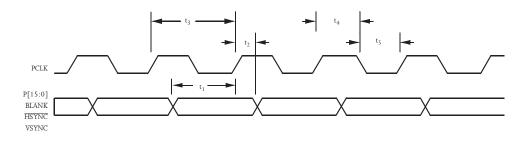

|      | 8.3     | Display memory timing                       |                         |

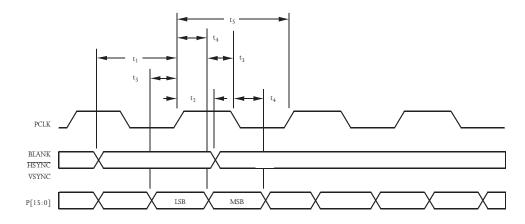

|      | 8.4     | Feature connector timing                    |                         |

|      | 8.5     | VMI+ and THP timing                         |                         |

|      | 8.6     | Test conditions                             |                         |

| 9    | Phys    | sical dimensions                            |                         |

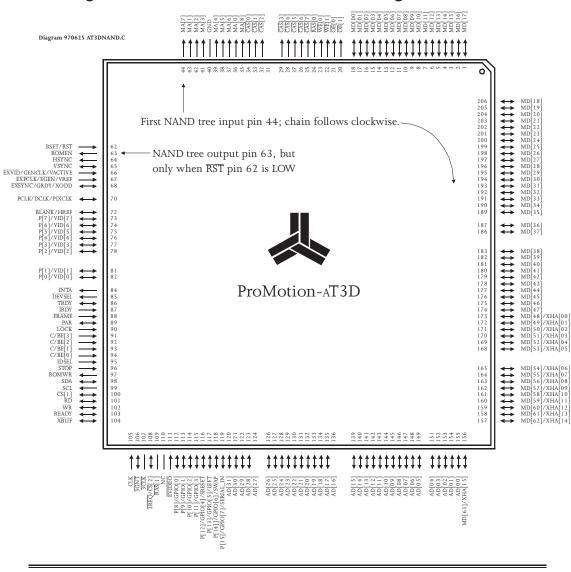

|      | -       | D NAND tree                                 |                         |

| - •  | 10.1    |                                             |                         |

|      | 10.2    | 0                                           |                         |

| 11   | 10.1    | phics programming notes                     |                         |

| ••   | -       | ProMotion registers                         |                         |

|      | 11.1    | 6                                           |                         |

|      | 11.2    | _                                           |                         |

|      | 11.4    |                                             |                         |

|      | 11.5    |                                             |                         |

|      | 11.6    |                                             |                         |

|      | 11.7    |                                             |                         |

| 12   |         | ion video notes                             |                         |

|      | 12.1    | Software standards                          |                         |

|      | 12.1    |                                             |                         |

|      | 12.2    | Motion video in the vWindow                 |                         |

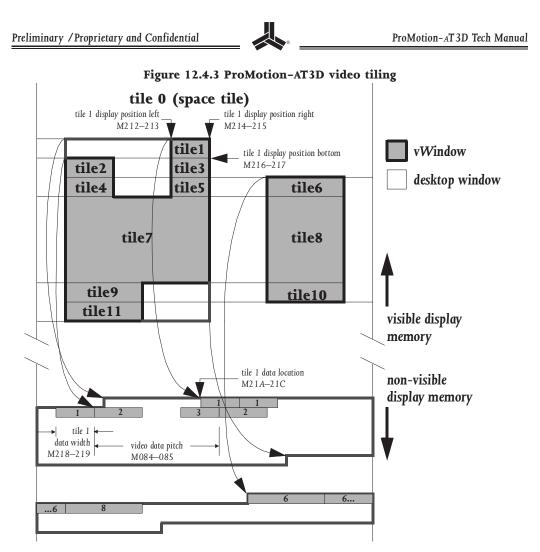

|      |         | Video tile allocation procedure             |                         |

| 13   |         | Motion-AT3D bi-endian support               |                         |

|      |         | Overview                                    |                         |

|      | 10.1    |                                             | 1 1                     |

Copyright ©1997 Alliance Semiconductor; All rights reserved

| roMotion-A | T3D Databook                           | Preliminary Informatio |

|------------|----------------------------------------|------------------------|

| 4 3D p     | rogramming notes                       |                        |

|            | Texture mapping                        |                        |

|            | lard VGA register descriptions.        |                        |

|            | VGA attribute controller registers     |                        |

|            | VGA general registers                  |                        |

|            | VGA sequencer registers                |                        |

|            | VGA graphics controller registers      |                        |

|            | VGA CRTC registers                     |                        |

|            | VGA palette RAM registers              |                        |

|            | ided register descriptions             |                        |

|            | Extended setup registers               |                        |

|            | Extended CRTC registers                |                        |

|            | 2D Drawing engine registers            |                        |

|            | Motion video registers                 |                        |

|            | Video tile buffer registers            |                        |

|            | Video tile buffer register groups 0–11 |                        |

|            | Extended configuration registers       |                        |

|            | Hardware cursor registers              |                        |

|            | PCI configuration registers            |                        |

|            | DAC registers                          |                        |

|            | Clock registers and formulas           |                        |

|            | General purpose I/O registers          |                        |

|            | VMI+ host port registers               |                        |

|            | THP interface registers                |                        |

|            | VMI+ video port registers              |                        |

|            | 3D rendering engine registers          |                        |

|            | Polygon vertex stack registers         |                        |

|            | Polygon stack register groups 0–2      |                        |

|            | Texture scale registers                |                        |

|            | Test Registers                         |                        |

|            | formats                                |                        |

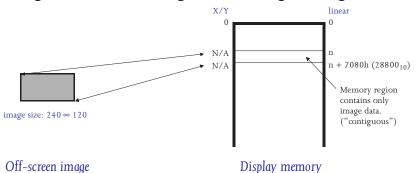

|            | vWindow data formats in display memor  |                        |

|            | Memory video formats                   |                        |

|            | ,<br>Memory graphics formats           |                        |

|            | ndices                                 |                        |

|            | Glossary                               |                        |

|            | Windows 3.11 driver configuration      |                        |

Copyright @1997 Alliance Semiconductor; All rights reserved

$\oplus$

| Preliminary | Information                                     | ProMotion-AT3D Databook |

|-------------|-------------------------------------------------|-------------------------|

| 10.0        |                                                 | 2.1.1                   |

| 18.3        | Windows95 Driver configuration                  |                         |

| 18.4        | ProMotion stepping information                  |                         |

| 18.5        | Registers used to identify controller revisions |                         |

| 18.6        | Recommended 3Dfx THP interface                  |                         |

| 18.7        | Recommended pinout THP connector (Rev. 3)       |                         |

| 18.8        | Recommended VMI+ interface                      |                         |

| 18.9        | Promotion-AT3D extended memory map              |                         |

v

$\oplus$

$\mathbf{k}$

ProMotion-AT3D Databook

Preliminary Information

ProMotion-AT3D Technical manual

## Preface

#### Statement of intent

Alliance provides this document for development partners, not as an invitation for reverse engineering Alliance proprietary and confidential information.

#### Intended audience

Material presented in Section 1 through Section 9 of this manual appears in the ProMotion-AT3D Databook. This material, intended for the video board (hardware) developer, has been updated to reflect changes made since that databook went to press, including addition of a NAND tree as Section 10. Section 11 through Section 17 contain material intended for software driver developers, providing an introduction to ProMotion<sup>®</sup> features. Section 15 through Section 16 provide a detailed reference to the ProMotion register set. Section 18 is an appendix including a glossary and late breaking material.

#### Reserved registers and bits

To prevent unexpected operation, all reserved register bits should be written with 0s and masked off if read back. Future compatability is jeopardized if this procedure is not followed.

#### Writing conventions

| Register addresse | es and indices appear in hexadecimal; bits are indicated in decimal.                              |

|-------------------|---------------------------------------------------------------------------------------------------|

| XXX.YY            | indicates an I/O mapped index/data accessible register with index at XXXh and index value of YYh. |

| Mnnn              | indicates memory mapped offset nnn (hex) from register base address.                              |

| [ZZ:zz]           | indicates bits ZZh through zzh.                                                                   |

Critical notes and important warnings are set apart from other material with horizontal lines and have this symbol in the margin.

Hints and tips have this symbol in the margin.

#### ProMotion-AT3D Technical manual

Preliminary /Proprietary and Confidential

### NDA Confidential information

Material included in this manual includes confidential information which could compromise Alliance's position if disclosed. Refer to your non-disclosure agreement with Alliance Semiconductor Corporation for further details of fair use.

Do not show this manual to anyone without an NDA from Alliance.

Copyright ©1997 Alliance Semiconductor; All rights reserved

¢

vi

- Smooth scaling and color conversion

- 64 step bi-linear filter with full line buffer

- DirectDraw/DirectVideo/DCI support

- Multiple independent video windows

- Hardware occlusion without loss of quality

- VMI compatible TV/video port

- Glueless 7110/7111 support

- Hardware MPEG support

- Interpolated downscaling filter

- ◆ Integrated 175 MHz DAC & clockgen

- Programmable HW gamma & color correctionFull 256×24-bit CLUT RAM

- ◆ VESA<sup>®</sup> standards: VAFC, DPMS, DDC 2.0B

- ◆ High throughput PCI v2.1 interface

- Programmable bi-endian support

- ◆ Flexible EDO DRAM interface

- 1, 1.5, 2, 3, 4 MB configurations

- Single-cycle (1–2 MB) and interleaved (3–4 MB)

- Programmable resolution to 1600×1200

and video accelerator. It incorporates an advanced 3D rendering engine with a powerful Windows graphical user interface accelerator engine, unique motion video acceleration hardware and a high-precision DAC + clock generator, all in a single integrated 208-pin PQFP package. The AT3D is fully pin-compatible with previous-generation ProMotion-6422 and AT24 controllers.

The chip's 128-bit internal architecture and ultra high performance memory interface give the AT3D superior performance in a low-cost mainstream Windows accelerator. Hardware gamma correction and a full 256∞24-bit CLUT ensure optimum color quality.

ProMotion-AT3D acts as the central media hub in a feature rich multimedia subsystem. AT3D's video input port implements a superset of the Video Module Interface (VMI) standard. AT3D supports glueless 8/16-bit connection to live video decoders such as 7110 & 7111 with filtered downscaling, and an 8/16-bit host port connects to ISA or Motorola style devices, including audio, MPEG, and videoconferencing codecs. A hardware scaler with bilinear filter and full line buffer smoothly scales playback or capture windows from native size up to full screen at full speed.

ProMotion-AT3D also drives a proprietary 'THP' upgrade port jointly developed with 3Dfx Interactive, Inc., for highperformance seamless upgradability to arcade-quality 3D hardware acceleration.

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

Copyright ©1997 Alliance Semiconductor; All rights reserved

(

#### Preliminary / Proprietary and Confidential

#### Software drivers and BIOS

- ◆ ProMotion Director's Chair<sup>™</sup> for Windows 95<sup>™</sup>

- Direct3D, DirectDraw<sup>™</sup> & DirectVideo<sup>™</sup>

- Windows  $NT^{TM}$  4.0, 3.5x

- Direct3D, DirectDraw<sup>™</sup>

- OpenGL MCD

- ♦ Major 3D APIs

- 3Dfx interactive GLIDE<sup>TM</sup>

- Argonaut Brender

- Criterion Renderware

- ◆ ProMotion Director's Chair<sup>™</sup> for Windows<sup>™</sup> 3.X

- Display control interface (DCI)

- Resolution switching on the fly

- Virtual desktop to 1600×1200

- Microsoft Video for Windows

- ♦ AutoDesk® ADI

- WordPerfect® 6.0

- ♦ OS/2<sup>™</sup> Warp, 2.11

- ♦ SCO Open Desktop<sup>™</sup>

- ♦ Linux

- ◆ Industry standard Phoenix<sup>®</sup> VGA BIOS

- VESA DPMS power management

- DDC 2.0B

- VESA BIOS extensions

- ⇒ Complete, high-performance, robust

Alliance supports the ProMotion family with high-quality flat-model optimized driver software. ProMotion drivers take full advantage of ProMotion-AT3D hardware and the latest software technology to accelerate real performance of real applications, from word processing and spreadsheets to the most demanding CAD programs and multimedia software.

The same driver set supports all register-compatible ProMotion controllers: 32xx, 64xx, ATxx, EDxx.

The ProMotion driver set accelerates all major operating environments, graphics-intensive software, and motion video applications. With 100% VGA and VESA compatibility, ProMotion controllers can also run standard DOS and VBE-compatible applications directly without driver software.

Source code for ProMotion drivers and BIOS is available to permit customization and differentiation.

## Flexible memory interface

|     | 256 colors | 32K/64K colors | 16M colors |

|-----|------------|----------------|------------|

| 1 M | 1152×864   | 800×600        | 640×480    |

| 2 M | 1600×1200  | 1152×864       | 800×600    |

| 4 M | 1600×1200  | 1600×1200      | 1280×1024  |

Manufacturing package

- ◆ Reference PCB designs

- OEM software utilities

- Customer software utilities

- ⇒ Full customer support

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

ProMotion's optimized memory interface delivers highquality non-interlaced truecolor display at up to 1280×1024 resolution, using economical EDO DRAM.

ProMotion reference designs, OEM tools, and application notes reduce time-to-market. Alliance's OEM support and quality standards, developed over years as a high-volume system supplier to the PC industry, meet the strictest requirements.

Copyright ©1997 Alliance Semiconductor; All rights reserved

$\oplus$

2

## **3Dfx Interactive THP interface**

- ◆ Voodoo Graphics 'VG-96' module

- 40+ MPixel/second fill rate

- Bilinear filtered and advanced filtered textures

- Polygon anti-aliasing

- Alpha blending

- Programmable fog table

- GLIDE<sup>TM</sup> low-level software API

- Strong developer support

- $\Rightarrow$  Upgrade path from mass-market to leading-edge

\* Pre

#### Preliminary / Proprietary and Confidential

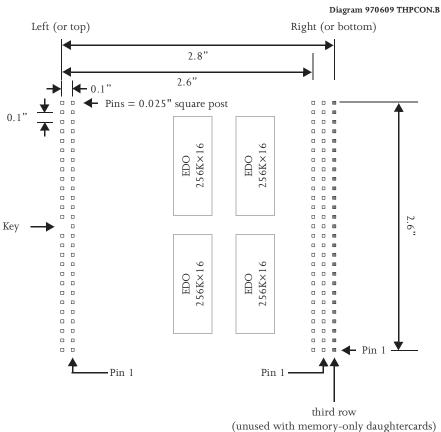

Thanks to Alliance Semiconductor's unique partnership with 3Dfx Interactive, Inc., the ProMotion accelerator family offers unmatched flexibility and upgradability. ProMotion-AT3D's proprietary 'THP' upgrade port, jointly developed by Alliance and 3Dfx, supports glueless interface to the 3Dfx 'VG-96' chipset, for super-advanced PC rendering performance and special effects.

Motherboards and adapters designed with ProMotion-AT3D and outfitted with the inexpensive THP upgrade connector can be upgraded using a daughtercard module based on the VG-96 chipset. Direct3D<sup>M</sup> and GLIDE<sup>M</sup> based software titles for AT3D can transparently take advantage of VG-96 capabilities.

The VG-96 upgrade represents just one possible use of the THP port. THP is an extensible platform suitable for new Alliance and 3Dfx offerings, ensuring that manufacturers' designs and users' systems will not face early obsolescence.

3

## System block diagram

**\***

Preliminary / Proprietary and Confidential

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

## 2. Functional description

### 2.1 3D rendering accelerator

ProMotion-AT3D features a high speed **3D rendering engine** to accelerate texture-mapped 3D polygons. The AT3D rendering engine is designed for speed to make game development easy. High triangle and fill rate performance enable all supported features and effects across the 640×480×16 display, at 30 frames per second and higher. Thanks to its high speed rendering engine, ProMotion-AT3D enables developers to focus on content rather than the micro-optimizations required by lower-performance hardware.

Fully perspective correct, ProMotion-AT3D texture mapping implements true **divide-per-pixel perspective** with no performance penalty. The on-chip **setup engine** computes edge deltas, off-loading expensive divides from the host CPU, and—more importantly—reducing PCI traffic to less than 40 bytes per vertex. **Hardware tri-strip support** further reduces PCI traffic for common triangle mesh constructs.

An on-chip **texture lookup table** (TLUT), separate from the DAC CLUT, is optimized for Direct3D and other indexed texture environments, reducing texture memory requirements to 4 or 8 bits/texel. Off-screen **palette caching** with a fast palette load instruction permits a separate full 256-entry palette per texture, or even per polygon. In texture mapping, the indexed texel passes through the TLUT for conversion to a direct color value, which then passes through interpolated lighting modulation and fog blending stages before being written to the back buffer. TLUT bypass allows for **RGB textures** as well.

Hardware MIPMapping allows software to store pre-filtered textures, avoiding the substantial performance hit of on-the-fly filtering. Texture memory for multiple map levels comes from the savings associated with palettized textures.

A **Z-buffer stage** in the rendering pipeline provides accurate hidden surface removal. Proprietary techniques permit Z-buffering in as little as 8KB off screen memory, leaving more memory for richer textures.

## 2.2 **THP coprocessor interface**

ProMotion's proprietary **THP coprocessor interface** jointly developed with 3Dfx Interactive, Inc., provides a high-bandwidth control and data interface for coprocessors like the 3Dfx 'VG-96.' Refer to "Recommended 3Dfx THP interface," described on page 317.

5

Preliminary / Proprietary and Confidential

## 2.3 2D graphics accelerator

The ProMotion-AT3D integrated MMUI accelerator includes a high performance **128-bit** graphics accelerator designed for demanding truecolor, hi-color, and 256-color GUI and CAD applications. An optimized **BLT engine** maximizes performance of host-to-screen and screen-to-screen operations. A separate drawing engine efficiently handles pattern fills, text rendering, lines and polygons. Advanced features include:

- 256 raster operations

- Color DitherFill<sup>TM</sup>

- Source and destination transparency

- Programmable BLT stride

- Line draw

- Strip draw

- Quick-start and auto-update capability

- Linear memory access

- Mono-to-color expansion

- Clipping

- Hardware cursor

#### 2.4 Motion video accelerator

An on-chip **motion video accelerator** enables software codecs to achieve 30 fps full-screen playback with no additional hardware. ProMotion-AT3D accomplishes this feat by off-loading the CPU-intensive tasks of scaling and color space conversion, and by minimizing the memory bandwidth required for display of decompressed video data.

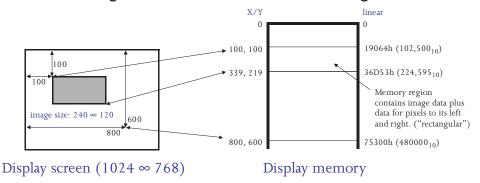

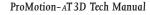

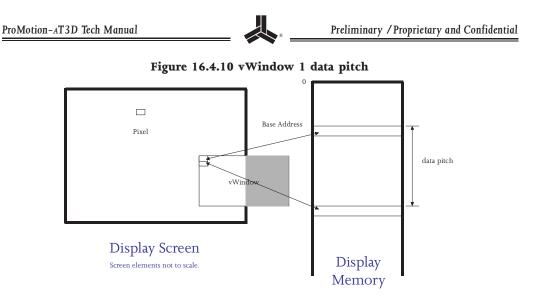

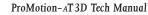

The chip manages a hardware motion video window, the vWindow<sup>TM</sup>. When displaying the vWindow, the controller stretches by programmable X and Y factors ranging from 1.01 to 255.0. High-precision **bilinear interpolation filter** and **on-chip line buffer** circuitry enhance the quality of scaled low-resolution images. **Hardware occlusion support** in up to  $1280 \approx 1024$  means full quality video even in the most demanding system resolutions.

Motion video data may be in pseudo-color, RGB, or YUV format (4:2:2, 4:1:1, or 4:0:0). ProMotion-AT3D converts YUV data to RGB "on the fly" for display in photorealistic color using ProMotion's onboard DAC. The advanced ProMotion architecture permits full 24-bit color for motion video data, even when the graphics desktop uses lower color depth. With ProMotion-AT3D, even a 1MB graphics system can display 8-bit graphics up to 1024×768 resolution, along with 24-bit full-screen motion video.

The ProMotion architecture maximizes motion video performance as well. Because YUV format is more compact than truecolor RGB, and because each motion video frame is sent across the host bus at its unscaled resolution, the host sends a minimum of data across the system bus. Because ProMotion-AT3D does scaling on the fly, it reads only the minimum required data for each screen update, making the best possible use of available bandwidth. ProMotion's innovative architecture removes bandwidth bottlenecks to display multimedia data at its full speed.

ProMotion-AT3D Tech Manual

## 2.5 VGA controller

A fully register-compatible Super VGA controller in the ProMotion-AT3D chip supports all monochrome and 4-bit packed and planar modes. Super VGA modes conform to VESA standards. Refer to Table 2.6.1 for extended modes.

#### Table 2.5 VGA modes

| VGA mode | Screen format    | Supported display mode |  |

|----------|------------------|------------------------|--|

| 0, 1     | $360 \times 400$ | text                   |  |

| 2, 3     | $720 \times 400$ | text                   |  |

| 4,5      | 320 × 200        | graphics               |  |

| 6        | 640 × 200        | graphics               |  |

| 7        | $720 \times 400$ | text                   |  |

| D        | 320 × 200        | graphics               |  |

| Е        | 640 × 200        | graphics               |  |

| F        | 640 × 350        | graphics               |  |

| 10       | 640 × 350        | graphics               |  |

| 11       | $640 \times 480$ | graphics               |  |

| 12       | $640 \times 480$ | graphics               |  |

| 13       | 320 × 200        | graphics               |  |

2.6

## Clock generator and DAC

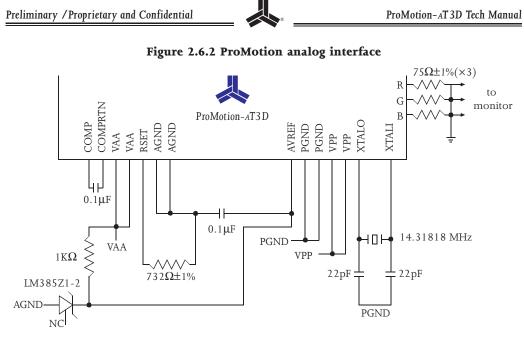

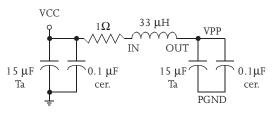

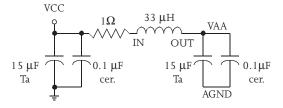

ProMotion-AT3D's high-frequency clock generator and integrated palette DAC give high-quality, high-resolution display. Table 2.6.1 details ProMotion resolutions available with standard BIOS. Analog biasing circuitry appears in Figure 2.6.2 and Figure 2.6.3.

Hardware gamma correction in 16- and 24-bit modes—including separate gamma tables for desktop and video areas—permits software color matching and brightness/tint control.

Preliminary / Proprietary and Confidential

#### Table 2.6.1 ProMotion-AT3D extended graphics modes

| Display<br>resolution | Bits per<br>pixel | VESA mode<br>(hex) | Mem. req.<br>(MB) | Vert.freq.<br>(Hz) | Horiz. freq.<br>(KHz) | Pixel freq.<br>(MHz) | VCLK freq.<br>(MHz) |

|-----------------------|-------------------|--------------------|-------------------|--------------------|-----------------------|----------------------|---------------------|

| 640×400               | 8                 | 100                | 1.0               | 70                 | 31.5                  | 25.175               | 25.175              |

|                       | 32                |                    | 1.0               | 70                 | 31.5                  | 25.175               | 25.175              |

| 640×480               | 4                 |                    | 1.0               | 60                 | 31.5                  | 25.175               | 25.175              |

|                       | 8                 | 101                | 1.0               | 60                 | 31.5                  | 25.175               | 25.175              |

|                       | 15,16             | 110, 111           | 1.0               | 60                 | 31.5                  | 25.175               | 25.175              |

|                       | 24                | 112                | 1.0               | 60                 | 31.5                  | 25.175               | 25.175              |

|                       | 32                | 112                | 2.0               | 60                 | 31.5                  | 25.175               | 25.175              |

|                       | 4                 |                    | 1.0               | 72                 | 37.9                  | 31.5                 | 31.5                |

|                       | 8                 |                    | 1.0               | 72                 | 37.9                  | 31.5                 | 31.5                |

|                       | 15,16             |                    | 1.0               | 72                 | 37.9                  | 31.5                 | 31.5                |

|                       | 24                |                    | 1.0               | 72                 | 37.9                  | 31.5                 | 31.5                |

|                       | 32                |                    | 2.0               | 72                 | 37.9                  | 31.5                 | 31.5                |

|                       | 4                 |                    | 1.0               | 75                 | 37.5                  | 31.5                 | 31.5                |

|                       | 8                 |                    | 1.0               | 75                 | 37.5                  | 31.5                 | 31.5                |

|                       | 15,16             |                    | 1.0               | 75                 | 37.5                  | 31.5                 | 31.5                |

|                       | 24                |                    | 1.0               | 75                 | 37.5                  | 31.5                 | 31.5                |

|                       | 32                |                    | 2.0               | 75                 | 37.5                  | 31.5                 | 31.5                |

|                       | 8                 |                    | 1.0               | 85                 | 43.3                  | 36.0                 | 36.0                |

|                       | 15,16             |                    | 1.0               | 85                 | 43.3                  | 36.0                 | 36.0                |

|                       | 32                |                    | 2.0               | 85                 | 43.3                  | 36.0                 | 36.0                |

|                       | 8                 |                    | 1.0               | 100                | 50.95                 | 41.165               | 41.165              |

|                       | 15,16             |                    | 1.0               | 100                | 50.95                 | 41.165               | 41.165              |

|                       | 8                 |                    | 1.0               | 120                | 63.92                 | 53.69                | 53.69               |

|                       | 15,16             |                    | 1.0               | 120                | 63.92                 | 53.69                | 53.69               |

Notes for Table 2.6.1:

1 Modes supported through BIOS are independent of drivers.

8

2 Implementation of refresh rates is driver-dependant.

3 Refresh rates shown may require high MCLK and/or non-fast page DRAM.

¢

#### Table 2.6.1 ProMotion-AT3D extended graphics modes

| Display<br>resolution | Bits per<br>pixel | VESA mode<br>(hex) | Mem. req.<br>(MB) | Vert.freq.<br>(Hz) | Horiz. freq.<br>(KHz) | Pixel freq.<br>(MHz) | VCLK freq<br>(MHz) |

|-----------------------|-------------------|--------------------|-------------------|--------------------|-----------------------|----------------------|--------------------|

| 800×600               | 4                 | 102                | 1.0               | 56                 | 35.2                  | 36                   | 36                 |

|                       | 8                 | 103                | 1.0               | 56                 | 35.2                  | 36                   | 36                 |

|                       | 15,16             | 113, 114           | 1.0               | 56                 | 35.2                  | 36                   | 36                 |

|                       | 24                |                    | 2.0               | 56                 | 35.2                  | 36                   | 36                 |

|                       | 32                | 115                | 1.5†              | 56                 | 35.2                  | 36                   | 36                 |

|                       | 8                 |                    | 1.0               | 60                 | 37.9                  | 40                   | 40                 |

|                       | 15,16             |                    | 1.0               | 60                 | 37.9                  | 40                   | 40                 |

|                       | 24                |                    | 2.0               | 60                 | 37.9                  | 40                   | 40                 |

|                       | 32                |                    | 1.5†              | 60                 | 37.9                  | 40                   | 40                 |

|                       | 8                 |                    | 1.0               | 72                 | 48.1                  | 50                   | 50                 |

|                       | 15,16             |                    | 1.0               | 72                 | 48.1                  | 50                   | 50                 |

|                       | 24                |                    | 2.0               | 72                 | 48.1                  | 50                   | 50                 |

|                       | 32                |                    | 1.5†              | 72                 | 48.1                  | 50                   | 50                 |

|                       | 8                 |                    | 1.0               | 75                 | 46.9                  | 50                   | 50                 |

|                       | 15,16             |                    | 1.0               | 75                 | 46.9                  | 50                   | 50                 |

|                       | 24                |                    | 2.0               | 75                 | 46.9                  | 50                   | 50                 |

|                       | 32                |                    | 1.5†              | 75                 | 46.9                  | 50                   | 50                 |

|                       | 8                 |                    | 1.0               | 85                 | 53.7                  | 56.3                 | 56.3               |

|                       | 15,16             |                    | 1.0               | 85                 | 53.7                  | 56.3                 | 56.3               |

|                       | 32                |                    | 1.5†              | 85                 | 53.7                  | 56.3                 | 56.3               |

|                       | 8                 |                    | 1.0               | 100                | 64.0                  | 65.0                 | 65.0               |

|                       | 15,16             |                    | 1.0               | 100                | 64.0                  | 65.0                 | 65.0               |

|                       | 8                 |                    | 1.0               | 120                | 75.2                  | 76.96                | 76.96              |

|                       | 15, 16            |                    | 1.0               | 120                | 75.2                  | 76.96                | 76.96              |

Notes for Table 2.6.1:

1 Modes supported through BIOS are independent of drivers.

2 Implementation of refresh rates is driver-dependant.

3 Refresh rates shown may require high MCLK and/or non-fast page DRAM.

Preliminary / Proprietary and Confidential

#### Table 2.6.1 ProMotion-AT3D extended graphics modes

| Display<br>resolution | Bits per<br>pixel | VESA mode<br>(hex) | Mem. req.<br>(MB) | Vert.freq.<br>(Hz) | Horiz. freq.<br>(KHz) | Pixel freq.<br>(MHz) | VCLK freq.<br>(MHz) |

|-----------------------|-------------------|--------------------|-------------------|--------------------|-----------------------|----------------------|---------------------|

| 1024×768              | 8                 |                    | 1.0               | 43(86i)            | 35.52                 | 44.9                 | 44.9                |

|                       | 15,16             |                    | 2.0               | 43(86i)            | 35.52                 | 44.9                 | 44.9                |

|                       | 4                 | 104                | 1.0               | 60                 | 48.3                  | 65                   | 65                  |

|                       | 8                 | 105                | 1.0               | 60                 | 48.3                  | 65                   | 65                  |

|                       | 15,16             | 117                | 2.0               | 60                 | 48.3                  | 65                   | 65                  |

|                       | 32                | 118                | 3.0†              | 60                 | 48.3                  | 65                   | 65                  |

|                       | 4                 |                    | 1.0               | 70                 | 56.5                  | 75                   | 75                  |

|                       | 8                 |                    | 1.0               | 70                 | 56.5                  | 75                   | 75                  |

|                       | 15,16             |                    | 2.0               | 70                 | 56.5                  | 75                   | 75                  |

|                       | 32                |                    | 4.0               | 70                 | 56.5                  | 75                   | 75                  |

|                       | 4                 |                    | 1.0               | 75                 | 60                    | 80                   | 80                  |

|                       | 8                 |                    | 1.0               | 75                 | 60                    | 80                   | 80                  |

|                       | 15,16             |                    | 2.0               | 75                 | 60                    | 80                   | 80                  |

|                       | 32                |                    | 3.0†              | 75                 | 60                    | 80                   | 80                  |

|                       | 4                 |                    | 1.0               | 85                 | 68.6                  | 94.5                 | 94.5                |

|                       | 8                 |                    | 1.0               | 85                 | 68.6                  | 94.5                 | 94.5                |

|                       | 32                |                    | 3.0†              | 85                 | 68.6                  | 94.5                 | 94.5                |

|                       | 4                 |                    | 1.0               | 100                | 80.8                  | 108                  | 108                 |

|                       | 8                 |                    | 1.0               | 100                | 80.8                  | 108                  | 108                 |

|                       | 15,16             |                    | 2.0               | 100                | 80.8                  | 108                  | 108                 |

| 1152×864              | 8                 |                    | 1.0               | 60                 | 54.1                  | 80                   | 80                  |

|                       | 15,16             |                    | 2.0               | 60                 | 54.1                  | 80                   | 80                  |

|                       | 32                |                    | 4.0               | 60                 | 54.1                  | 80                   | 80                  |

|                       | 8                 |                    | 1.0               | 70                 | 53.9                  | 94.5                 | 94.5                |

|                       | 15,16             |                    | 2.0               | 70                 | 53.9                  | 94.5                 | 94.5                |

|                       | 32                |                    | 4.0               | 70                 | 53.9                  | 94.5                 | 94.5                |

|                       | 8                 |                    | 1.0               | 75                 | 67.5                  | 100                  | 100                 |

|                       | 15,16             |                    | 2.0               | 75                 | 67.5                  | 100                  | 100                 |

|                       | 8                 |                    | 1.0               | 85                 | 77.09                 | 121.5                | 121.5               |

|                       | 15,16             |                    | 2.0               | 85                 | 77.09                 | 121.5                | 121.5               |

Notes for Table 2.6.1:

1 Modes supported through BIOS are independent of drivers.

2 Implementation of refresh rates is driver-dependant.

3 Refresh rates shown may require high MCLK and/or non-fast page DRAM.

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

#### Table 2.6.1 ProMotion-AT3D extended graphics modes

| Display<br>resolution | Bits per<br>pixel | VESA mode<br>(hex) | Mem. req.<br>(MB) | Vert.freq.<br>(Hz) | Horiz. freq.<br>(KHz) | Pixel freq.<br>(MHz) | VCLK freq.<br>(MHz) |

|-----------------------|-------------------|--------------------|-------------------|--------------------|-----------------------|----------------------|---------------------|

| 1280×1024             | 8                 |                    | 2.0               | 43(86i)            | 96.4                  | 78.75                | 78.75               |

|                       | 4                 | 106                | 1.0               | 60                 | 64                    | 110                  | 110                 |

|                       | 8                 | 107                | 2.0               | 60                 | 64                    | 100                  | 100                 |

|                       | 15,16             | 119,11A            | 4.0               | 60                 | 64                    | 110                  | 110                 |

|                       | 24                | 11B                | 4.0               | 60                 | 72                    | 75                   | 75                  |

|                       | 4                 |                    | 1.0               | 75                 | 80.0                  | 135                  | 135                 |

|                       | 8                 |                    | 2.0               | 75                 | 80.5                  | 144                  | 144                 |

|                       | 15,16             |                    | 4.0               | 75                 | 80.5                  | 144                  | 144                 |

|                       | 4                 |                    | 1.0               | 85                 | 91.146                | 157                  | 157                 |

| 1600×1200             | 8                 |                    | 2.0               | 48(96i)            | 62.5                  | 135                  | 135                 |

|                       | 8                 |                    | 2.0               | 60                 | 75                    | 160                  | 160                 |

|                       | 15,16             |                    | 4.0               | 60                 | 70                    | 70                   | 70                  |

|                       | 8                 |                    | 2.0               | 65                 | 81.25                 | 175.5                | 175.5               |

Notes for Table 2.6.1:

1 Modes supported through BIOS are independent of drivers.

2 Implementation of refresh rates is driver-dependant.

3 Refresh rates shown may require high MCLK and/or non-fast page DRAM.

¢

Preliminary / Proprietary and Confidential

| Table 2.6.2 AT3D memory requirements for | r vesa | modes |

|------------------------------------------|--------|-------|

|------------------------------------------|--------|-------|

|            |             |       |      | VESA/ | VBE vertical | refresh |      |      |

|------------|-------------|-------|------|-------|--------------|---------|------|------|

|            |             | 43Hz  |      |       |              |         |      |      |

| Resolution | Color depth | (86i) | 56Hz | 60Hz  | 70Hz         | 72Hz    | 75Hz | 85Hz |

| 640×480    | 4-bit       |       |      | 1 MB  |              | 1 MB    | 1 MB | 1 MB |

|            | 8-bit       |       |      | 1 MB  |              | 1 MB    | 1 MB | 1 MB |

|            | 15/16-bit   |       |      | 1 MB  |              | 1 MB    | 1 MB | 1 MB |

|            | 32-bit      |       |      | 2 MB  |              | 2 MB    | 2 MB | 2 MB |

| 800×600    | 4-bit       |       |      | 1 MB  |              | 1 MB    | 1 MB |      |

|            | 8-bit       |       | 1 MB | 1 MB  |              | 1 MB    | 1 MB |      |

|            | 15/16-bit   |       |      | 1 MB  |              | 1 MB    | 1 MB |      |

|            | 32-bit      |       |      | 2 MB  | 2 MB         | 2 MB    | 2 MB | 2 MB |

| 1024×768   | 4-bit       |       |      | 1 MB  |              | 1 MB    | 1 MB |      |

|            | 8-bit       | 1 MB  |      | 1 MB  | 1 MB         | 1 MB    | 1 MB | 1 MB |

|            | 15/16-bit   |       |      | 2 MB  |              | 2 MB    | 2 MB | 2 MB |

|            | 32 MB-bit   |       |      | 4 MB  |              | 4 MB    | 4 MB |      |

| 1154×864   | 4-bit       |       |      | 1 MB  |              | 1 MB    | 1 MB |      |

|            | 8-bit       |       |      | 1 MB  |              | 1 MB    | 1 MB |      |

|            | 15/16-bit   |       |      | 2 MB  |              | 2 MB    | 2 MB |      |

| 1280×1024  | 4-bit       |       |      | 1 MB  |              | 1 MB    |      |      |

|            | 8-bit       | 2 MB  |      | 2 MB  |              | 2 MB    | 2 MB | 2 MB |

|            | 15/16-bit   |       |      | 4 MB  |              |         | 4 MB |      |

|            | 32-bit      |       |      | 4 MB  |              |         |      |      |

| 1600×1200  | 8-bit       | 2 MB* |      | 2 MB  | 2 MB         |         |      |      |

|            | 15/16-bit   |       |      | 4 MB  |              |         |      |      |

\* 1600×1200 8-bit VESA interlaced mode is 48Hz (96i).

NOTE: All AT3D refresh rates comply with VESA tolerances,  $\pm 0.5\%$  PCLK.

¢

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

Preliminary / Proprietary and Confidential

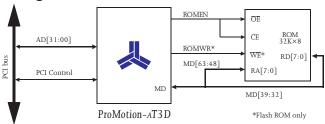

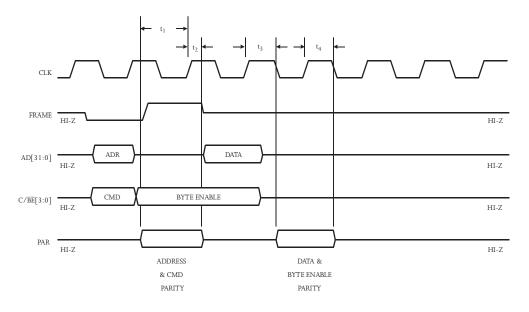

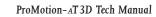

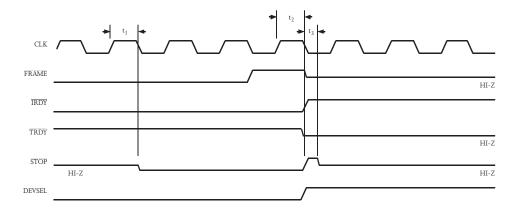

## 2.7 PCI host interface

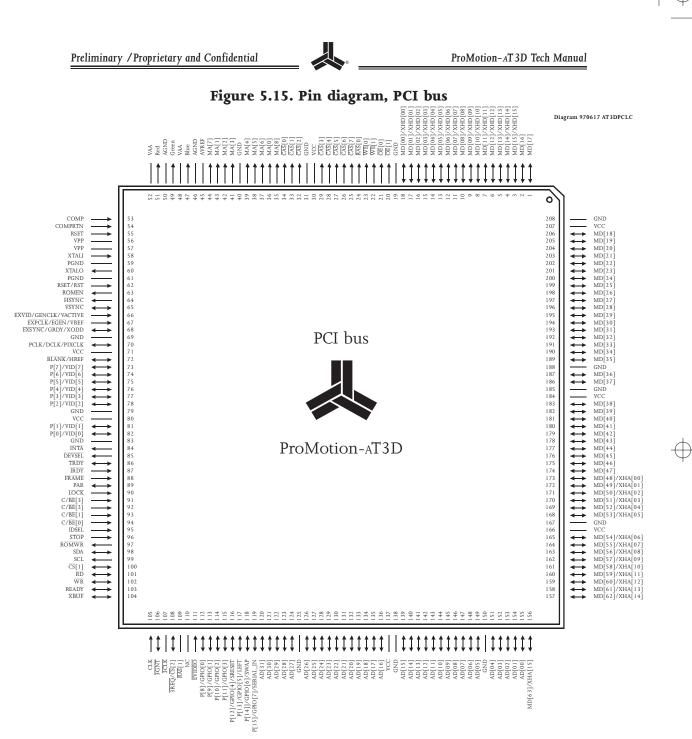

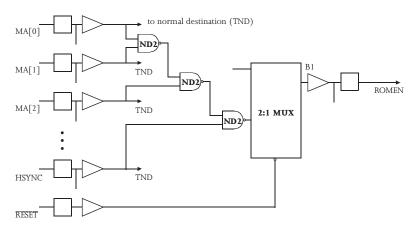

ProMotion-AT3D interfaces directly to a PCI bus. The controller supports **zero-wait-state bursts** of successive dwords into the chip's inbound command FIFO. After dispatching commands and data to the AT3D, the host CPU can continue execution. Configuration strap MD[27] selects PCI bus operation; refer to "ProMotion-AT3D configuration straps," on page 61.

#### Figure 2.7. Glueless PCI/ROM interface

## 2.8 **ROM BIOS interface**

ProMotion-AT3D supports address, data, and flash write control interface for ROM BIOS or Flash EEPROM as shown in Figure 2.7, "Glueless PCI/ROM interface."

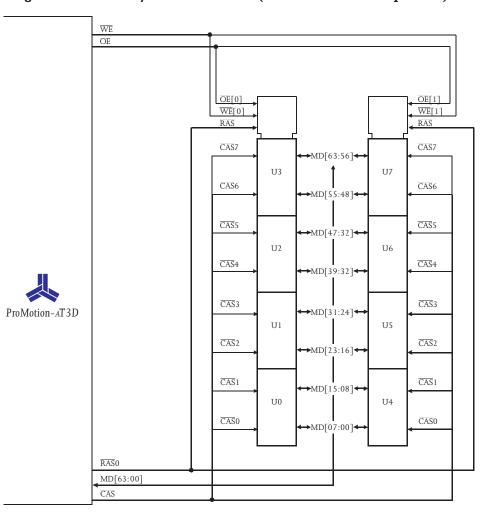

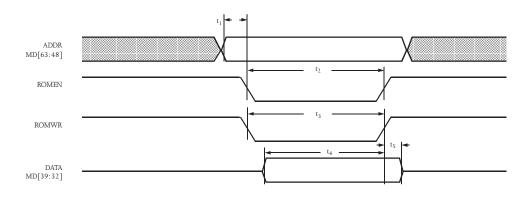

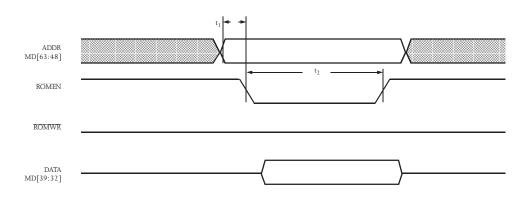

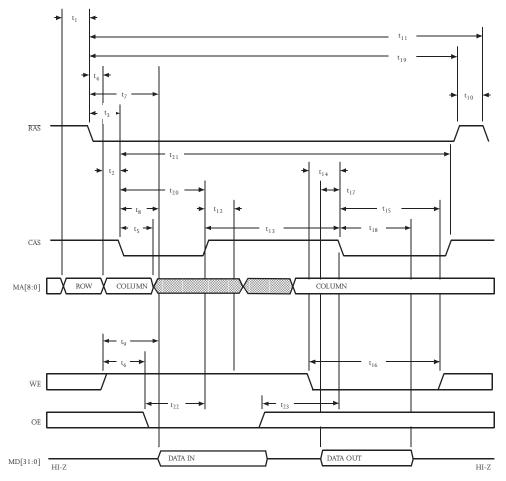

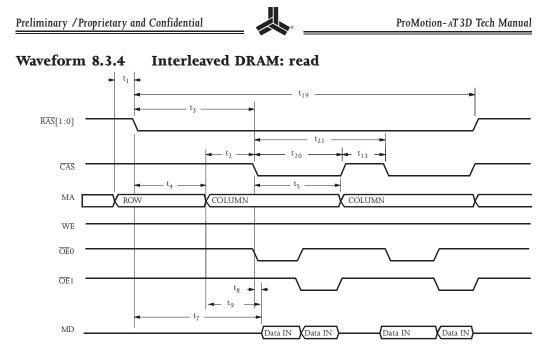

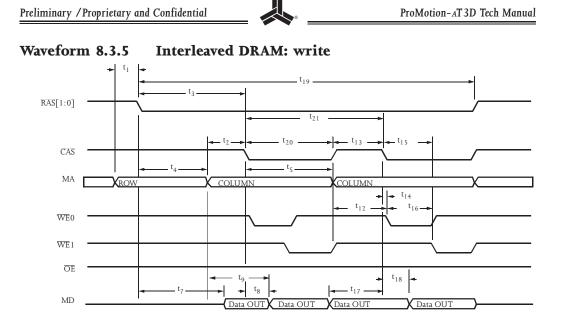

## 2.9 DRAM interface

ProMotion-AT3D controls 1, 2, or 4 megabytes of DRAM frame buffer memory. For 1MB and 2MB systems 256K×4, ×8, or ×16 parts may be used. For 4MB systems 256K×8 or ×16 may be used. Dual-CAS EDO and fast-page memories are supported.

**Single cycle EDO** timing permits high memory efficiency even in 1–2 MB configurations. Programmable memory timing allows ProMotion-AT3D to use standard speed DRAM or take advantage of high-speed DRAMs.

14

¢

Preliminary / Proprietary and Confidential

ProMotion-AT3D Tech Manual

Preliminary / Proprietary and Confidential

## 2.10 Monitor and feature connector interface

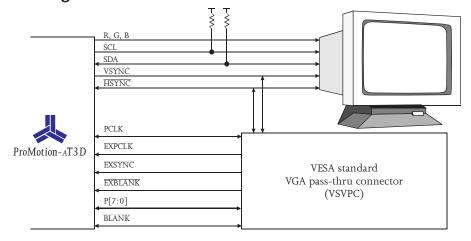

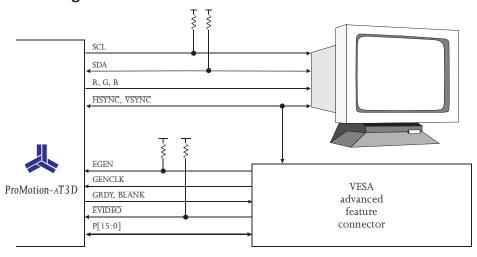

For interoperability with video capture and other multimedia cards, ProMotion-AT3D offers two feature connector options, selectable by configuration strap MD[26]. In VSVPC mode, ProMotion-AT3D connects to an industry-standard 8-bit VGA pass-through connector; refer to Figure 2.10.1, "Glueless VSVPC feature connector." In VAFC mode, the chip supports the VESA Advanced Feature Connector standard, including 16-bit input and output. With the circuit shown in Figure 2.10.2, VAFC can be implemented without an expensive multiport DAC.

#### Figure 2.10.1: Glueless VSVPC feature connector

Figure 2.10.2: Glueless VAFC feature connector

16

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

Copyright ©1997 Alliance Semiconductor; All rights reserved

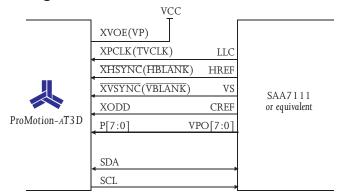

## 2.11 VMI+ video interface

ProMotion-AT3D provides a VMI-compatible interface port for live video and hardware codec input. The controller's VMI+ video input port supports 8-bit and 16-bit digital video. Refer to ProMotion implementation notes for details.

#### Figure 2.11. VMI+ interface and decoder

### 2.12 VMI+ Host interface

ProMotion-AT3D supports host modes A and B, corresponding to Intel- and Motorola-style peripheral interface, to drive control and data inputs of MPEG coprocessors of other devices. Refer to ProMotion VMI implementation notes for details.

### 2.13 DDC 2.0B support

ProMotion-AT3D includes dedicated I/O pins for bi-directional DDC monitor connections. Using industry standard protocols, software can use DDC to read status and write configurations to compliant monitors. The same serial interface can control serial devices such as EEPROM for nonvolatile configuration strap.

\*

Preliminary / Proprietary and Confidential

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

¢

Preliminary / Proprietary and Confidential

## 3. VGA registers

#### Table 3.1 VGA attribute controller registers

| I/O mapped port | Index |                                                   |      |     |

|-----------------|-------|---------------------------------------------------|------|-----|

| (hex)           | (hex) | Register                                          | Bits | r/w |

| 3C0             | -     | "Index," described on page 119                    | 6    | r/w |

| 3C0             | 00–0F | "Palette registers 0-15," described on page 119   | 6    | r/w |

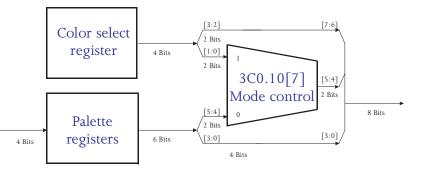

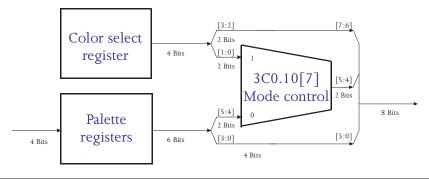

| 3C0             | 10    | "Mode control," described on page 119             | 8    | r/w |

| 3C0             | 11    | "Overscan color," described on page 121           | 8    | r/w |

| 3C0             | 12    | "Color plane enable," described on page 121       | 6    | r/w |

| 3C0             | 13    | "Horizontal pixel panning," described on page 122 | 4    | r/w |

| 3C0             | 14    | "Color select," described on page 123             | 4    | r/w |

#### Table 3.2 VGA general registers

| I/O mapped port | Index |                                                  |      |     |

|-----------------|-------|--------------------------------------------------|------|-----|

| (hex)           | (hex) | Register                                         | Bits | r/w |

| 3C2             | -     | "Item select/miscellaneous output," described on | 8    | W   |

| 3CC             | -     | page 124                                         | 8    | r   |

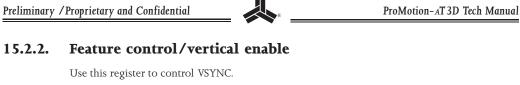

| 3BA/3DA         |       | "Feature control/vertical enable," described on  | 4    | W   |

| 3CA             | -     | page 125                                         | 4    | r   |

| 3C2             | -     | "Input status 0," described on page 126          | 8    | r   |

| 3BA/3DA         |       | "Input status 1," described on page 126          | 6    | r   |

#### Table 3.3 VGA sequencer registers

| I/O mapped port | Index |                                               |      |     |

|-----------------|-------|-----------------------------------------------|------|-----|

| (hex)           | (hex) | Register                                      | Bits | r/w |

| 3C4             | -     | "Sequencer index," described on page 128      | 4    | r/w |

| 3C5             | 00    | "Reset," described on page 128                | 2    | r/w |

| 3C5             | 01    | "Clocking mode," described on page 128        | 6    | r/w |

| 3C5             | 02    | "Map mask," described on page 129             | 4    | r/w |

| 3C5             | 03    | "Character map select," described on page 130 | 6    | r/w |

| 3C5             | 04    | "Memory mode," described on page 131          | 4    | r/w |

#### Table 3.4 VGA graphics controller registers

| Index |                                           |                                                                                                                                                                                                                    |                                                                                                                                                                                                                             |

|-------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (hex) | Register                                  | Bits                                                                                                                                                                                                               | r/w                                                                                                                                                                                                                         |

| -     | "Graphics index," described on page 132   | 4                                                                                                                                                                                                                  | r/w                                                                                                                                                                                                                         |

| 00    | "Set/reset," described on page 132        | 4                                                                                                                                                                                                                  | r/w                                                                                                                                                                                                                         |

| 01    | "Enable set/reset," described on page 132 | 4                                                                                                                                                                                                                  | r/w                                                                                                                                                                                                                         |

| 02    | "Color compare," described on page 133    | 4                                                                                                                                                                                                                  | r/w                                                                                                                                                                                                                         |

| 03    | "Data rotate," described on page 133      | 5                                                                                                                                                                                                                  | r/w                                                                                                                                                                                                                         |

| 04    | "Read map select," described on page 134  | 2                                                                                                                                                                                                                  | r/w                                                                                                                                                                                                                         |

|       | (hex)<br>-<br>00<br>01<br>02<br>03        | (hex)Register-"Graphics index," described on page 13200"Set/reset," described on page 13201"Enable set/reset," described on page 13202"Color compare," described on page 13303"Data rotate," described on page 133 | (hex)RegisterBits-"Graphics index," described on page 132400"Set/reset," described on page 132401"Enable set/reset," described on page 132402"Color compare," described on page 133403"Data rotate," described on page 1335 |

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

19

Copyright @1997 Alliance Semiconductor; All rights reserved

¢

## Table 3.4 VGA graphics controller registers

| I/O mapped port | Index |                                           |      |     |

|-----------------|-------|-------------------------------------------|------|-----|

| (hex)           | (hex) | Register                                  | Bits | r/w |

| 3CF             | 05    | "Graphics mode," described on page 134    | 5    | r/w |

| 3CF             | 06    | "Miscellaneous," described on page 135    | 4    | r/w |

| 3CF             | 07    | "Color don't care," described on page 136 | 4    | r/w |

| 3CF             | 08    | "Bit mask," described on page 137         | 8    | r/w |

## Table 3.5 VGA CRTC registers

| I/O mapped port | Index |                                                        |      |     |

|-----------------|-------|--------------------------------------------------------|------|-----|

| (hex)           | (hex) | Register                                               | Bits | r/w |

| 3D4             | -     | "CRTC index," described on page 138                    | 6    | r/w |

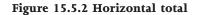

| 3D5             | 00    | "Horizontal total," described on page 138              | 8    | r/w |

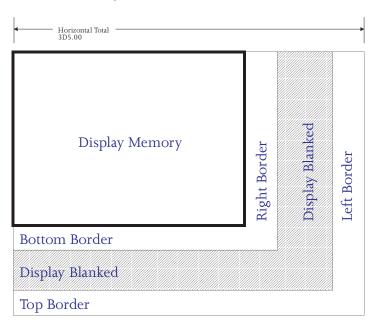

| 3D5             | 01    | "Horizontal display enable end," described on page 140 | 8    | r/w |

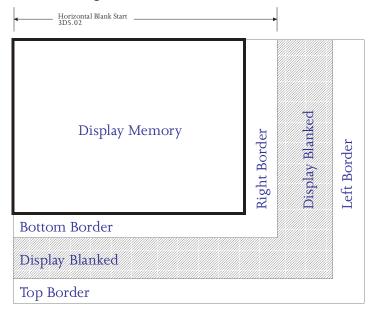

| 3D5             | 02    | "Horizontal blank start," described on page 141        | 8    | r/w |

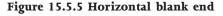

| 3D5             | 03    | "Horizontal blank end," described on page 142          | 8    | r/w |

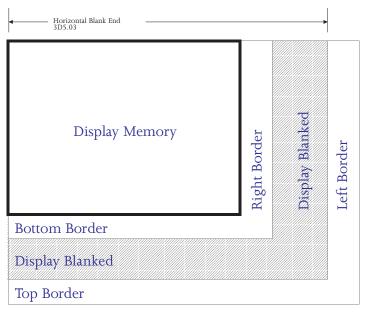

| 3D5             | 04    | "Horizontal retrace start," described on page 143      | 8    | r/w |

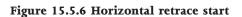

| 3D5             | 05    | "Horizontal retrace end," described on page 144        | 8    | r/w |

| 3D5             | 06    | "Vertical total," described on page 145                | 8    | r/w |

| 3D5             | 07    | "Vertical overflow," described on page 146             | 8    | r/w |

| 3D5             | 08    | "Preset row scan," described on page 146               | 7    | r/w |

| 3D5             | 09    | "Maximum scan line," described on page 147             | 8    | r/w |

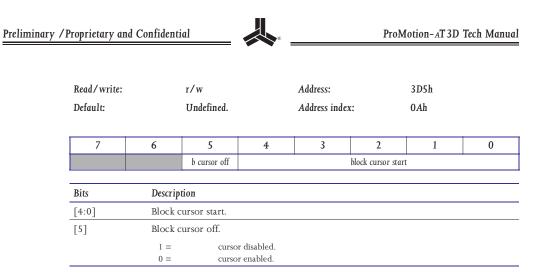

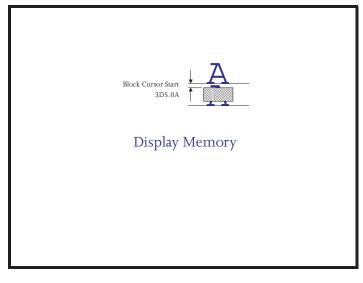

| 3D5             | 0A    | "Block cursor start," described on page 148            | 6    | r/w |

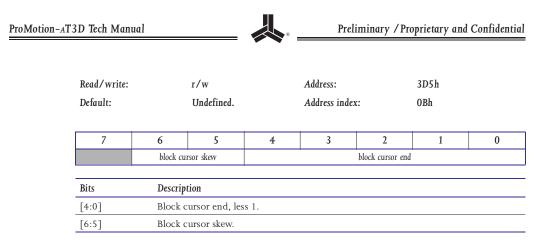

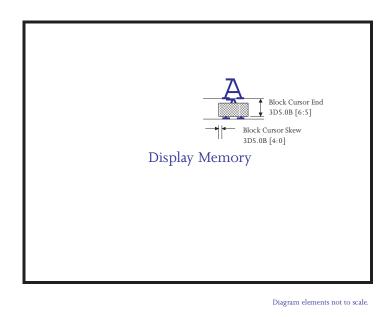

| 3D5             | 0B    | "Block cursor end," described on page 149              | 7    | r/w |

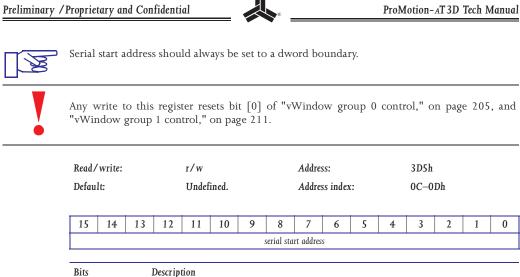

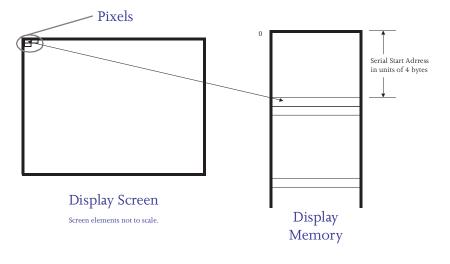

| 3D5             | 0C    | "Serial start address," described on page 150          | 16   | r/w |

| 3D5             | 0E    | "Block cursor location," described on page 151         | 16   | r/w |

| 3D5             | 10    | "Vertical retrace end," described on page 153          | 8    | r/w |

| 3D5             | 11    | "Vertical retrace end," described on page 153          | 8    | r/w |

| 3D5             | 12    | "Vertical display enable end," described on page 154   | 8    | r/w |

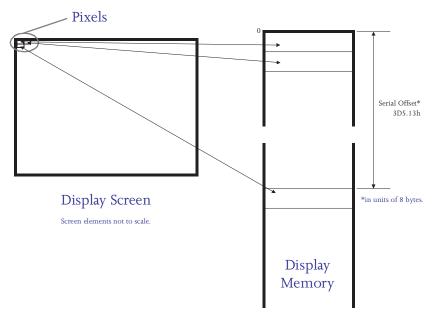

| 3D5             | 13    | "Serial offset," described on page 155                 | 8    | r/w |

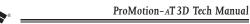

| 3D5             | 14    | "Underline location/dword mode," on page 156           | 7    | r/w |

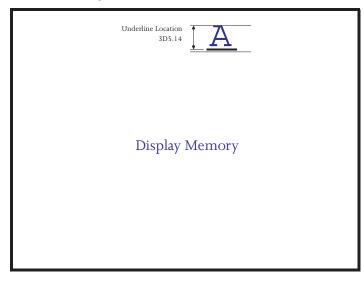

| 3D5             | 15    | "Vertical blank start," described on page 157          | 8    | r/w |

| 3D5             | 16    | "Vertical blank end," described on page 158            | 8    | r/w |

| 3D5             | 17    | "CRTC mode control register," described on page 159    | 8    | r/w |

| 3D5             | 18    | "Line compare," described on page 160                  | 8    | r/w |

| 3D5             | 22    | "Readback latch data," described on page 161           | 8    | r   |

| 3D5             | 24    | "Attribute index data," described on page 161          | 8    | r   |

Document ID 11-50002 Rev. \*\*-06. Printed 6/25/97.

20

$\oplus$

Preliminary / Proprietary and Confidential

ProMotion-AT3D Tech Manual

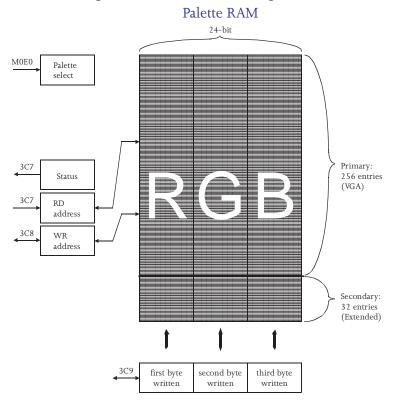

## Table 3.6 VGA palette DAC registers

| I/O<br>mapped | Index   | Memory<br>mapped<br>offset |                                                                       |      |     |

|---------------|---------|----------------------------|-----------------------------------------------------------------------|------|-----|

| port (hex)    | (hex)   | (hex)                      | Register                                                              | Bits | r/w |

| 3C6           | -       | -                          | "Palette RAM pel mask," described on page 163                         | 8    | r/w |

| 3C7           | -       | -                          | "Palette RAM state/read address," described on                        | 8    | W   |

| 3C7           | -       | -                          | page 163                                                              | 2    | r   |

| 3C8           | -       | -                          | "Palette RAM write address," described on page 164                    | 8    | r/w |

| 3C9           | -       | -                          | "Palette RAM data," described on page 164                             | 8    | r/w |

| 3C9           | 000–0FF | -                          | "Primary palette registers 0–255," described on page 165              | 24   | r/w |

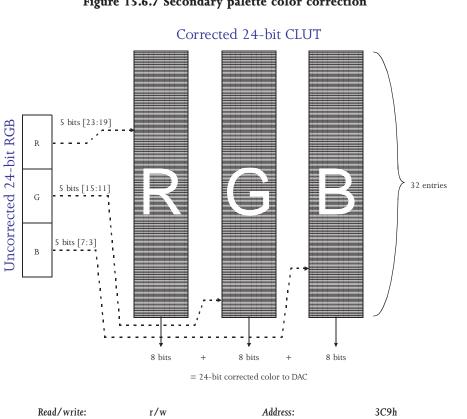

| 3C9           | 100-11F | -                          | "Secondary palette registers 0–31," described on page $165^{\dagger}$ | 24   | r/w |

$^{\dagger}3C9.100-11F$  are extended registers, included in this group for completeness.

.

Preliminary / Proprietary and Confidential

## 4. **ProMotion-AT3D extended registers**

## Table 4.1 Extended setup registers

| I/O<br>mapped<br>port<br>(hex)<br>3C5 | Index<br>(hex)<br>10 | Memory<br>mapped<br>offset<br>(hex) | <b>Register</b><br>"Unlock extended registers," on page 167<br>3C5.10[7:0] unlock<br>Writing 12h unlocks I/O registers. ProMotion                                                                            | Bits<br>8 | r/w<br>r/w | Reset<br>7:0 |

|---------------------------------------|----------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|--------------|

|                                       |                      |                                     | memory mapped registers cannot be locked. Writes to<br>regosters 000–13F pass through the command FIFO.<br>Writes to registers 140–1FF do not pass through the<br>command FIFO.                              |           |            |              |

| 3C5                                   | 11-19                | -                                   | "Chip ID," described on page 167<br>3C5.11[72:0] ASCII string                                                                                                                                                | 72        | r          | -            |

| 3C5                                   | 1A                   | -                                   | "Flat model base address," described on page 168<br>3C5.1A[7:0] base address                                                                                                                                 | 8         | r/w        | [7:0]        |

| 3C5                                   | 1B                   | -                                   | "Remap control," on page 168<br>3C5.1B[5:3] remap host BLT port<br>3C5.1B[2:0] remap ProMotion registers                                                                                                     | 6         | r/w        | [5:0]        |

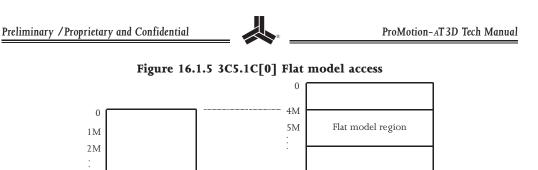

| 3C5                                   | 1C                   | -                                   | "Flat model control," on page 1693C5.1C[0]flat model access3C5.1C[2:1]flat model aperture3C5.1C[3]disable VGA memory access3C5.1C[4]VGA aperture addressing3C5.1C[5]simultanous linear/drawing engine access | 6         | r/w        | [5:0]        |

| 3C5                                   | 1D                   | -                                   | "Alternate access space pointer LOW," described on<br>page 171<br>3C5.1D[7:0] PMPOINTER [9:2]                                                                                                                | 8         | r/w        | -            |

| 3C5                                   | 1E-1F                | -                                   | "Alternate access space decode," described on page<br>172<br>3C5.1E[15:0] PMDECODE                                                                                                                           | 16        | r/w        | [15:0]       |

| 3C5                                   | 20-27                | -                                   | "Scratchpad," described on page 174 <sup>†</sup><br>3C5.20[64:0] scratchpad                                                                                                                                  | 64        | r/w        | -            |

| 3C5                                   | 28                   | -                                   | "Alternate access space pointer HIGH," described on<br>page 177<br>3C5.28[7:0] PMPOINTER [17:10]                                                                                                             | 8         | r/w        | -            |

| 3C5                                   | 29                   | -                                   | Reserved                                                                                                                                                                                                     | -         | -          | -            |

| 3C5                                   | 30                   | -                                   | "BIOS Paging," on page 177         3C5.30[4:0]       BIOS page         3C5.30[6:5]       BIOS page memory mapping         3C5.30[7]       local                                                              | 8         | r/w        | -            |

<sup>†</sup> ProMotion-3210<sup>TM</sup> memory mapped scratchpad is not supported. ProMotion-AT3D scratchpad registers are I/O mapped and reverse compatible with ProMotion-6410<sup>TM</sup>, 6422, AT24, and AT3D.

#### Table 4.1 Extended setup registers

| I/O<br>mapped<br>port | Index | Memory<br>mapped<br>offset |               |                                    |      |     |       |

|-----------------------|-------|----------------------------|---------------|------------------------------------|------|-----|-------|

| (hex)                 | (hex) | (hex)                      | Register      |                                    | Bits | r/w | Reset |

| -                     | -     | 1FC-1FE                    | E "Extended/I | DAC status," on page 178           | 22   | r   | -     |

|                       |       |                            | 1FC[3:0]      | command FIFO entries available     |      |     |       |

|                       |       |                            | 1FC[4]        | DAC threshold red                  |      |     |       |

|                       |       |                            | 1FC[5]        | DAC threshold green                |      |     |       |

|                       |       |                            | 1FC[6]        | DAC threshold blue                 |      |     |       |

|                       |       |                            | 1FC[7]        | signature analyzer busy            |      |     |       |

|                       |       |                            | 1FC[8]        | host BLT in progress               |      |     |       |

|                       |       |                            | 1FC[9]        | host BLT read data available       |      |     |       |

|                       |       |                            | 1FC[10]       | drawing engine busy                |      |     |       |

|                       |       |                            | 1FC[11]       | vertical display active            |      |     |       |

|                       |       |                            | 1FC[12]       | EXVID pin 66 input                 |      |     |       |

|                       |       |                            | 1FC[13]       | EXPCLK pin 67 input                |      |     |       |

|                       |       |                            | 1FC[14]       | EXSYNC pin 68 input                |      |     |       |

|                       |       |                            | 1FC[15]       | feature connector input            |      |     |       |

|                       |       |                            | 1FC[16]       | SDA input, equivalent to 0D0[4]    |      |     |       |

| -                     | -     | 1 FF                       | "Abort," des  | cribed on page 180                 | 0    | w   | -     |

|                       |       |                            | 1FF[]         | any write aborts drawing operation |      |     |       |

<sup>†</sup> ProMotion-3210<sup>TM</sup> memory mapped scratchpad is not supported. ProMotion-AT3D scratchpad registers are I/O mapped and reverse compatible with ProMotion-6410<sup>TM</sup>, 6422, AT24, and AT3D.

## Table 4.2 Extended CRTC registers

| I/O<br>mapped<br>port | Index | Memory<br>mapped<br>offset |                 |                                                                                                         |      |     |                    |

|-----------------------|-------|----------------------------|-----------------|---------------------------------------------------------------------------------------------------------|------|-----|--------------------|

| (hex)                 | (hex) | (hex)                      | Register        |                                                                                                         | Bits | r/w | Reset              |

| 3D5                   | 19    | -                          | "Horizontal in  | terlaced start," on page 181                                                                            | 8    | r/w | [7:0] <sup>†</sup> |

|                       |       |                            | 3D5.19[7:0]     | horizontal interlaced start [7:0] of [8:0]                                                              |      |     |                    |

| 3D5                   | 1 A   | -                          | "Vertical exten | ded overflow," on page 181                                                                              | 5    | r/w | [4:0] <sup>†</sup> |

|                       |       |                            | 3D5.1A[0]       | vertical total [10] of [10:0]. "Vertical total,"<br>described on page 145.                              |      |     |                    |

|                       |       |                            | 3D5.1A[1]       | vertical display enable end [10] of [10:0].<br>"Vertical display enable end," described on<br>page 154. |      |     |                    |

|                       |       |                            | 3D5.1A[2]       | vertical blank start [10] of [10:0]. "Vertical blank start," described on page 157.                     |      |     |                    |

|                       |       |                            | 3D5.1A[3]       | vertical retrace start [10] of [10:0]. "Vertical retrace start," described on page 152                  |      |     |                    |

|                       |       |                            | 3D5.1A[4]       | line compare [10] of [10:0]. "Line<br>compare," described on page 160.                                  |      |     |                    |

<sup>†</sup> Writing to 3D5.00 resets this register unless autoreset is disabled with 3D5.1E.

ProMotion-AT3D Tech Manual

## Table 4.2 Extended CRTC registers

| I/O<br>mapped<br>port | Index | Memory<br>mapped<br>offset |                            |                                                                                                             |      |     |                    |

|-----------------------|-------|----------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------|------|-----|--------------------|

| (hex)                 | (hex) | (hex)                      | Register                   |                                                                                                             | Bits | r/w | Reset              |

| 3D5                   | 1B    | -                          | "Horizontal ov             | verflow," on page 182                                                                                       | 5    | r/w | [4:0] <sup>†</sup> |

|                       |       |                            | 3D5.1B[0]                  | horrizontal total [8] of [8:0]. "Horizontal<br>total," described on page 138.                               |      |     |                    |

|                       |       |                            | 3D5.1B[1]                  | horizontal display enable end [8] of [8:0].<br>"Horizontal display enable end," described                   |      |     |                    |