### **Copyright Notice**

Copyright © 1993 Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies, Inc.

### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

### **Trademark Acknowledgement**

CHIPS Logotype, CHIPSlink, CHIPSPort, ELEAT, LeAPSet, NEAT, NEATsx, PEAK, SCAT, and Wingine are registered trademarks of Chips and Technologies, Inc.

PrintGine, SuperState, SuperMath, SuperMathDX, WinPC and XRAM are trademarks of Chips and Technologies, Incorporated.

IBM®, AT, XT, PS/2, Micro Channel, Enhanced Graphics Adapter, Color Graphics Adapter, Video Graphics Adapter, IBM Color Display, and IBM Monochrome Display are trademarks of International Business Machines Corporation.

Hercules is a trademark of Hercules Computer Technology.

MS-DOS and Windows are trademarks of Microsoft Corporation.

MultiSync is a trademark of Nippon Electric Company (NEC).

Brooktree is a trademark of Brooktree Corporation.

Inmos is a trademark of Inmos Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

VESA is a trademark of Video Electronics Standards Associations.

VL-Bus is a trademark of Video Electronics Standards Associations.

### Disclaimer

This document is provided for the general information of the customer. Chips and Technologies, Inc., reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the data sheet. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

Chips and Technologies, Inc. 2950 Zanker Road San Jose, California 95134 Phone: 408-434-0600 Telex: 272929 CHIPS UR FAX: 408-434-0412 Title: 64300 / 301 Data Sheet

Publication No.: DS167.2 Stock No.: 010167-003 Revision No.: 1.2

## 64300 / 301 Wingine® DGX **DRAM Graphics Accelerator**

- High performance accelerator for computer graphic intensive applications, such as graphical user interface, word processor, spreadsheet and CAD/CAM programs.

- XRAM<sup>TM</sup> Technology (Patent Pending) (64300 only)

- The 64300 / 301 are identical except for one feature: the 64301 does not include XRAM technology

- Optimized interface to multiple bus architectures:

- VESA Local Bus (32-Bit)

- 386DX and 486SX/DX Local Bus (32-Bit)

- ISA Peripheral Bus (16-Bit)

- Three Operand BITBLT

- Supports all 256 logical combinations of Source, Destination and Pattern

- Hardware Assisted Line Draw

- 64x64x2 Hardware Cursor

- 32-Bit Color Expansion

- Zero Wait State Peripheral Bus Operation

- Direct linear mapping to system memory (up to 2MB selectable)

- A complete high performance local bus graphics system requires only the addition of DRAM and BIOS

- Full VGA compatibility

- Supports the VESA Display Power Management Signaling (DPMS) Protocol for desktop computer power management

- RAMDAC power-down and programmable clock provide additional power management capability

- Supports a wide variety of monitor resolutions and color depths (bits per pixel):

- 640x480, 4bpp to 24bpp

- 800x600, 4bpp to 16bpp 1024x768, 4bpp to 16bpp

- 1280x1024, 4bpp to 8bpp

- Integrated RAMDAC

- Up to 16.7 Million Colors (24 bits per pixel)

- 256x18 LUT

- Integrated Clock Synthesizer

- Programmable MCLK up to 72MHz

- Programmable PCLK up to 85MHz

- Flexible display memory configurations supporting 512KB to 2MB:

- Four, eight or sixteen 256Kx4 DRAMs

- One, two or four 256Kx16 DRAMs

- Support for Color Key and video overlay with external video data input

- Flash' ROM support for in-circuit BIOS upgrades

- 208-pin PFP pinouts optimized for PCB layout

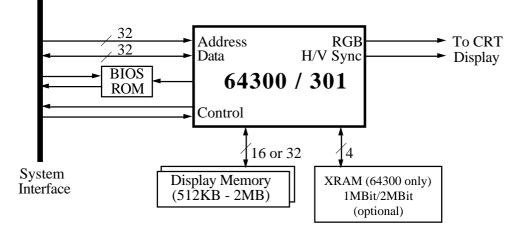

## **System Diagram**

# **Revision History**

| Revision                                                       | Date                                  | By                              | Comment                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|----------------------------------------------------------------|---------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| $\begin{array}{c} 0.1 \\ 0.2 \\ 0.3 \\ 0.4 \\ 0.5 \end{array}$ | 9/92<br>12/92<br>1/93<br>2/93<br>5/93 | DR<br>DR<br>DR<br>DR<br>DR / DH | Internal Review - Rough Draft<br>Internal Review<br>Updated Pinouts & Added Functional Description<br>Modified Register Summary &Added Electrical Specifications Section<br>Added Preliminary Timing & Application Schematics<br>Removed 'autoincrement' bit from DR08<br>Changed memory interface pin names to match DRAM pin names:                                                                                                 |  |  |  |  |  |  |

|                                                                |                                       |                                 | MAD0-7 & MBD0-7changed toMAD0-15MCD0-7 & MDD0-7changed toMBD0-15RASAB# & RASCD#changed toRASA# & RASB#CAS0A# & CAS0B#changed toCASAL0# & CASAH0#CAS0C# & CAS0D#changed toCASBL0# & CASBH0#CAS1A# & CAS1B#changed toCASAL1# & CASBH1#CAS1C# & CAS1D#changed toCASBL1# & CASBH1#                                                                                                                                                        |  |  |  |  |  |  |

| 0.6                                                            | 6/93                                  | DR                              | Added 64301 Specifications<br>Modified ISA Timing, Circuits and DAC specs<br>Changed nineut delated CPI04 and added VIPEE                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 1.0                                                            | 8/93                                  | DR / DH                         | Changed pinout - deleted GPI04 and added VREF<br>Changed pin location of VREF and RSET<br>Fixed notation/naming of configuration pins<br>Fixed pin numbers in Application Schematics<br>Added proper clock synthesizer decoupling in Application Schematics<br>Changed ICT mechanism<br>Removed references to 16-bit 386SX support                                                                                                    |  |  |  |  |  |  |

| 1.1<br>1.2                                                     | 9/93<br>11/93                         | DR<br>DR                        | Modified DRAM Read/Write Timing Table<br>Changed pinout from 104-156<br>Deleted GPIO0 and GPIO1 from XR71 and XR72<br>Changed definition of pin 104 from VREF to COMP<br>Deleted support for a 2x clock input<br>Added support for 1024x768x16BPP mode<br>Added direct interface for VESA Standard IBM VGA Feature Connector<br>Deleted MDA, Hercules, and CGA backwards compatibility support<br>Removed support for external RAMDAC |  |  |  |  |  |  |

# **Table of Contents**

| Section                                                                                                              | Page             |

|----------------------------------------------------------------------------------------------------------------------|------------------|

| Introduction                                                                                                         | 7                |

| Performance                                                                                                          | 7                |

| XRAM Accelerator Cache (64300 only)                                                                                  | 7                |

| Local Bus                                                                                                            | 7                |

| Scalability                                                                                                          | 7<br>8<br>8<br>8 |

| Acceleration Features                                                                                                | 8                |

| Cost Optimization                                                                                                    | 8                |

| High Integration<br>DRAM Display Memory                                                                              | 8                |

| DRAM Display Memory                                                                                                  | 8<br>8           |

| Differentiating Features<br>Desktop Power Management<br>Minimum Chip Count / Board Space                             | 8                |

| Desktop Power Management                                                                                             | 8                |

| Minimum Chip Count / Board Space                                                                                     | 8                |

| Display Memory Interface                                                                                             | 8                |

| CPU Bus Interface                                                                                                    | 9                |

| Display Interface.<br>Full Compatibility                                                                             | 9                |

| Full Compatibility                                                                                                   | 9                |

| Write Protection                                                                                                     | 9<br>9           |

| Extension Registers                                                                                                  |                  |

| Context Switching                                                                                                    | 9                |

| Reset, Setup, and Test Modes                                                                                         | 10               |

| Reset Mode                                                                                                           | 10               |

| Setup Mode                                                                                                           | 10               |

| Tri-State Mode                                                                                                       | 10               |

| ICT (In-Circuit-Test) Mode                                                                                           | 10               |

| Chip Architecture                                                                                                    | 11               |

| Chip Architecture<br>Sequencer                                                                                       | 11               |

| CRT Controller                                                                                                       | 11               |

| Graphics Controller                                                                                                  | 11               |

| Attribute Controller                                                                                                 | 11               |

| VGA Color Palette/DAC                                                                                                | 11               |

| BitBlt Engine.                                                                                                       | 11               |

| BitBlt Engine<br>Hardware Cursor                                                                                     | 12               |

| Clock Synthesizer                                                                                                    | 12               |

| Configuration Switches                                                                                               | 12               |

| General Purpose I/O                                                                                                  | 12<br>12         |

| Clock Selection                                                                                                      | $12^{12}$        |

| BIOS ROM Interface                                                                                                   | 13               |

| Flexible Architecture                                                                                                | 13               |

| Package                                                                                                              | 13               |

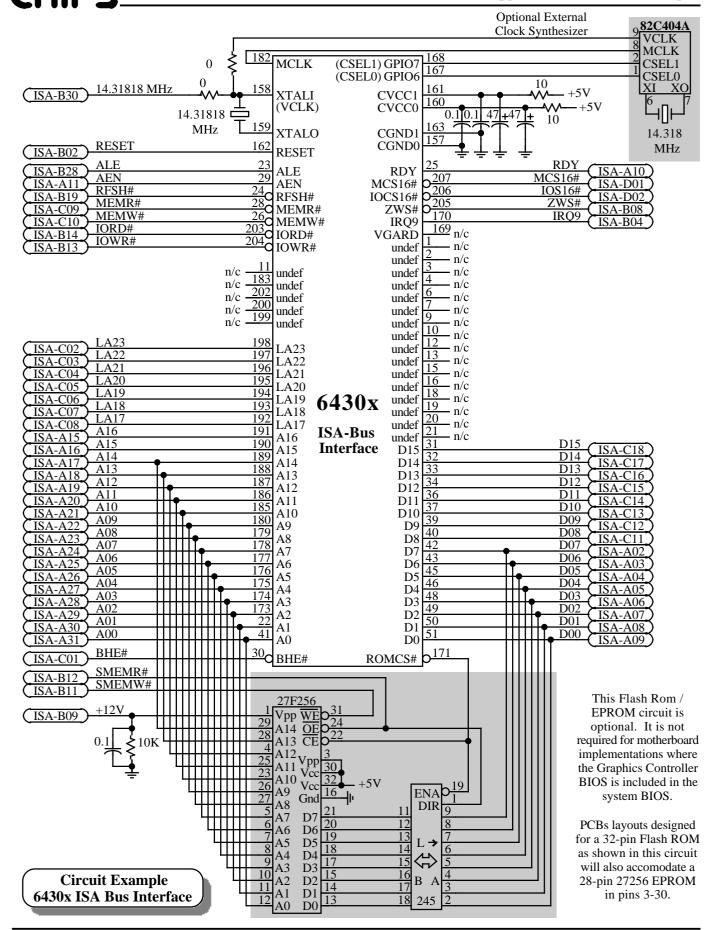

| Package<br>Application Schematic Examples                                                                            | 13               |

|                                                                                                                      |                  |

| Pinouts                                                                                                              | 15               |

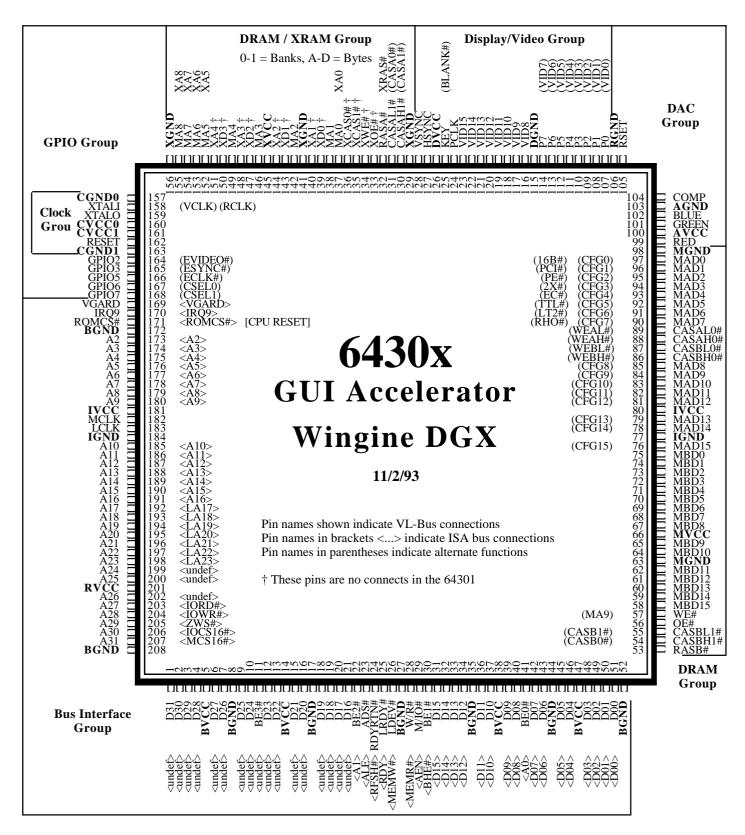

| Pin Diagram                                                                                                          | 15               |

| Pin List - Bus Interface                                                                                             | 16               |

| Pin List - Display Memory Interface                                                                                  | 18               |

| Pin List - CRT Interface                                                                                             | 19               |

| Pin Descriptions - CPU/VL-Bus Interface<br>Pin Descriptions - ISA Bus Interface<br>Pin Descriptions - Display Memory | 20               |

| Pin Descriptions - ISA Bus Interface                                                                                 | 24               |

| Pin Descriptions - Display Memory                                                                                    | 27               |

| Pin Descriptions - Video Interface                                                                                   | 30               |

| Pin Descriptions - Clock, Power & Ground<br>Pin Descriptions - Digital Power & Ground                                | 32               |

| Pin Descriptions - Digital Power & Ground                                                                            | 33               |

|                                                                                                                      |                  |

®

| Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Register and Port Address Summaries<br>I/O Map<br>CGA, MDA, and Hercules Registers<br>EGA Registers<br>VGA Registers<br>VGA Indexed Registers<br>Extension Registers<br>32-Bit Registers                                                                                                                                                                                                                                                                                                    | 35<br>36<br>36<br>36<br>37<br>38                                                                                                                    |

| Register Descriptions<br>Global Control (Setup) Registers<br>General Control and Status Registers<br>Sequencer Registers<br>CRT Controller Registers<br>Graphics Controller Registers<br>Attribute Controller and<br>Color Palette Registers                                                                                                                                                                                                                                                | 47<br>49<br>53<br>69<br>77                                                                                                                          |

| Extension Registers<br>32-Bit Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83<br>113                                                                                                                                           |

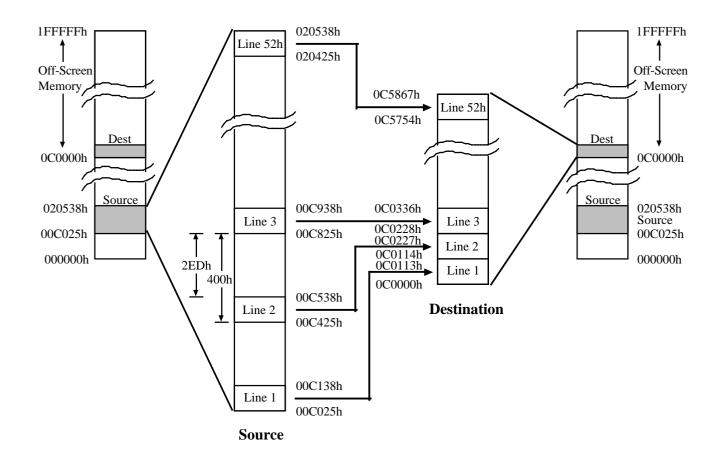

| Functional Description<br>System Interface<br>Functional Blocks<br>Bus Interface<br>ISA Interface<br>VL-Bus Interface<br>Direct Processor Interface<br>Display Memory Interface<br>Memory Architecture<br>XRAM Accelerator (64300 only)<br>RAMDAC<br>Clocks<br>Internal Clock Synthesizer<br>MCLK Operation<br>VCLK Operation<br>Programming Clock Synthesizer<br>Programming Constraints<br>Programming Example<br>BitBlt Engine<br>Bit Block Transfer<br>Sample Screen-to-Screen Transfer | $\begin{array}{c} 123\\ 123\\ 123\\ 123\\ 124\\ 124\\ 124\\ 125\\ 126\\ 126\\ 126\\ 126\\ 127\\ 127\\ 127\\ 127\\ 128\\ 129\\ 129\\ 130\end{array}$ |

| Compressed Screen-to-Screen Transfer<br>System-to-Screen BitBlts<br>Hardware Cursor<br>Programming                                                                                                                                                                                                                                                                                                                                                                                          | 131<br>133<br>134<br>134                                                                                                                            |

# **Table of Contents**

| Section                                                                                                                                                                                                     | Page                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

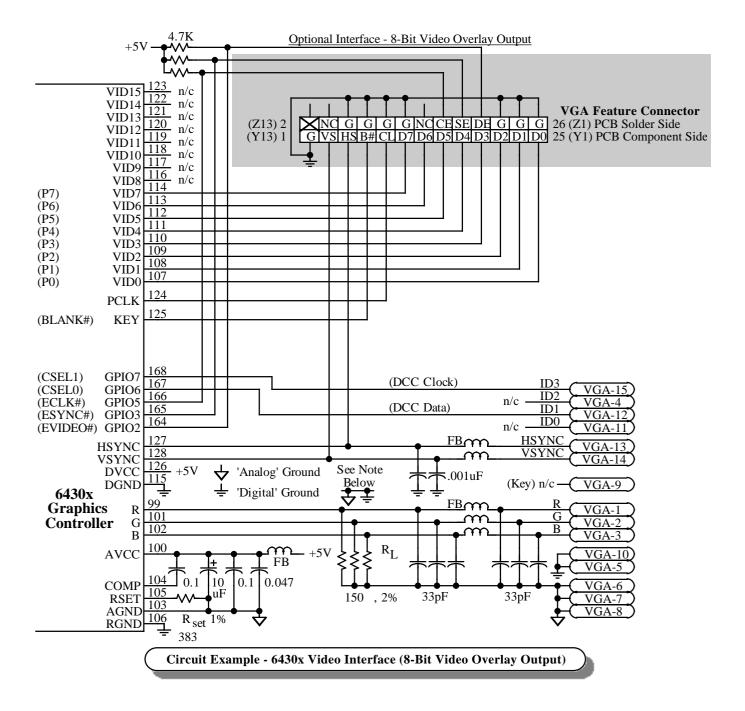

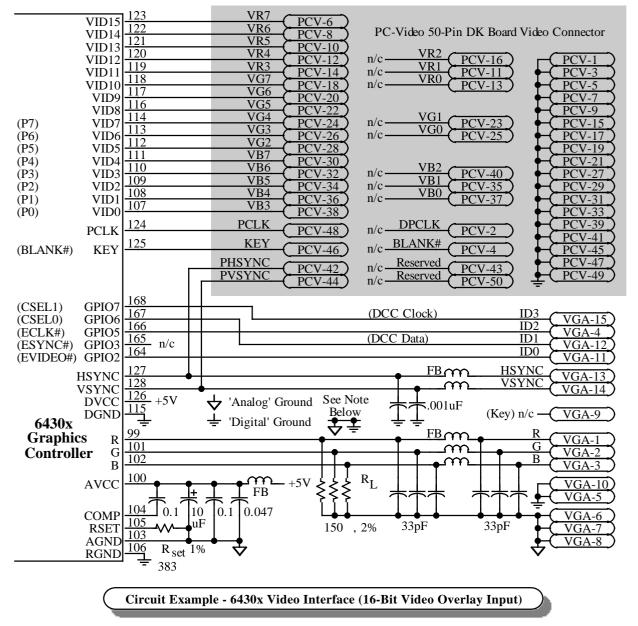

| Application Schematics<br>System Bus Interface<br>Display Memory Interface<br>Video Interface                                                                                                               | 135<br>136<br>139<br>141                      |

| Electrical Specification<br>Absolute Maximum Conditions<br>Normal Operating Conditions<br>DAC Characteristics<br>DC Characteristics<br>DC Drive Characteristics<br>AC Test Conditions<br>AC Characteristics | 143<br>143<br>143<br>143<br>144<br>144<br>144 |

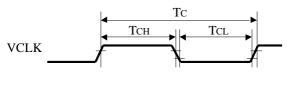

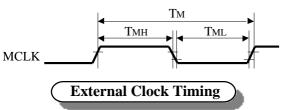

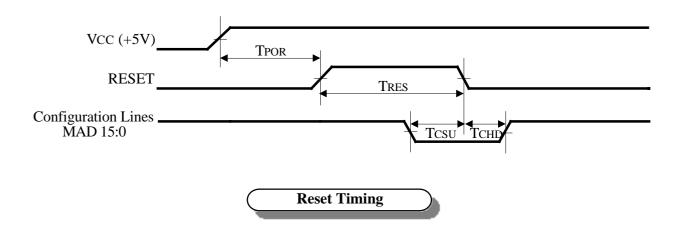

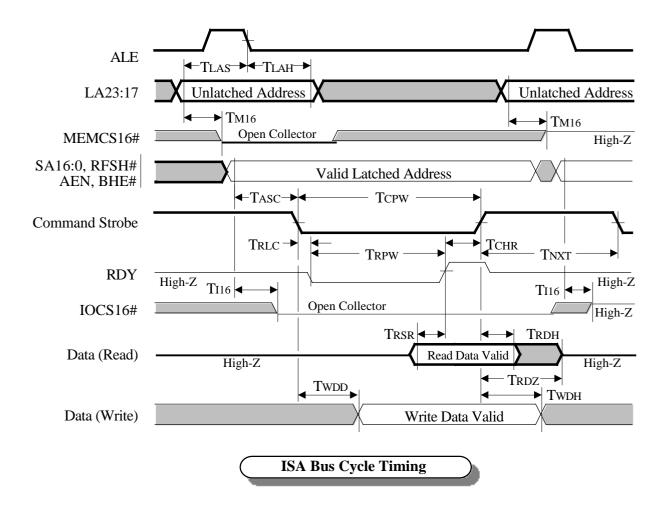

| Clock Timing<br>Reset Timing<br>ISA Bus Timing<br>DC Characteristics                                                                                                                                        | 145<br>145<br>146                             |

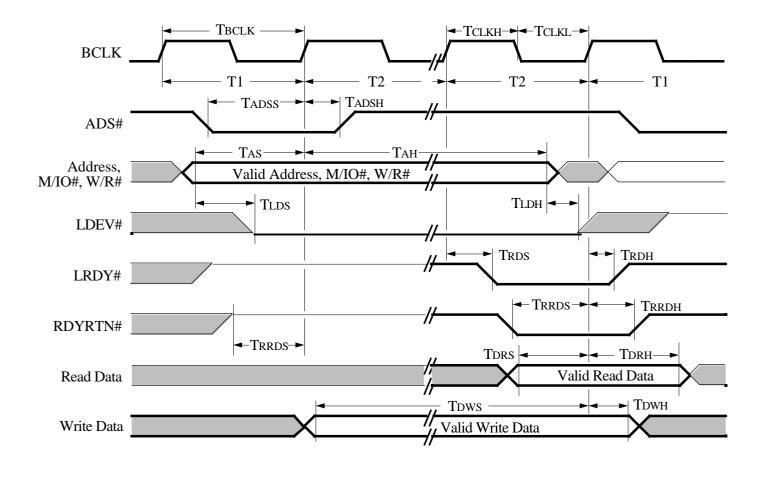

| 486 Local Bus Timing<br>AC Characteristics                                                                                                                                                                  | 148                                           |

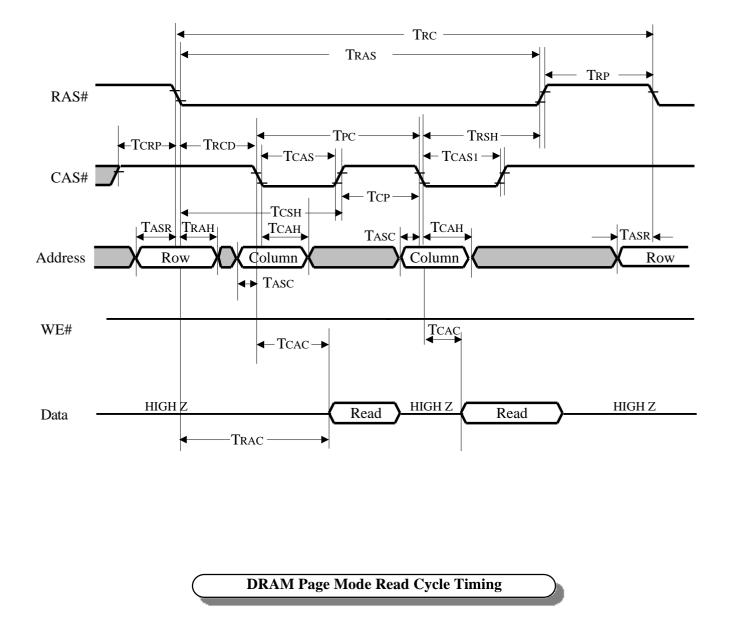

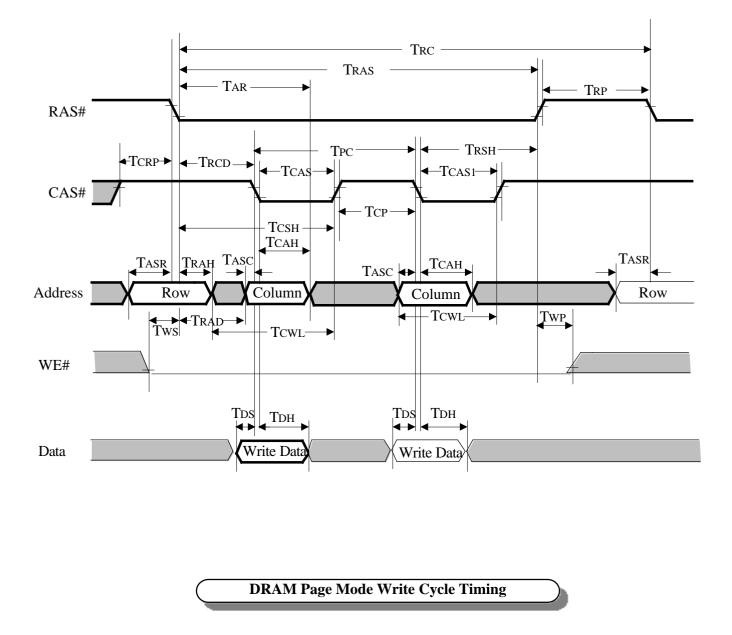

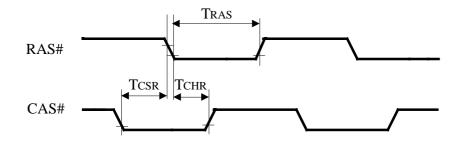

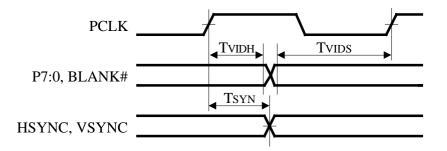

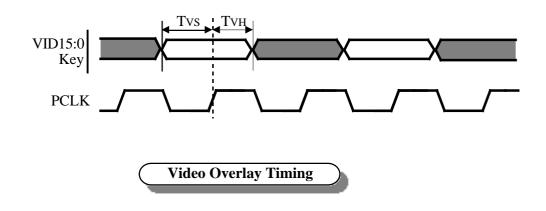

| DRAM Read/Write Timing<br>Refresh Timing<br>CRT Video Timing<br>Video Overlay Timing                                                                                                                        | 150<br>153<br>154<br>154                      |

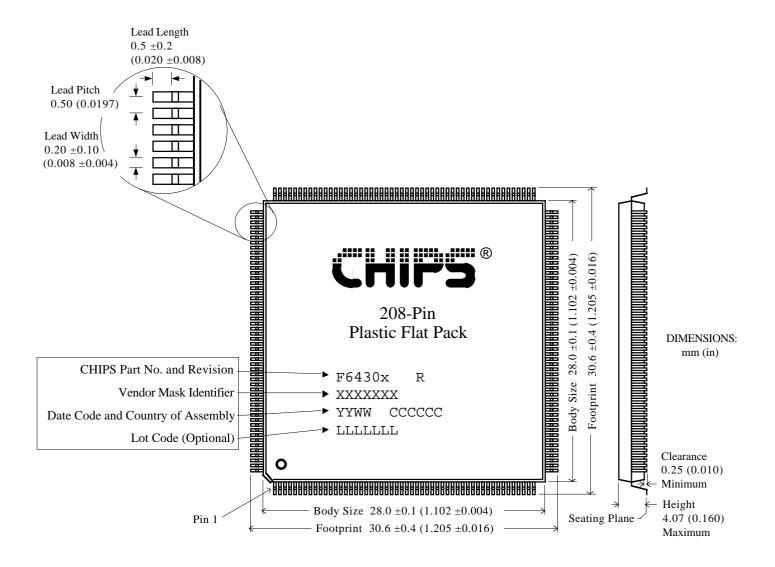

| Mechanical Specifications<br>Plastic 208-PFP Package Dimensions                                                                                                                                             | 155<br>155                                    |

# List of Figures and Tables

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>Page</u>                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| System Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                         |

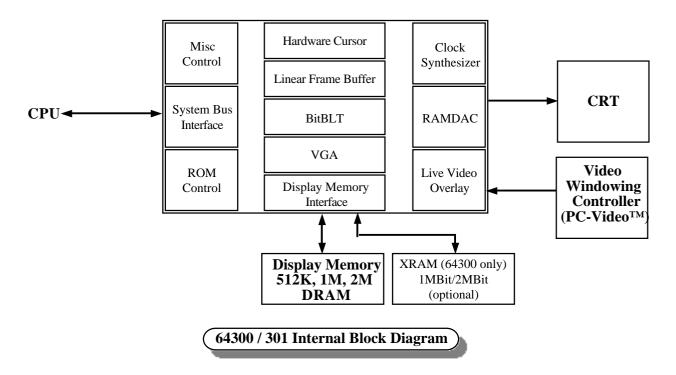

| Internal Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                         |

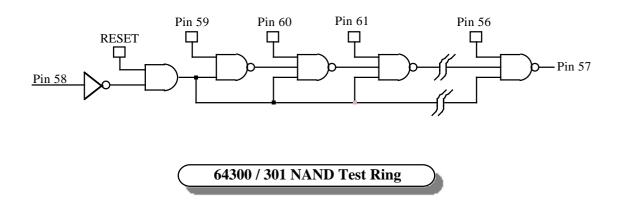

| NAND Test Ring                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                        |

| Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                                        |

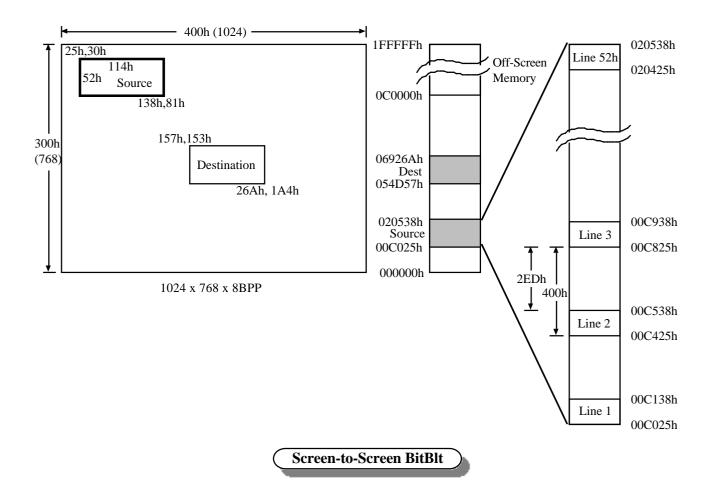

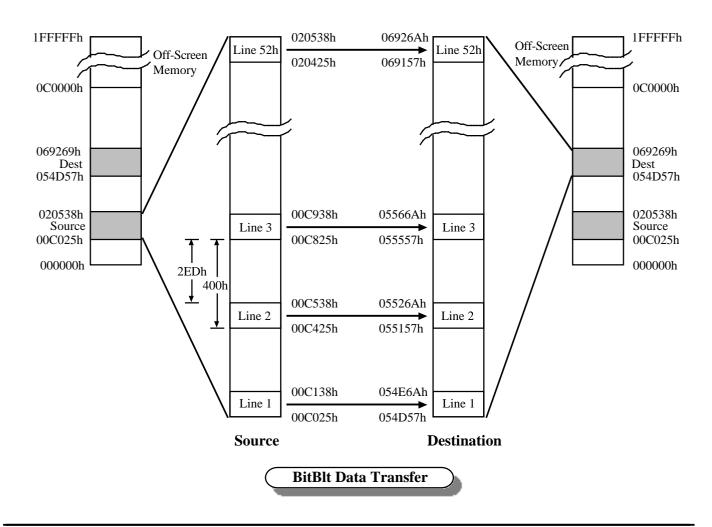

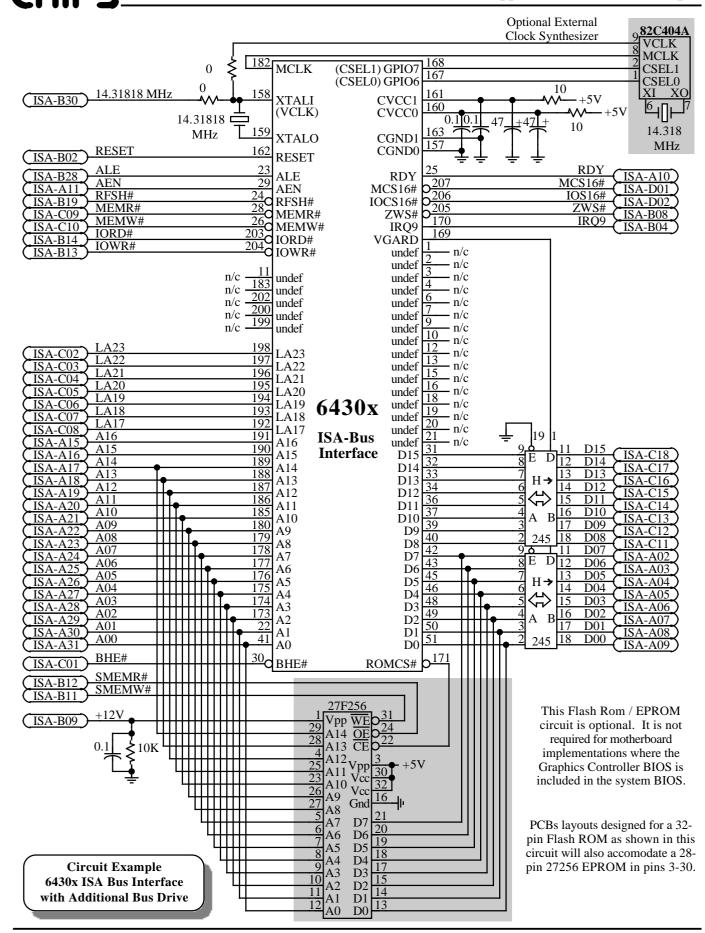

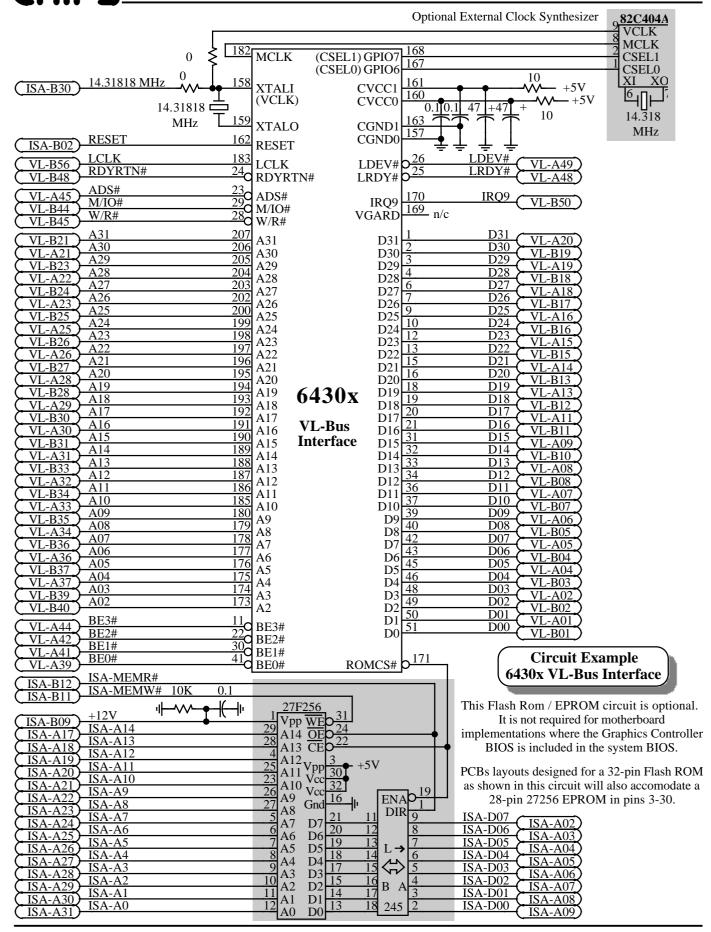

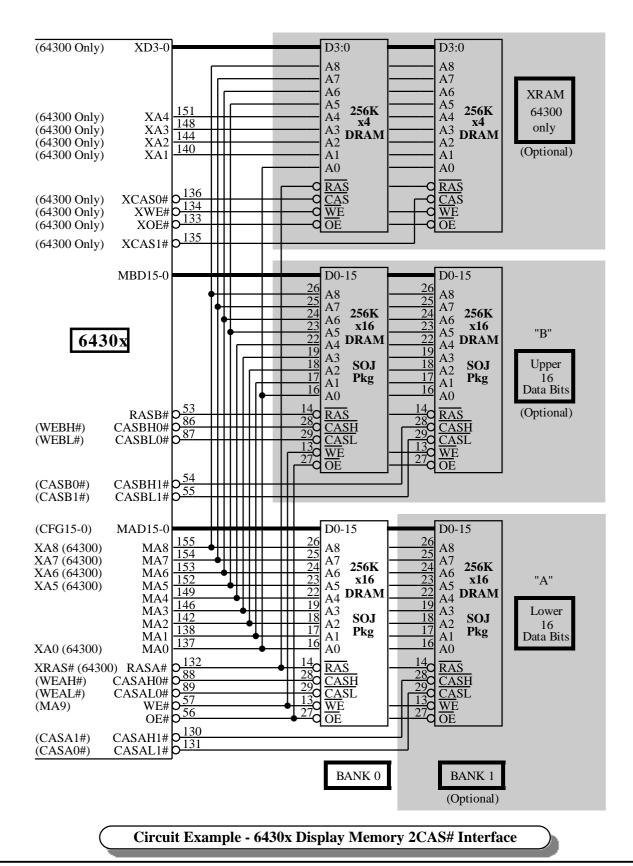

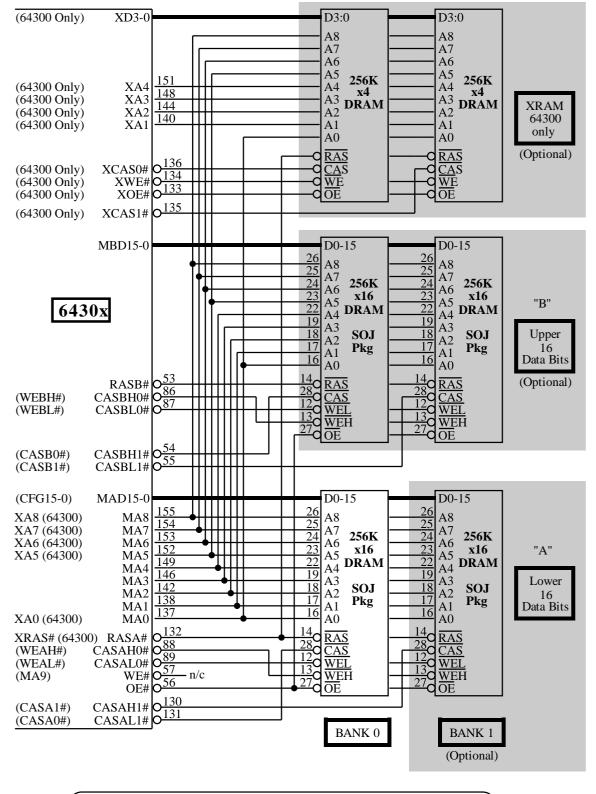

| Functional Description<br>VGA Memory Map<br>Internal RAMDAC Interface<br>Clock Register Structure<br>Typical Clock Synthesizer Block Diagram .<br>Possible BitBlt Orientations With Overlap .<br>Screen to Screen BitBlt<br>BitBlt Data Transfer<br>Differential Pitch BitBlt Data Transfer<br>Application Schematic Examples<br>ISA Bus Interface<br>ISA Bus Interface - Additional Bus Drive<br>VL Bus Interface<br>Display Memory 2-CAS# Interface<br>Display Memory 2-WE# Interface | 124<br>125<br>126<br>129<br>130<br>131<br>132<br>136<br>137<br>138<br>139 |

| Video Interface 8-Bit Output<br>Video Interface 16-Bit Input                                                                                                                                                                                                                                                                                                                                                                                                                            | 140<br>141<br>142                                                         |

| Clock Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 145                                                                       |

| Reset Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 145                                                                       |

| ISA Bus Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 147                                                                       |

| 486 Local Bus Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 149                                                                       |

| DRAM Page Mode Read Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 151                                                                       |

| DRAM Page Mode Write Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 152                                                                       |

| CAS-Before-RAS (CBR) DRAM<br>Refresh Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                       | 153                                                                       |

| CRT Video Data and Control Signal Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                | 154                                                                       |

| Video Overlay Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 154                                                                       |

| Mechanical Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 155                                                                       |

| Table                                                                 | Page |

|-----------------------------------------------------------------------|------|

| Pin Lists                                                             | 16   |

| Pin Descriptions                                                      | 20   |

| Register Summary - I/O Map                                            | 35   |

| Register Summary - CGA/MDA/Herc Modes                                 | 36   |

| Register Summary - EGA Mode                                           | 36   |

| Register Summary - VGA Mode                                           | 36   |

| Register Summary - Indexed Registers                                  | 37   |

| Register Summary - Extension Registers                                | 38   |

| Register Summary - 32-Bit Registers                                   | 41   |

| Register List - Setup Registers                                       | 45   |

| Register List - General Control & Status<br>Register List - Sequencer | 47   |

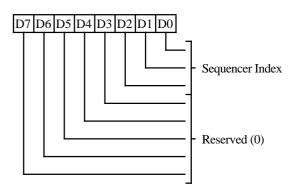

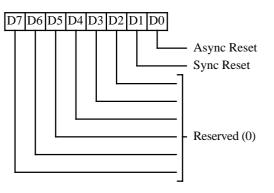

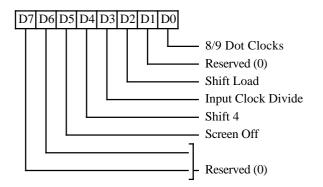

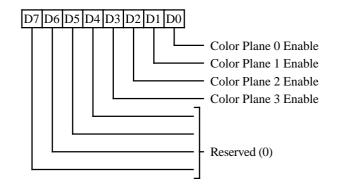

| Register List - Sequencer                                             | 49   |

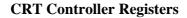

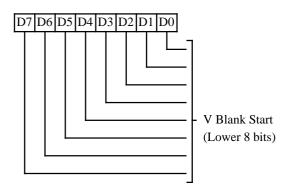

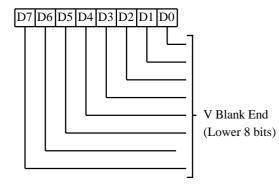

| Register List - CRT Controller                                        | 53   |

| Register List - Graphics Controller                                   | 69   |

| Register List - Attribute Controller                                  |      |

| and Color Palette                                                     | 77   |

| Register List - Extension Registers                                   | 83   |

| Register List - 32-Bit Registers                                      | 113  |

| Absolute Maximum Conditions                                           | 143  |

| Normal Operating Conditions                                           | 143  |

| DAC Characteristics                                                   | 143  |

| DC Characteristics                                                    | 144  |

| DC Drive Characteristics                                              | 144  |

| AC Test Conditions                                                    | 144  |

| AC Characteristics                                                    |      |

| Clock Timing                                                          | 145  |

| Reset Timing                                                          | 145  |

| ISA Bus Timing                                                        | 146  |

| DC Characteristics                                                    |      |

| 486 Local Bus Timing                                                  | 148  |

| AC Characteristics                                                    | 1.50 |

| DRAM Read/Write Timing                                                | 150  |

| Refresh Timing                                                        | 153  |

| CRT Video Timing                                                      | 154  |

| Video Overlay Timing                                                  | 154  |

## Introduction

The 64300 / 301 Wingine® DGX combines three powerful elements aimed at addressing the requirements of mainstream desktop PC designs: 1) state of the art techniques for optimizing performance in computer graphic intensive applications, graphical user interfaces (GUI) and operating systems, such as Windows; 2) cost saving features such as integrated palette DAC and clock synthesizer, integrated support for multiple bus interfaces and flexible DRAM-based display memory configurations; and 3) differentiating factors such as optional XRAM Accelerator Cache (64300)only), desktop computer power management, Flash ROM support, linearly mapped display memory, and Multimedia support for color key and video overlays.

### PERFORMANCE

®

### XRAM Accelerator Cache (64300 only)

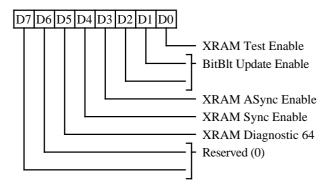

The XRAM Accelerator Cache (patent pending) is a breakthrough in performance technology. By using one standard 256Kx4 Fast Page DRAM, a proprietary algorithm implemented in the 64300 significantly increases graphics system performance. The result is performance never before achieved in standard DRAM-based graphics architectures. For added flexibility, the XRAM Accelerator Cache is optional.

### Local Bus

To address the requirement of high performance (particularly GUI environments) in while maintaining a cost effective bill of materials for the graphics system, the 64300 / 301 offers the industry's most optimized price/performance/feature mix. A variety of industry standard 32-bit local bus interfaces are integrated on chip, including: VESA Local Bus (VL-Bus), 386DX and 486SX/DX CPU buses. The key is that local bus interfaces are 32bit wide. This means full local bus performance potential is realized and no external TTL devices are required for multiplexing or demultiplexing bus signals. In addition to local bus support, ISA / EISA standard peripheral buses are also supported.

### Scalability

A benefit provided by the 64300 XRAM technology is scalability. When a system's host CPU is upgraded (e.g. from a 486DX-25 to a 486DX-33 or from a 486DX-33 to a 486DX2-66) the 64300 Wingine DGX performance will scale with the processor and a significant improvement will be observed in the display. Other DRAM-based graphics accelerators gain some degree of performance which, while measurable, is not as significant nor as noticeable on the display.

### **Acceleration Features**

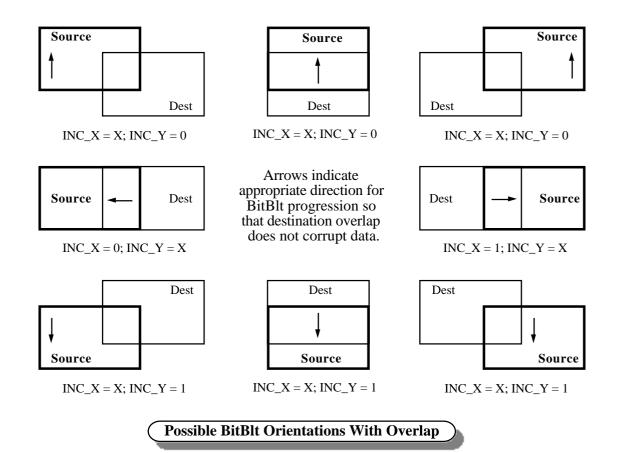

Several functions traditionally performed by software have been implemented in hardware to Three-Operand further improve performance. BITBLT logic supports all 256 logical combinations of Source, Destination and Pattern. Line drawing is accelerated with hardware А programmable-size 64x64x2 assistance. hardware cursor allows flexible cursor size and flicker free cursor display. The presence of the hardware cursor frees software from continuously generating the cursor image on the display. A 32-Bit Color Expansion engine allows the host CPU to transfer monochrome "maps" of color images over the system bus at high speeds to the 64300 / 301, which decodes the monochrome images into their color form.

For ISA implementations, the 64300 / 301 additionally supports Zero Wait State memory accesses.

### **COST OPTIMIZATION**

### **High Integration**

The 64300 / 301 integrates a Graphics Accelerator Engine together with a True-Color palette DAC and clock synthesizer. The integrated palette DAC supports 24-Bit direct color and features a 256x18 LUT. The integrated dual clock synthesizer allows full programmability of MCLK (memory clock) and PCLK (pixel clock). The integrated clock synthesizers support frequencies from 390KHz to 120MHz.

### **DRAM Display Memory**

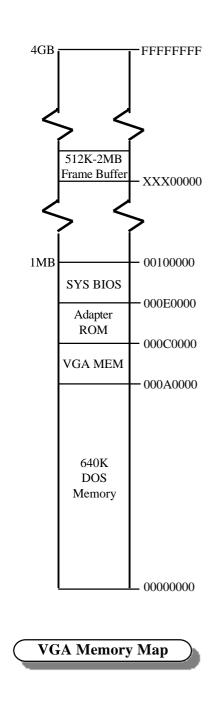

The 64300 / 301 supports from 512KB to 2MB of DRAM display memory. Both 256Kx4 and 256Kx16 Fast Page Mode DRAM organizations are supported. Display memory is linearly mapped up to 2MB, simplifying development of device drivers and optimizing driver performance.

### DIFFERENTIATING FEATURES

The 64300 / 301 True-Color GUI Accelerator permits a high degree of differentiation at low cost. For example, in the 64300 the XRAM Accelerator significantly increases performance for the price of one standard 256Kx4 DRAM (for 1MByte video memory systems). However, the ability to differentiate does not end there. The VESA display power management signalling (DPMS) standard is supported, enabling stand-by, suspend, and "off" power saving modes. Color Key and video overlay are supported for optimal Multimedia applications. Flash ROMs (PEROMs) are supported for insystem BIOS upgrades. Pinouts are optimized for PCB board layout such that a 64300 / 301 GUI accelerator design can be implemented in less than 9 square inches (5800 sq mm). Additionally, the 64300 / 301 offers integrated palette DAC and dual clock synthesizer, but also allows use of these devices externally. The package may be checked for correct insertion via its in-circuit test features.

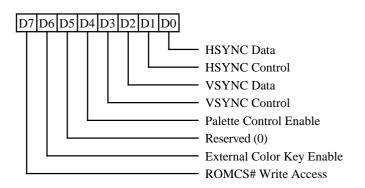

### DESKTOP POWER MANAGEMENT

The 64300 / 301 supports the VESA DPMS (Display Power Management Signalling) protocol. This includes the ability to independently stop HSYNC or VSYNC and hold them at a static level. Additionally the RAMDAC may be powered-down and the clock frequencies lowered for further power savings.

### MINIMUM CHIP COUNT / BOARD SPACE

The 64300 / 301 was designed to integrate as many functions as economically possible to minimize chip count and board space. The 64300 / 301 integrates a VGA core, True-Color palette DAC, and dual programmable clock synthesizer and employs separate address and data buses so that no external buffers are required (VL-Bus).

Using the 64300 / 301, a complete 32-bit, VGAcompatible, local bus GUI accelerator design for motherboard applications can be built with just 2 ICs, including display memory, as shown in the following bill of materials table:

| Qty | Chip Type               |

|-----|-------------------------|

| 1   | 64300 / 301 Wingine DGX |

|   | U                            |

|---|------------------------------|

| 1 | 256V w16 East Dags Made DDAM |

|   | 256Kx16 Fast Page Mode DRAM  |

|   |                              |

2 Total

For add-in board applications, external bus drivers may be required for additional signal drive and a PEROM may be required for BIOS storage. Improved performance or other optional features may require implementation of more than one memory chip. In the 64300, the XRAM Accelerator Cache option, for example, would add a single 256Kx4 Fast Page Mode DRAM to the above bill of materials.

### DISPLAY MEMORY INTERFACE

The 64300 Wingine DGX can employ multiple display memory configurations providing the OEM with flexibility to use it in several designs with differing cost and performance criteria.

The 64300 / 301 supports the following display memory configurations using Fast Page Mode DRAMs:

- One 256Kx16 DRAM (512 KBytes)

- Four 256Kx4 DRAMs (512 KBytes)

- Two 256Kx16 DRAMs (1 MByte)

- Eight 256Kx4 DRAMs (1 MByte)

- Four 256Kx16 DRAMs (2 MBytes)

- Sixteen 256Kx4 DRAMs (2 MByte)

In the 64300 performance is significantly improved when optional memory is added to support the XRAM. For 1MByte configurations one additional 256K x 4 DRAM is required. For 2MByte configurations, two 256K x 4 DRAMs are required. In all configurations the 64300 / 301 supports all standard VGA display modes.

The entire display memory (512 KBytes to 2 MBytes) is always available to the CPU in regular four-plane mode, chained two-plane mode, and super-chained one-plane mode.

Display memory control signals are derived from the memory clock (MCLK) input.

The 64300 / 301 serves as a DRAM controller for the system's display memory. It handles DRAM refresh, fetches data from display memory as required to refresh the screen, interfaces the CPU to display memory and supplies all necessary DRAM control For VGA compatibility, the display signals. memory is arranged as four planes of 64 KBytes each. Each plane is eight bits wide for a total of 32 bits. All planes share a common address bus. Each plane has a separate CAS signal and share a common write enable (except when using 256K x 16 DRAMs with 2 WE# / 1 CAS# which separates byte accesses based on WE#). Planes 0/1 and 2/3 have separate RAS signals which operate independently only when in text modes. In 2MByte configurations the second bank is a duplicate of the first with an additional set of CAS control signals.

### **CPU BUS INTERFACE**

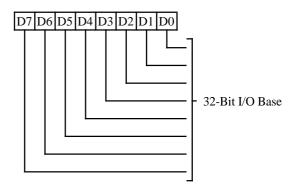

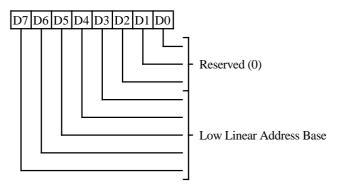

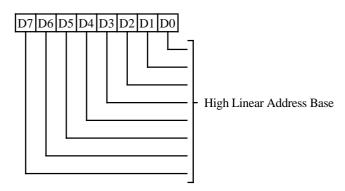

The 64300 / 301 provides on-chip support for interface to VESA Local Bus (VL-Bus), 486 SX Local Bus, 486 DX Local Bus, 386 DX Local Bus, and EISA/ISA Bus. Strap options allow the user to configure the chip for the type of interface desired. Control signals for all interface types are integrated on chip. Support is provided for 8-bit, 16-bit, and 32-bit cycles for both memory and I/O. All parameters necessary to ensure proper operation in these various environments are handled in a fashion transparent to the CPU. These include internal decoding of all memory and I/O addresses, bus width translations, and generation of the necessary control signals. In ISA/EISA bus implementations the 64300 / 301 must be placed in a 16-bit slot for proper operation. The 64300 / 301 also provides a 'linear addressing' feature which allows display memory to be accessed in any area of upper memory up to 2MB in size.

### **DISPLAY INTERFACE**

The 64300 / 301 supports high resolution fixed frequency and variable frequency analog monitors in interlaced and non-interlaced modes of operation.

The 64300 / 301 supports resolutions up to 1280x1024 pixels with 256 colors or 1024x768 pixels with 65K colors in a 2 MB display memory configuration and supports Super-VGA resolutions such as 640 x 480 16.7M colors, 800x600 65K colors, and 1024x768 256 colors in 1MB display memory configurations.

### FULL COMPATIBILITY

The 64300 / 301 is fully compatible with the IBM<sup>TM</sup> VGA standard at the hardware, register, and BIOS level. Mode initialization is supported at the BIOS and register levels, ensuring compatibility with all application software.

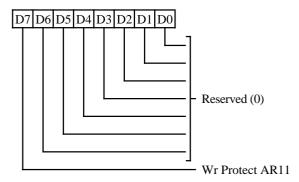

### Write Protection

The 64300 / 301 has the ability to write protect the overscan or border color for European ergonomics display requirements.

### **Extension Registers**

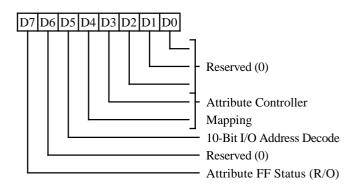

The 64300 / 301 employs an "Extension" Register set to control its enhanced features. These Extension Registers provide control of the CRT parameters for extended modes and control of the additional hardware features in the 64300 / 301. These registers are always accessible as an index/data register set at I/O port addresses 3D6-3D7h. None of the unused bits in the regular VGA registers are used for extensions. There are also 32bit registers (DRXX) which control the BitBlt engine and hardware cursor.

### **Context Switching**

For support of multi-tasking, windowing, and context switching, the state of the 64300 / 301 (internal registers) is readable and writable. This feature is fully compatible with IBM's VGA. Additional registers are provided to allow read back of internal latches not readable in the IBM VGA.

### **RESET, SETUP, AND TEST MODES**

### **Reset Mode**

When this mode is activated by pulling the RESET pin high, the 64300 / 301 is forced to VGAcompatible mode and is disabled. It must be enabled after deactivating the RESET pin by writing to the Global Enable Register (46E8h). The RESET pin must be active for at least 1.5µs for the 64300 / 301 to enter a stable state.

### Setup Mode

In this mode, only the Global Enable register is accessible.

Setup mode is entered by writing a 1 to bit-4 of port 46E8h. This port is incorporated in the 64300 / 301. While in Setup mode, the video output is active if it was active prior to entering Setup mode and inactive if it was inactive prior to entering Setup mode.

After power up, video BIOS can optionally disable the video 46E8h register (via XR70) for compatibility in case other non-IBM-compatible peripheral devices use those ports.

### **Tri-State Mode**

In this mode, most output pins of the 64300 / 301 chip may be disabled for testing of circuitry external to the chip. The 64300 / 301 will enter Tri-State mode during RESET. The 64300 / 301 will exit Tri-State mode when RESET goes inactive.

### ICT (In-Circuit Test) Mode

In this mode, pins on the 64300 / 301 chip may be tested individually to determine if they are properly connected. The 64300 / 301 will enter ICT mode when RESET is active (high) and MBD15 (pin 58) is low as shown below. In ICT mode, all digital signal pins except WE#, XA4:1 and MA4:1 become inputs which are part of a long path starting at pin 59 (MDD6) and proceeding around the chip to pin 56 (OE#). On the 64301, XWE pin 134 is a do not connect and thus is not part of the ICT test path. ICT mode tests all pins except XTALO, RED, GREEN, BLUE, COMP, RSET, XA4:1, MA4:1, LCLK, MCLK, VCC and GND. All other pins are part of a NAND ring as shown below. The result of the NAND ring is output on pin 57 (WE#). A typical test environment will place all test ring input pins at a logical high level after enabling the test ring with RESET high and MBD15 low. Pins in the test ring (starting at pin 59 and moving counterclockwise around the chip) are sequentially brought low. Upon each high to low transition, the output of the test ring (pin 57) should toggle.

Warning: This method is subject to change on future revisions of the 64300 / 301. Always refer to the most current data sheet for this device.

### CHIP ARCHITECTURE

The 64300 / 301 integrates eight major internal modules:

### Sequencer

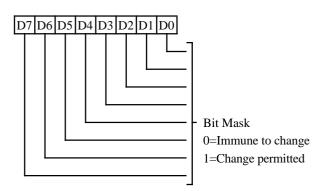

The Sequencer generates all CPU and display memory timing. It controls CPU access of display memory by inserting cycles dedicated to CPU access. It also contains mask registers which can prevent writes to individual display memory planes.

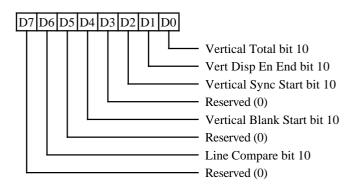

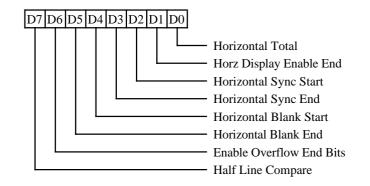

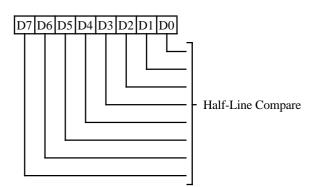

### **CRT Controller**

The CRT Controller generates all the sync and timing signals for the display and also generates the addresses used for both display refresh and CPU access of display memory.

### **Graphics Controller**

The Graphics Controller interfaces the 16 or 32-bit CPU data bus to the 32-bit internal data bus used by the four planes (Maps) of display memory. It also latches and supplies display memory data to the Attribute Controller for use in refreshing the screen image. For text modes this data is supplied in parallel form (character generator data and attribute code); for graphics modes it is converted to serial form (one bit from each of four bytes form a single pixel). The Graphics Controller can also perform any one of several types of logical operations on data while reading it from or writing it to display memory.

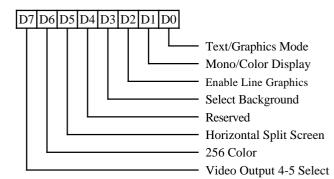

### Attribute Controller

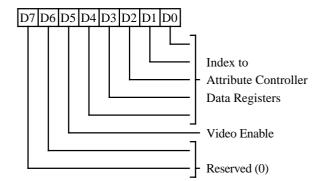

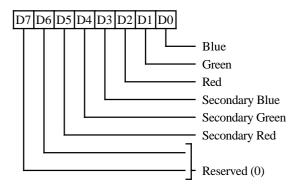

The Attribute Controller generates the 4-bit-wide VGA video data stream used to refresh the display. This is created in text modes from a font pattern and an attribute code which pass through a parallel to serial conversion. In graphics modes, the display memory contains the 4-bit pixel data. In text and 16 color graphics modes the 4-bit pixel data acts as an index into a set of 16 internal color look-up registers which generate a 6-bit color value. Two additional bits of color data are added to provide an 8-bit address to the VGA color palette. In 256color modes, two 4-bit values may be passed through the color look-up registers and assembled into one 8-bit video data value. In high-resolution 256-color modes, an 8-bit video data value may be provided directly, bypassing the attribute controller color lookup registers. Text and cursor blink, underline and horizontal scrolling are also the responsibility of the Attribute Controller.

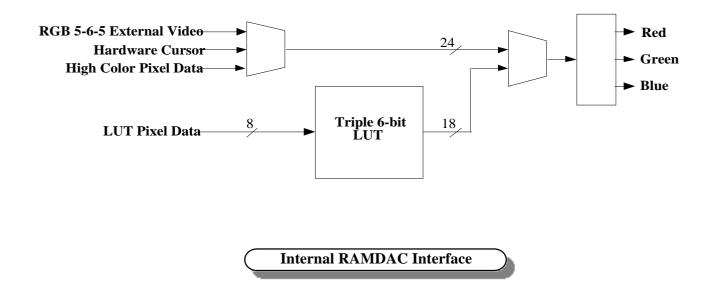

### VGA Color Palette/DAC

The 64300 / 301 integrates an industry standard VGA-compatible palette DAC for support of analog-output CRT displays.

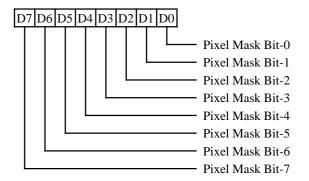

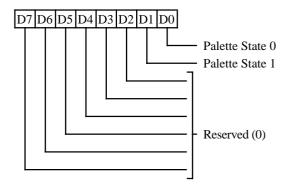

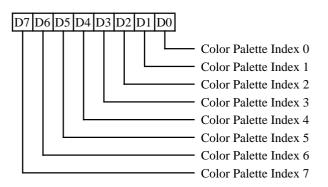

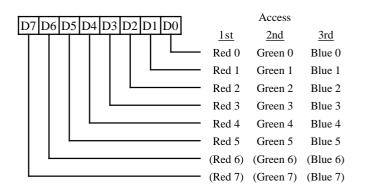

The on-board VGA color palette contains a pixel mask register, 256x18 color lookup table (LUT), and triple 8-bit DACs for driving analog CRTs directly. The 'LM339' comparator function is implemented internally to generate the SENSE signal. The voltage reference for the internal DACs is also implemented on-chip.

### True Color Support

Each DAC analog output provides 8-bit resolution (256 shades of color on each of the analog R, G, and B outputs). The internal DAC supports generation of 15 bit/pixel TARGA format (5R + 5G + 5B + 1 unused), 16 bit/pixel (5R + 6G + 5B), and 24bpp (8R + 8G + 8B) graphics output to analog CRT displays. 15bpp (also called '555' mode) is compatible with Sierra RAMDACs and 16 bpp (also called '565' mode) is compatible with XGA high-color mode.

### **BitBlt Engine**

The BitBlt engine performs a wide range of tasks in graphics modes. In its simplest form it transfers blocks of data from one area of the screen to another without CPU supervision. It is also capable of performing address generation for system to All 256 Microsoft Windows screen transfers. Raster Operations are supported. It may also be used for font and monochrome bitmap expansion to full color depth from bitmaps stored in either system memory or display memory. The BitBlt engine contains Windows compatible a monochrome or full color (8x8) pattern register and a 3-operand logical raster operation block. The BitBlt engine is controlled by a set of 32-bit wide registers.

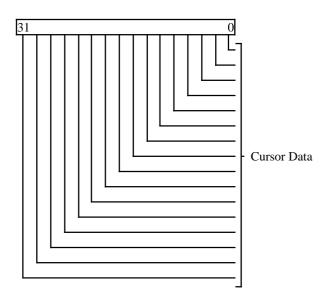

### Hardware Cursor

Hardware cursors are commonly used in windowing environments such as OS/2, X-Windows, and Microsoft Windows. The 64300 / 301 incorporates a 64x64x2 hardware cursor for support of these environments. The format is an AND plus an XOR plane which select between transparency, highlight (invert), and two user definable colors. The cursor RAM may also be divided up into quarters supporting storage for up to four cursors simultaneously. This has the advantage of allowing pseudo-dynamic cursor icons (rotating cartwheels, sand falling through an hourglass, etc.) and also eliminates the flashing which may occur when the active cursor's shape and position (hotspot) change simultaneously.

### **Clock Synthesizer**

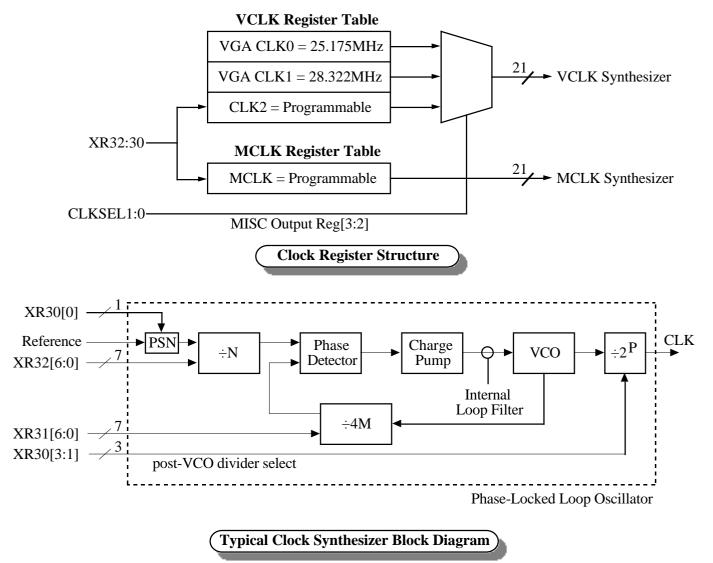

A dual programmable clock synthesizer complete with charge pumps and filters is integrated into the 64300 / 301. On reset the clock synthesizer defaults to VGA compatible values. It requires a 14.31818MHz crystal or oscillator input to generate a reference frequency. If a crystal is used it does not require other passive components externally (no additional resistors or capacitors). Both clocks are programmable to function across the full specified operating range of both PCLK and MCLK.

### **CONFIGURATION SWITCHES**

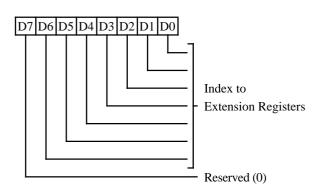

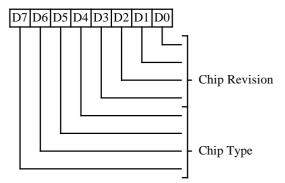

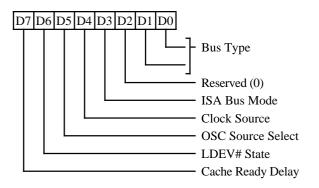

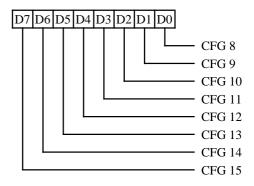

The 64300 / 301 can read up to sixteen configuration bits. These signals are sampled on memory data bus bits MAD15:0 on the falling edge of RESET. The state of MAD1:0 on RESET determines the bus interface type. MAD2 is currently undefined. In ISA interfaces MAD3 chooses between MCLK and MCLK+2 for the internal Host Clock (HCLK). MAD4 determines where the video and memory clocks are located (internal or external). If the internal clock synthesizer is selected, MAD5 determines if the reference is connected to a crystal or TTL oscillator input. MAD6 determines if the local bus controller expects a tri-state LDEV# signal or a straight unlatched decode. In VL-Bus mode MAD7 determines if the cache controller owns the RDY# signal during the first T2 of a local bus cycle. In ISA bus mode MAD7 chooses between an external HCLK or internal HCLK (see MAD3). All eight bits of the lower configuration byte (on MAD7:0) are latched into an extension register (XR01) on RESET so software may determine the hardware configuration.

A second configuration byte is latched on reset from MAD15:8 and may be read in XR74. These bits have no internal hardware function and may be used for any desired purpose by software.

Memory data lines MAD15:0 for the corresponding bits must be externally connected to 47K pullups or pulldowns (or driven to the desired 0 or 1 level while RESET is high) so that they may be latched on the falling edge of RESET. The 64300 / 301 does not implement pullup or pulldown resistors on these pins internally.

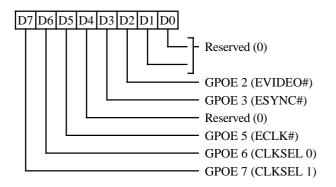

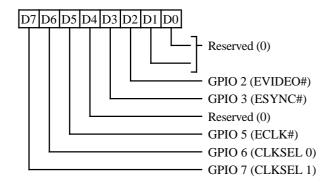

### GENERAL PURPOSE I/O

There are five general purpose I/O (GPIO) pins which are controlled via XR71 and XR72. Several of these pins are multiplexed with optional functions such as external clock synthesizer and feature connector support. If these features are not used then the corresponding pins may become user definable I/O pins. Additional features can be added to the 64300 / 301 by using these pins. These features include; reading the IBM monitor ID bits, controlling the programming voltage on a Flash ROM device, or as an interface to a serial Non-Volatile Memory (EEPROM).

### **CLOCK SELECTION**

The 64300 / 301 will typically be configured to use its internal clock synthesizer. On RESET the internal MCLK is set to 60MHz. A 60MHz MCLK is within the operational specification for 80ns DRAMs and is high enough to operate all standard VGA modes. The fixed Video CLK registers (Video CLK selects 0 and 1) are set as close as possible to the standard VGA frequencies (25.175MHz and 28.322MHz). These are the required frequencies for VGA compatible designs. The CLKSEL1:0 bits in the MISC Status Register are also cleared on RESET thus selecting Video CLK0 (25.175MHz). The internal clock synthesizer accepts either a TTL 14.31818MHz oscillator input on XTAL IN or a 14.31818MHz crystal on its XTAL IN / XTAL OUT pins. The internal clocks may be programmed to within 0.5% of any frequency between 10MHz and 80MHz. Standard video frequencies in this range are achieved to within the VESA recommended accuracy.

If an external clock synthesizer is used (e.g. 82C404C) the pixel clock is input on XTAL IN; the memory clock on MCLK.

The MCLK frequency is dependent upon the access speed of the DRAMs connected to the 64300 / 301. DRAM's with access times of 60ns are matched with an MCLK frequency of approximately 72MHz. The maximum video data rate for a given

#

MCLK frequency is approximately 1.2x (Bytes/sec). Hence the maximum video data rate for 60ns DRAMs is about 90MBytes/sec.

### **BIOS ROM INTERFACE**

The video BIOS is implemented as an 8-bit (32Kx8) ROM. Typically a system will shadow the BIOS in system memory and thus it will only be read at boot time.

In all ISA and VL-Bus add-on cards the video BIOS is physically on the card and the BIOS ROM requires a buffer to drive its data onto the bus. For ISA bus designs the 64300 / 301 generates control signals for the BIOS and turns on its external drivers. In VL-Bus add-in card designs the 64300 / 301 does not respond to BIOS accesses on the VL-Bus (no DEVSEL# is issued). Rather, the 64300 / 301 monitors accesses on the VL-Bus and performs the transfers across the ISA bus. This allows byte alignment translation to occur in the system logic interface rather than requiring four transceivers on the VL-Bus card. For implementation information refer to the circuit examples in the Application Schematics section.

In all motherboard direct processor interfaces it is presumed that the video BIOS is part of the system BIOS.

Chips and Technologies, Inc. supplies a video BIOS optimized for 64300 / 301 hardware. The BIOS supports the extended functions of the 64300 / 301, such as extended resolution modes. It is DPMS compatible and supports the VESA 'Super VGA' BIOS mode extensions. The BIOS Modification Program (BMP) enables OEMs to tailor their feature set by programming the extended functions. CHIPS offers the BIOS as a standard production version, a customized version, or as source code.

### FLEXIBLE ARCHITECTURE

The 64300 / 301's flexible architecture enables OEMs to differentiate their products with enhanced features. OEMs can design one VGA sub-system and implement a wide range of features by selecting the display memory configuration, the XRAM accelerator option, and a live video overlay option. A single VGA sub-system design can provide:

- Lowest cost: use one 256Kx16 DRAM (512 KBytes) for a minimum VGA subsystem

- Standard Performance 1MByte subsystem: use two 256Kx16 DRAMs

- Highest Performance 1MByte DRAM system: use two 256Kx16 DRAMs plus a single 256Kx4 DRAM for XRAM acceleration

- Extended Resolution: use four 256Kx16 DRAMs plus two 256Kx4 DRAMs for acceleration

- Add live video via RGB 5-6-5 synchronized live video window (CHIPS 69001 PC-Video<sup>TM</sup>)

The 64300 / 301 is an excellent option for main system motherboards which must support a wide range of processor performance. The 64300, with its XRAM option, provides a scalability not available from any other DRAM based video controller.

### PACKAGE

The 64300 / 301 is available in a 208-pin plastic flat pack (PFP).

### **APPLICATION SCHEMATIC EXAMPLES**

Included in this document are the following application schematic examples:

- 1. Bus Interface: 16-bit EISA/ISA Bus Bus Interface: 32-bit VL Bus

- 2. Memory Interface: 1, 2, 4 256Kx16 DRAMs 2-CAS# Memory Interface: 1, 2, 4 256Kx16 DRAMs 2-WE#

- 3. CRT/Video Interface: 8-bit Video Output CRT/Video Interface: 16-bit Video Output

### **Pin List - Bus Interface**

| <u>Pin #</u> | Type     | <u>PU</u> | <u>Іон</u> | Iol | Load | <u>VL Bus</u> | <u>386 DX</u> | ISA Bus      |

|--------------|----------|-----------|------------|-----|------|---------------|---------------|--------------|

| 183          | In       |           |            |     |      | LCLK          | CLK2X         |              |

| 162          | In       |           |            |     |      | RESET         | RESET         | RESET        |

| 102          |          |           |            |     |      |               |               |              |

| 169          | I/O      |           | -4         | 4   | 50   | VGARD         | VGARD         | VGARD        |

| 171          | Ī/O      |           | -4         | 4   | 50   | ROMCS#        | CRESET        | ROMCS#       |

| 170          | Ī/O      |           | -12        | 12  | 50   | IRQ9          | IRQ9          | IRQ9         |

|              |          |           |            |     |      |               |               | <b>X</b> '   |

| 26           | I/O      |           | -8         | 8   | 50   | LDEV#         | LDEV#         | MEMW#        |

| 25           | I/O      |           | -12        | 12  | 50   | LRDY#         | LRDY#         | RDY          |

| 24           | In       |           |            |     |      | RDYRTN#       | RDYRTN#       | RFSH#        |

| 28           | In       |           |            |     |      | W/R#          | W/R#          | MEMR#        |

| 29           | In       |           | -8         | 8   | 50   | M/IO#         | M/IO#         | AEN          |

| 23           | In       |           |            |     |      | ADS#          | ADS#          | ALE          |

|              |          |           |            |     |      |               |               |              |

| 30           | In       |           | —          |     |      | BE1#          | BE1#          | BHE#         |

| 11           | In       |           |            |     |      | BE3#          | BE3#          |              |

| 41           | In       |           |            |     |      | BE0#          | BE0#          | AO           |

| 22           | In       |           |            |     |      | BE2#          | BE2#          | A1           |

| 173          | In       |           |            |     |      | A2            | A2            | A2           |

| 174          | In       |           |            |     |      | A3            | A3            | A3           |

| 175          | In       |           |            |     |      | A4            | A4            | A4           |

| 176          | In       |           |            |     |      | A5            | A5            | A5           |

| 177          | In       |           |            |     |      | A6            | A6            | A6           |

| 178          | In       |           |            |     |      | A7            | A7            | A7           |

| 179          | In       |           |            |     |      | A8            | A8            | A8           |

| 180<br>185   | In       |           |            |     |      | A9<br>A10     | A9<br>A10     | A9<br>A10    |

| 185          | In<br>In |           |            |     |      | A10<br>A11    | A10<br>A11    | A10<br>A11   |

| 180          | In       |           |            |     |      | All<br>Al2    | A11<br>A12    | A11<br>A12   |

| 187          | In       |           |            |     |      | A12<br>A13    | A12<br>A13    | A12<br>A13   |

| 188          | In       |           |            |     |      | A13<br>A14    | A13           | A13<br>A14   |

| 190          | In       |           |            |     |      | A14<br>A15    | A14<br>A15    | A14<br>A15   |

| 190          | In       |           |            |     |      | A15<br>A16    | A15           | A16          |

| 192          | In       |           |            |     |      | A17           | A10<br>A17    | LA17         |

| 192          | In       |           |            |     |      | A17<br>A18    | A17<br>A18    | LA17<br>LA18 |

| 193          | In       |           |            |     |      | A19           | A19           | LA19         |

| 195          | In       |           |            |     |      | A20           | A20           | LA19<br>LA20 |

| 196          | In       |           |            |     |      | A21           | A21           | LA21         |

| 197          | In       |           |            |     |      | A22           | A22           | LA22         |

| 198          | In       |           |            |     |      | A23           | A23           | LA23         |

| 199          | In       |           |            |     |      | A24           | A24           |              |

| 200          | In       |           |            |     |      | A25           | A25           |              |

|              |          |           |            |     |      |               |               |              |

| 202          | In       |           |            |     |      | A26           | A26           |              |

| 203          | In       |           |            |     |      | A27           | A27           | IORD#        |

| 204          | In       |           |            |     |      | A28           | A28           | IOWR#        |

| 205          | I/O      |           | -12        | 12  | 50   | A29           | A29           | ZWS#         |

| 206          | I/O      |           | -12        | 12  | 50   | A30           | A30           | IOCS16#      |

| 207          | I/O      |           | -12        | 12  | 50   | A31           | A31           | MCS16#       |

Note: IOL/IOH are specified in mA; Load is specified in pF; • in 'PU' column indicates high value (50K ) internal pullup at RESET

### **Pin List - Bus Interface**

| Pin # | Type       | <u>PU</u> | <u>Іон</u>               | Iol | Load | <u>VL Bus</u> <u>386 DX</u> |            | ISA Bus |

|-------|------------|-----------|--------------------------|-----|------|-----------------------------|------------|---------|

| 51    | I/O        |           | -8                       | 8   | 50   | D0                          | D0         | D0      |

| 50    | I/O        |           | -8                       | 8   | 50   | D1                          | D1         | D1      |

| 49    | I/O        |           | -8                       | 8   | 50   | D2                          | D2         | D2      |

| 48    | I/O        |           | -8                       | 8   | 50   | D3                          | D3         | D3      |

| 46    | I/O        |           | -8                       | 8   | 50   | D4                          | D4         | D4      |

| 45    | I/O        |           | -8                       | 8   | 50   | D5                          | D5         | D5      |

| 43    | I/O        |           | -8                       | 8   | 50   | D6                          | D6         | D6      |

| 42    | I/O        |           |                          | 8   | 50   | D7                          | D7         | D7      |

| 40    | I/O        |           | -8                       | 8   | 50   | D8                          | D8         | D8      |

| 39    | I/O        |           | -8                       | 8   | 50   | D9                          | D9         | D9      |

| 37    | I/O        |           | -8                       | 8   | 50   | D10                         | D10        | D10     |

| 36    | I/O        |           | -8                       | 8   | 50   | D11                         | D11        | D11     |

| 34    | I/O        |           | -8                       | 8   | 50   | D12                         | D12        | D12     |

| 33    | I/O        |           | -8                       | 8   | 50   | D13                         | D13        | D13     |

| 32    | I/O        |           | - <u>8</u><br>- <u>8</u> | 8   | 50   | D14                         | D14        | D14     |

| 31    | I/O        |           | -8                       | 8   | 50   | D15                         | D15        | D15     |

| 21    | I/O        |           | -8                       | 8   | 50   | D16                         | D16        |         |

| 20    | I/O<br>I/O |           | -8                       | 8   | 50   | D10                         | D10        |         |

| 19    | I/O<br>I/O |           | -8                       | 8   | 50   | D17<br>D18                  | D17        |         |

| 19    | I/O<br>I/O |           | -8                       | 8   | 50   | D18<br>D19                  | D18<br>D19 |         |

|       | I/O<br>I/O |           | -8                       | 8   | 50   |                             |            |         |

| 16    |            |           | -8                       | 8   |      | D20                         | D20        |         |

| 15    | I/O        |           | -8                       |     | 50   | D21                         | D21        |         |

| 13    | I/O        |           | -8                       | 8   | 50   | D22                         | D22        |         |

| 12    | I/O        |           | -8                       | 8   | 50   | D23                         | D23        |         |

| 10    | I/O        |           | -8                       | 8   | 50   | D24                         | D24        |         |

| 9     | I/O        |           | -8                       | 8   | 50   | D25                         | D25        | —       |

| 7     | I/O        |           | -8                       | 8   | 50   | D26                         | D26        |         |

| 6     | I/O        |           | -8                       | 8   | 50   | D27                         | D27        |         |

| 4     | I/O        |           | -8                       | 8   | 50   | D28                         | D28        |         |

| 3     | I/O        |           | -8                       | 8   | 50   | D29                         | D29        |         |

| 2     | I/O        |           | -8                       | 8   | 50   | D30                         | D30        |         |

| 1     | I/O        |           | -8                       | 8   | 50   | D31                         | D31        |         |

Note: IOL/IOH are specified in mA; Load is specified in pF; • in 'PU' column indicates high value (50K) internal pullup at RESET

### **Pin List - Display Memory Interface**

|            | Type       |        |            |                 |          | <b>Function</b>    | Alt        | <b>Pin</b> # | Туре       | PU | <u>Іон</u>      | Iol | Load     | <b>Function</b> | Alt   |

|------------|------------|--------|------------|-----------------|----------|--------------------|------------|--------------|------------|----|-----------------|-----|----------|-----------------|-------|

| 137        | Out        |        | -8         | 8               | 50       | MA0                | XA0        | 97           | I/O        |    | _4              | 4   | 50       | MAD0            | CFG0  |

| 138        | Out        |        | -16        | 16              | 50       | MA1                |            | 96           | I/O        |    | _4              | 4   | 50       | MAD1            | CFG1  |

| 142        | Out        |        | -16        | 16              | 50       | MA2                |            | 95           | I/O        |    | _4              | 4   | 50       | MAD2            | CFG2  |

| 146        | Out        |        | -16        | 16              | 50       | MA3                |            | 94           | I/O        |    | _4              | 4   | 50       | MAD3            | CFG3  |

| 149        | Out        |        | -16        | 16              | 50       | MA4                |            | 93           | I/O        |    | _4              | 4   | 50       | MAD4            | CFG4  |

| 152        | Out        |        | -8         | 8               | 50       | MA5                | XA5        | 92           | I/O        |    | _4              | 4   | 50       | MAD5            | CFG5  |

| 153        | Out        |        | -8         | 8               | 50       | MA6                | XA6        | 91           | I/O        |    | _4              | 4   | 50       | MAD6            | CFG6  |

| 154<br>155 | Out<br>Out |        | 8<br>8     | <u>8</u><br>8   | 50<br>50 | MA7<br>MA8         | XA7<br>XA8 | 90           | I/O        |    | _4              | 4   | 50       | MAD7            | CFG7  |

|            |            |        |            |                 |          |                    |            | 85           | I/O        |    | _4              | 4   | 50       | MAD8            | CFG8  |

| 132        | Out        | 1      | -8         | 8               | 50       | RASA#              | XRAS#      | 84           | I/O        |    | _4              | 4   | 50       | MAD9            | CFG9  |

| 53         | Out        | 1      | -8         | 8               | 50       | RASB#              |            | 83           | I/O        |    | _4              | 4   | 50       | MAD10           | CFG10 |

| 89         | Out        |        | -12        | 12              | 50       | CASAL0#            |            | 82           | I/O        |    | -4              | 4   | 50       | MAD11           | CFG11 |

| 88         | Out        |        | -12        | 12              | 50       | CASAH0#            |            | 81           | I/O        |    | _4              | 4   | 50       | MAD12           | CFG12 |

| 87         | Out        |        | -12        | 12              | 50       | CASBL0#            | WEBL#      | 79           | I/O        |    | _4              | 4   | 50       | MAD13           | CFG13 |

| 86<br>131  | Out<br>Out |        | -12<br>-12 | 12<br>12        | 50<br>50 | CASBH0#            |            | 78           | I/O        |    | _4              | 4   | 50       | MAD14           | CFG14 |

| 131        | Out        |        | -12 $-12$  | $\frac{12}{12}$ |          | CASAL1#<br>CASAH1# | CASA0#     | 76           | I/O        |    | _4              | 4   | 50       | MAD15           | CFG15 |

| 55         | Out        |        | -12 $-12$  | $\frac{12}{12}$ | 50       | CASBL1#            | CASR1#     | 75           | I/O        |    | _4              | 4   | 50       | MBD0            |       |

| 54         | Out        |        | -12        | $\frac{12}{12}$ | 50       | CASBH1#            |            | 74           | I/O        |    | -4              | 4   | 50       | MBD0<br>MBD1    |       |

|            |            |        |            |                 |          |                    |            | 73           | I/O        |    | -4              | 4   | 50       | MBD1<br>MBD2    |       |

| 57         | Out        |        | -12        | 12              | 50       | WE#                | MA9        | 72           | I/O        |    | _4              | 4   | 50       | MBD2<br>MBD3    |       |

| 56         | Out        |        | -12        | 12              | 50       | OE#                |            | 71           | I/O        |    | _4              | 4   | 50       | MBD4            |       |

| 140        | Out        |        | -16        | 16              | 50       | XA1                |            | 70           | I/O        |    | _4              | 4   | 50       | MBD5            |       |

| 144        | Out        |        | -16        | 16              | 50       | XA2                |            | 69           | I/O        |    | _4              | 4   | 50       | MBD6            |       |

| 148        | Out        |        | -16        | 16              | 50       | XA3                |            | 68           | I/O        |    | -4              | 4   | 50       | MBD7            |       |

| 151        | Out        |        | -16        | 16              | 50       | XA4                |            | 67           | I/O        |    | _4              | 4   | 50       | MBD8            |       |

| 136        | Out        |        | _4         | 4               | 50       | XCAS0#             |            | 65           | I/O        |    | 4<br>4          | 4   | 50       | MBD9            |       |

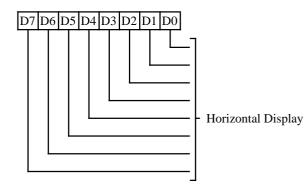

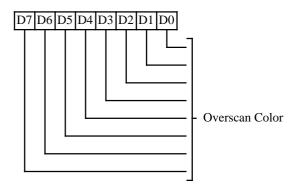

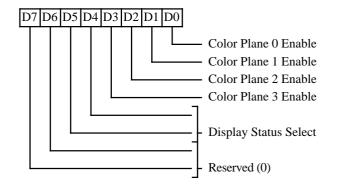

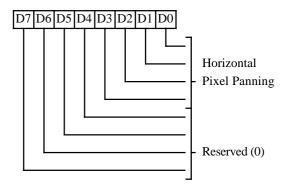

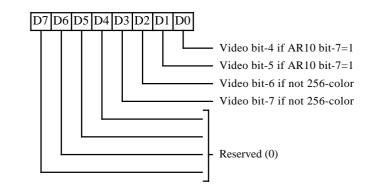

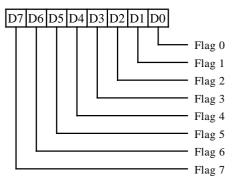

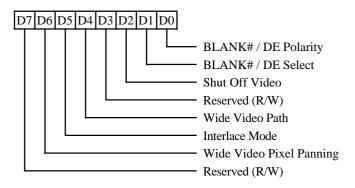

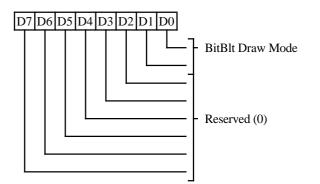

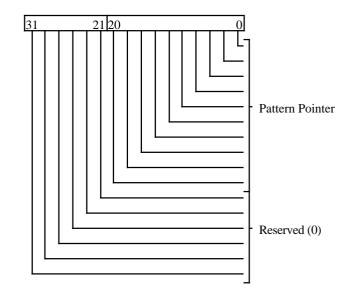

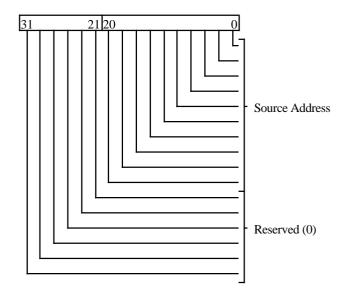

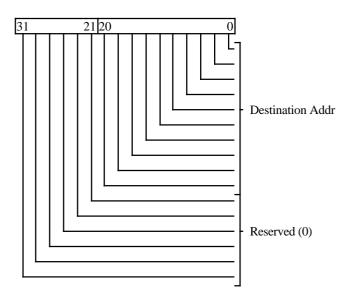

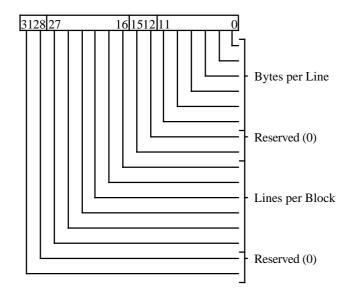

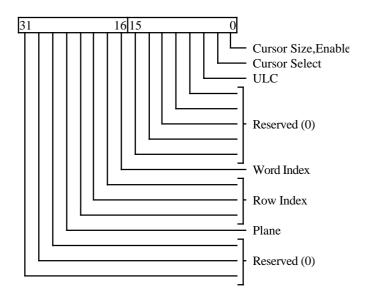

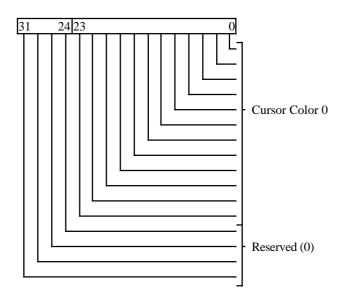

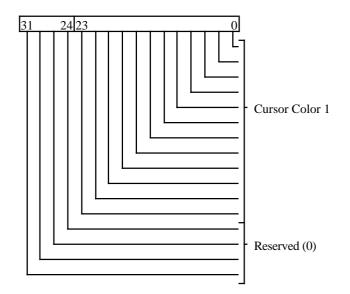

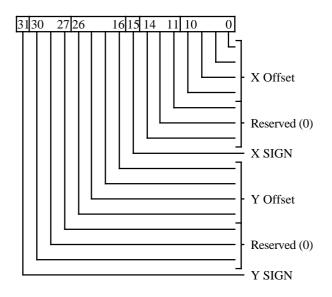

| 135        | Out        | 1      | _4         | 4               | 50       | XCAS1#             |            | 64<br>62     | I/O<br>I/O |    | <u>-4</u><br>-4 | 4   | 50<br>50 | MBD10<br>MBD11  |       |