# 82C431/82C432A/82C433/82C434A CS8240: ENHANCED GRAPHICS CHIPSet\*\*

- 100% hardware and software compatible to IBM™ Enhanced Graphics Adapter card

- Supports IBM Color Graphics and Monoohrome adapters, and Hércules™ Graphics modes

- Bit mapped graphics in four planes

- 640 × 350 resolution for IBM Enhanced Color Display

- Light pen interface

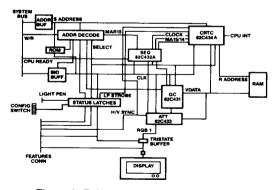

The Enhanced Graphics CHIPSet offers a complete solution for implementing an IBM Enhanced Graphics Adapter compatible controller. The chip set provides a highly integrated solution, allowing a complete Enhanced Graphics control implementation using 32 chips, including 256K byte of display memory.

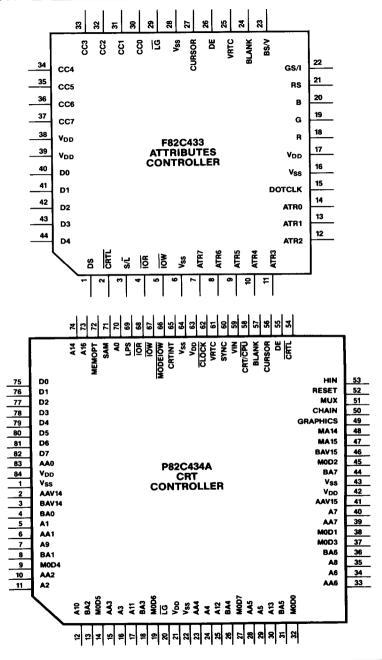

The chip set consists of the 82C431 Graphics Controller, 82C432A Sequencer, 82C433 Attributes Controller and 82C434A CRT Controller. The chip set supports color and monochrome direct drive displays in various modes. Other features include bit mapped graphics, light pen interface, and RAM loadable character generator. The chip set supports alphanumeric (AN) and all-points-addressable (APA) graphics modes, including all modes supported by the IBM Monochrome Display and Color/Graphics

- Full 16 color support in 640 × 200 and 320 × 200 pixels for IBM Color Display

- Supports 720 × 350 pixels for IBM Monochrome Displays

- Supports 640 × 400 pixels for 400-line displays

- Soft scrolls, Pans and Windows through a 1M-pixels memory

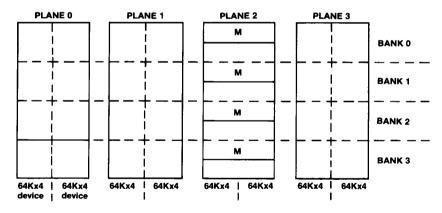

- Supports 256K bytes of memory using 64K × 4 DRAMs

Adapters. Additionally, other modes provide 720  $\times$  350 pixels support for the IBM Monochrome Display. It also provides full 16 color support for 320  $\times$  200 pixel and 640  $\times$  200 pixel resolutions for the IBM color display. The IBM Enhanced Color Display is supported with AN and APA graphics with a resolution of 640  $\times$  400 (200-line double scan) mode for 400-line monitors.

The 82C432A and 82C434A are upgraded versions of 82C432 and 82C434 respectively. The 82C432A and 82C434A are fully compatible to the 82C432 and 82C434 respectively.

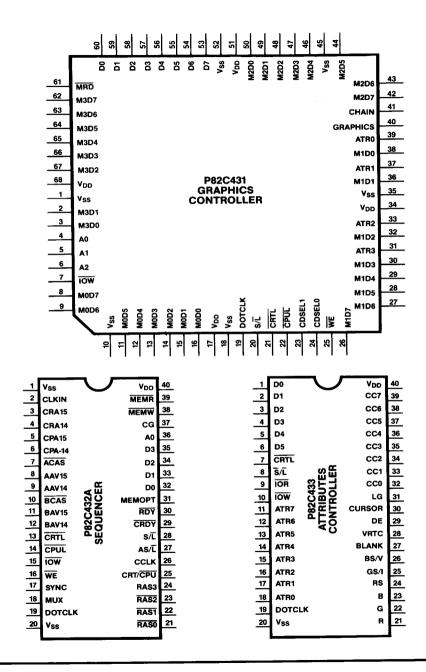

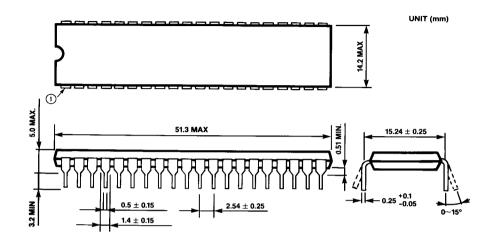

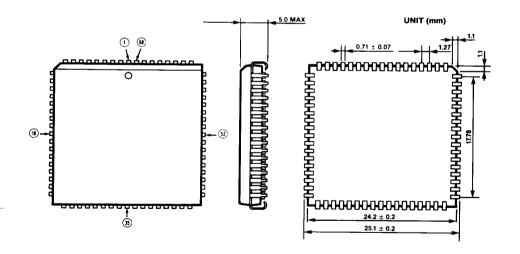

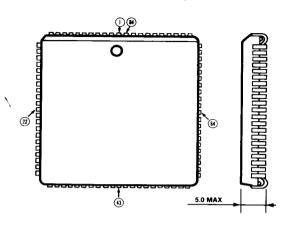

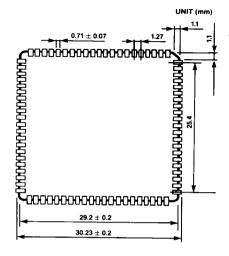

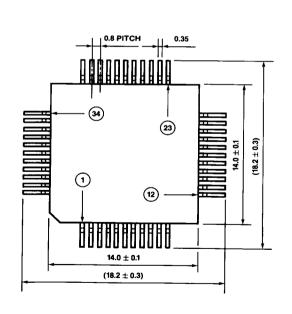

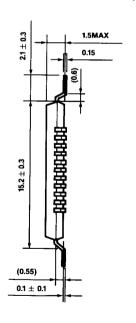

The 82C431 is packaged in 68-pin Plastic Leaded Chip Carrier (PLCC), 82C432A and 82C433 in 40-pin DIPs and 44-pin PFPs, and 82C434A in 84-pin PLCC.

Figure 1. Enhanced Graphics Controller

# 82C431 Pin Description

| Pin No.               | Pin<br>Type | Symbol    | Description                                                                                                                                                                                                                                                                                                                                               |  |

|-----------------------|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 60-53                 | 1/0         | D0-D7     | CPU data bus pins are bidirectional tri-state signals. They are used to load data into the 82C431. The data bus is also used to send/receive data to/from the display memory.                                                                                                                                                                             |  |

| 16-11 }<br>9-8        | 1/0         | M0D0-M0D7 | Memory data buses M0D0-M0D7, M1D0-M1D7, M2D0-<br>M2D7 and M3D0-M3D7 are memory data buses used                                                                                                                                                                                                                                                            |  |

| 38, 36, 32 }<br>30-26 |             | M1D0-M1D7 | to send and receive data to/from the display memory. These buses are bidirectional tri-state pins.                                                                                                                                                                                                                                                        |  |

| 50-46 }<br>44-42 }    |             | M2D0-M2D7 | state pins.                                                                                                                                                                                                                                                                                                                                               |  |

| 3, 2<br>67-62 }       |             | M3D0-M3D7 |                                                                                                                                                                                                                                                                                                                                                           |  |

| 22                    | ı           | CPUL      | CPU Latch is active low input. It is generated by the 82C432A Sequencer. When active the display memory data will be read into the graphics controller. The low-to-high going edge of this signal along with MRD active will output the data onto the data bus D0-D7 for a CPU memory read operation.                                                     |  |

| 21                    | ı           | CRTL      | CRT Latch is an active low input. It is generated by the 82C432A Sequencer. When active the display memory graphics data will be loaded into the graphics controller on the low-to-high going edge. The data on the display memory should meet the se up and hold requirements. The data loaded is transferred into the Shifter register when S/L is low. |  |

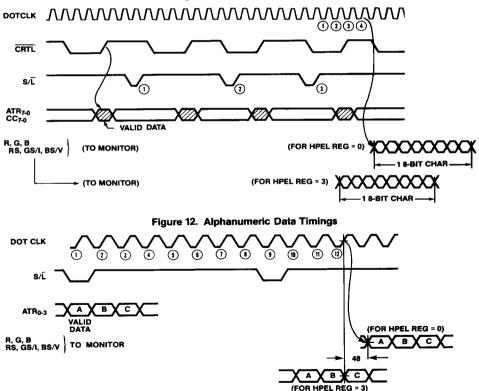

| 19                    | 1           | DOTCLK    | Dot Clock is used by the graphics controller to shift the data in the Shifter register.                                                                                                                                                                                                                                                                   |  |

| 20                    | ı           | S/L       | Shift or Load input serves dual functions. It is generated by the 82C432A Sequencer. When low, the display memory data will be loaded into the Shifter. When high, it will shift the data in the Shifter by one bit.                                                                                                                                      |  |

| 25                    | 1           | WE        | Write Enable is an active low input. When it is active, the display memory data is output on the M0D0-D7, M1D1-D7, M2D0-D7 and M3D0-D7 data buses. When WE is high, these data buses are tri-stated.                                                                                                                                                      |  |

| 7                     | 1           | IOW       | I/O Write is an active low input. It is used to load internal registers of the graphics controller by the CPU. The address and data setup and hold times must be met in order to write data into the internal registers.                                                                                                                                  |  |

| 61                    | t           | MRD       | Memory Read is an active low input. It is used by the CPU to read display memory data in conjunction with the high going edge of the CPUL input.                                                                                                                                                                                                          |  |

# 82C431 Pin Description

(Continued)

| Pin No.                 | Pin<br>Type | Symbol                        | Description                                                                                                                                                                                                                                                                                                                |

|-------------------------|-------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-6                     | 1           | A0-A2                         | Address signals A0, A1 and A2 are used by CPU to select the internal registers of the graphic controller.                                                                                                                                                                                                                  |

| 40<br>41<br>24-23       | 0<br>0<br>0 | GRAPHICS<br>CHAIN<br>CDSEL0-1 | Graphics, Chain, CDSEL0 and CDSEL1 are outputs of the Miscellaneous register. They can be tri-stated by setting the Mode register bit 2 to logical 1. Graphics & Chain outputs are used to multiplex the address buses in the 82C434A CRT Controller. CDSEL0 and CDSEL1 outputs control the mapping of the display memory. |

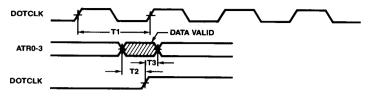

| 39, 37<br>33, 31        | 0           | ATR0-ATR3                     | Attributes 0-3 are used to transfer the output of the Shifter register to the 82C433 Attributes Controller in the graphics mode. In the alphanumeric mode, ATR0-ATR3 transfer the data on the M1D0-M1D3 to the Attributes Controller.                                                                                      |

| 1, 10, 18<br>35, 45, 52 |             | V <sub>SS</sub>               | Ground.                                                                                                                                                                                                                                                                                                                    |

| 68, 17,<br>34, 51       | _           | V <sub>DD</sub>               | 5 Volt Power Supply.                                                                                                                                                                                                                                                                                                       |

# 82C432A Pin Description

| Pin No.               | Pin<br>Type | Symbol                              | Description                                                                                                                                                                                                                                                                           |  |

|-----------------------|-------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2                     | ı           | CLKIN                               | Clock In is the input clock. It is the primary clock source for the chip. The output Dot Clock is of the same frequency as the CLKIN frequency.                                                                                                                                       |  |

| 36                    | 1           | Α0                                  | Address 0 is the address 0 of the CPU address bus. It is used to select between the index register and the control registers on the device. It is also used to write into even/odd memory planes.                                                                                     |  |

| 32-35                 | t           | D0-D3                               | D0-D3 are low order data bus bits. They are used to load the Sequencer registers.                                                                                                                                                                                                     |  |

| 4,3                   | I           | CRA14,15                            | CRA14 and CRA15 are the high order address bits for the CRT display read. These bits are generated by the 82C434A CRT Controller.                                                                                                                                                     |  |

| 6,5                   | ı           | CPA14,15                            | CPA14 and CPA15 are the high order address bits fo the CPU read/write operations. CPA14 is bit 14 of th CPU address bus. CPA15 is the decoded signal from the CPU address bus signals A13-A19. During memory read and write cycles, AAV14 = BAV14 = CPA14, and AAV15 = BAV15 = CPA15. |  |

| 37                    | 1           | CG                                  | CG is the Character Generator bit from the display memory. It is the attribute bit 3. It is used to select between the character maps A and B.                                                                                                                                        |  |

| 39,38                 | ı           | MEMR<br>MEMW                        | Memory Read and Memory Write are active low inputs. These inputs are used by the processor to read from and write into the display memory.                                                                                                                                            |  |

| 15                    | ı           | IOW                                 | I/O Write is the control signal from the system bus. It is used to load the various registers on the Sequence                                                                                                                                                                         |  |

| 31                    | 1           | MEMOPT                              | Memory Option is the control signal used to select 64K or 256K byte memory configurations as follows  MEMOPT  0  256K Bytes  1  64K Bytes                                                                                                                                             |  |

| 17                    | ı           | SYNC                                | Sync is generated by the 82C434A CRT Controller. It is used to disable the AS/L (Address Strobe/Load) signal during non-active display periods.                                                                                                                                       |  |

| 21-24                 | 0           | RAS0-<br>RAS3                       | RAS0-RAS3 are the Row Access Strobe signals for the four memory planes.                                                                                                                                                                                                               |  |

| 7,10                  | 0           | ACAS<br>BCAS                        | ACAS and BCAS are the Column Access Strobe signals for the memory planes.                                                                                                                                                                                                             |  |

| 9,<br>8,<br>12,<br>11 | 0           | AAV14,<br>AAV15,<br>BAV14,<br>BAV15 | AAV14, AAV15, BAV14 and BAV15 are high order active high signals for the two memory maps. During memory read and write cycles, AAV14 = BAV14 = CPA14, and AAV15 = BAV15 = CPA15.                                                                                                      |  |

# 82C432A Pin Description

(Continued)

| Pin No. | Pin<br>Type | Symbol          | Description                                                                                                                                                                                                                                                                                      |  |

|---------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13      | 0           | CRTL            | CRT LATCH is an active low signal. It is used to latch the memory data into the 82C431 Graphics Controller, and the 82C433 Attributes Controller, for CRT display read cycles.                                                                                                                   |  |

| 14      | 0           | CPUL            | CPU LATCH is an active low signal. It is used to load memory data into the Graphics Controller 82C431, for CPU memory read cycles.                                                                                                                                                               |  |

| 16      | 0           | WE              | Write Enable is an active low signal used to enable the CPU to write into the display memory.                                                                                                                                                                                                    |  |

| 18      | 0           | MUX             | MULTIPLEXER output is used to multiplex the RAS and CAS signals.                                                                                                                                                                                                                                 |  |

| 19      | 0           | DOTCLK          | Dot Clock output is used by the 82C431 Graphics Controller and by the 82C433 Attributes Controller.                                                                                                                                                                                              |  |

| 26      | 0           | CCLK            | Character Clock is an active high signal. It is used by the 82C434A CRT Controller.                                                                                                                                                                                                              |  |

| 28      | 0           | S/L             | Shift/Load output is used to load display memory graphics data into the 82C431 Graphics Controller.                                                                                                                                                                                              |  |

| 27      | 0           | AS/L            | Attributes Shift/Load signal is used to load alpha-<br>numeric display memory data into the 82C433<br>Attributes Controller.                                                                                                                                                                     |  |

| 25      | 0           | CRT/CPU         | CRT/CPU control signal is used by the 82C434A CR Controller to enable either the CRT read address or the CPU read/write address.                                                                                                                                                                 |  |

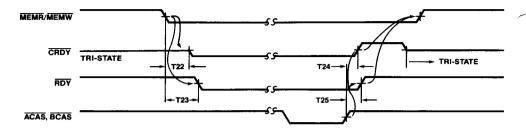

| 30      | 0           | RDY             | Ready is an active low output. It is used by the CPU indicate that a data transfer will be completed. It becomes inactive as soon as the memory read or write operation is completed. RDY acts as an enable input for a tri-state driver which drives the CPU Reainput.                          |  |

| 29      | 0           | CRDY            | CReady is similar to the RDY output. The difference between the two signals is the way they go inactive (high). The RDY when inactive goes high and stays high. The CRDY when inactive goes high for one dot clock period, and then goes tri-state. CRDY can directly drive the CPU Ready input. |  |

| 1,20    | _           | V <sub>SS</sub> | Ground.                                                                                                                                                                                                                                                                                          |  |

| 40      |             | V <sub>DD</sub> | 5 Volt Power Supply.                                                                                                                                                                                                                                                                             |  |

# 82C433 Pin Description

| Pin No. | Pin<br>Type                        | Symbol                           | Description                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-39   | I                                  | CC0-CC7                          | CC0-CC7 are the 8 Condition Code inputs coming directly from the display memory (plane 2). These 8 inputs are loaded into a parallel-to-serial shift register. The output of this shift register enables either ATR0-3 (CC=1), or ATR4-7 (CC=0) to address the color palette.                                                                                                        |

| 11-14   | I                                  | ATR7-ATR4                        | ATR7-ATR4 are the 4 high order attributes bits for alphanumeric data coming directly from the display memory (plane 1). The proper Condition Code bit chooses between ATR7-4 and ATR3-0.                                                                                                                                                                                             |

| 15-18   | I                                  | ATR3-ATR0                        | ATR3-ATR0 are the 4 low order attributes bits. They could either be graphics data, in which case they come from the 82C431 Graphics Controller or alphanumeric data, in which case they come from the display memory multiplexed through the Graphics Controller along with the graphics data. The Graphics Controller decides whether the incoming data is graphic or alphanumeric. |

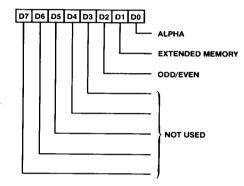

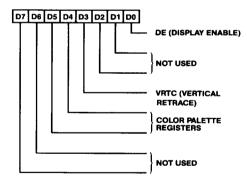

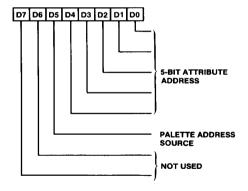

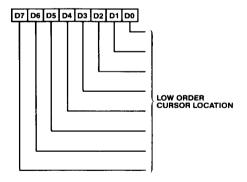

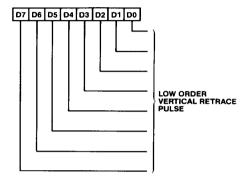

|         |                                    |                                  | D0-D5 are the 6 data bus signals. Four of these D5, D4, D3 and D0 are bidirectional while the other two, D2 and D1 are inputs only. The 4 bidirectional pins when read, output the following 4 status bits:                                                                                                                                                                          |

| 1-6     | 1/O<br>1<br>1<br>1/O<br>1/O<br>1/O | D0<br>D1<br>D2<br>D3<br>D4<br>D5 | D5: Color palette bit 1, D4: Color palette bit 0, D3: VRTC (Vertical retrace), D0: DE (Display Enable).                                                                                                                                                                                                                                                                              |

|         |                                    |                                  | Bits D5 and D4 are controlled by the Color Plane<br>Enable register bits 5, 4. Bits D3 and D0 are generated<br>by the 82C434A CRT Controller.                                                                                                                                                                                                                                        |

| 9       | ı                                  | ĪŌR                              | I/O Read is an active low signal. This signal has the dual purpose of reading the status, as well as clearing the address/data flip-flop.                                                                                                                                                                                                                                            |

| 10      | ı                                  | ĪŌW                              | I/O Write is an active low signal. It loads either the address register, one of the 16 color palette registers, or one of the 4 control registers.                                                                                                                                                                                                                                   |

| 19      | ı                                  | DOTCLK                           | Dot Clock is the active high clock generated by the 82C432A Sequencer.                                                                                                                                                                                                                                                                                                               |

| 7       | I                                  | CRTL                             | CRT Latch is an active low signal. It is used to load display memory data into the 82C433. It is generated by the 82C432A Sequencer.                                                                                                                                                                                                                                                 |

| 8       | ı                                  | S/L                              | $S/\bar{L}$ is the Shift/Load signal to load display memory data into the 82C433. It is generated by the 82C432A Sequencer as AS/ $\bar{L}$ signal.                                                                                                                                                                                                                                  |

# 82C433 Pin Description

(Continued)

| Pin No. | Pin<br>Type | Symbol                       | Description                                                                                                                                                                                                                                                                                                                                    |  |

|---------|-------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

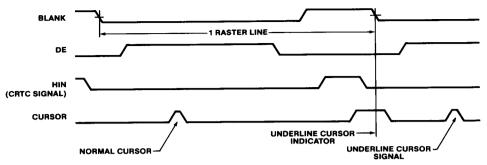

| 27      | I           | BLANK                        | BLANK is the Blank output from the 82C434A CRT Controller. It is low during the time the monitor is displaying data.                                                                                                                                                                                                                           |  |

| 28      | 1           | VRTC                         | VRTC is the Vertical Retrace output from the 82C434A CRT Controller. It is used by an internal 5 bit counter (divide by 32) to generate the blink clock required by blinking displays. The blink clock is ON for 16 VRTC periods and OFF for 16 VRTC periods. It is output on the data bus bit D3 as a status bit.                             |  |

| 29      | I           | DE                           | DE is the active high Display Enable output from the 82C434A CRT Controller. It is used for enabling the display area on the screen. When the DE and Blank signals are inactive at the same time, the border is displayed on the monitor. It is output on data bus bit D0 as a status bit.                                                     |  |

| 30      | 1           | CURSOR                       | CURSOR is an active high signal. It provides two functions:  1. During DE active time it indicates a valid cursor position.  2. If Cursor is active during the high-to-low edge of Blank, it indicates that the contents of the CRT Controller Underline Location register (R14) are equal to the line count (contents of the Raster Counter). |  |

| 31      | I           | LG                           | Line Graphics is an active low input from the CRT Controller. It is a logical NAND of M0D5, M0D6 and M0D7 (bits 5, 6 and 7 of plane 0 in display memory).                                                                                                                                                                                      |  |

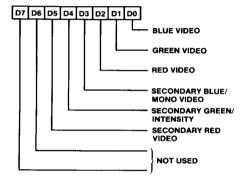

| 21-26   | 0           | R, G, B<br>RS, GS/I,<br>BS/V | R, G, B, RS, GS/I, BS/V are the 6 outputs that drive<br>the monochrome or color monitor. R, G, B are the<br>Red, Green, and Blue signals. The RS, GS/I, and BS/<br>are the Secondary Red, Secondary Green/Intensity,<br>Secondary Blue/Monochrome Video (display) signa                                                                        |  |

| 40      |             | V <sub>DD</sub>              | 5 Volt Power Supply.                                                                                                                                                                                                                                                                                                                           |  |

| 20      | _           | V <sub>SS</sub>              | Ground.                                                                                                                                                                                                                                                                                                                                        |  |

# 82C434A Pin Description

| Pin No. | Pin<br>Type | Symbol          | Description                                                                                                                                                                                 |

|---------|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70      | 1           | A0              |                                                                                                                                                                                             |

| 5       | I           | A1              |                                                                                                                                                                                             |

| 11      | 1           | A2              |                                                                                                                                                                                             |

| 16      | 1           | A3              |                                                                                                                                                                                             |

| 24      | ı           | A4              |                                                                                                                                                                                             |

| 29      | ı           | <b>A</b> 5      |                                                                                                                                                                                             |

| 34      | ı           | A6              |                                                                                                                                                                                             |

| 40      | ļ           | Α7              | CPU Address bits 0-14 and 16. They are used to                                                                                                                                              |

| 35      | !           | A8              | generate addresses for the display memory.                                                                                                                                                  |

| 7       | !           | A9              |                                                                                                                                                                                             |

| 12      |             | A10             |                                                                                                                                                                                             |

| 17      | !           | A11             |                                                                                                                                                                                             |

| 25      | ł           | A12             |                                                                                                                                                                                             |

| 30      | !           | A13             |                                                                                                                                                                                             |

| 74      | Į.          | A14             |                                                                                                                                                                                             |

| 73      | <u> </u>    | A16             |                                                                                                                                                                                             |

| 75-82   | I/O         | D0-D7           | CPU Data Bus bits 0-7. They are used to transfer data to and from the CPU data bus.                                                                                                         |

| 83      | 0           | AA0             |                                                                                                                                                                                             |

| 6       | 0           | AA1             |                                                                                                                                                                                             |

| 10      | 0           | AA2             |                                                                                                                                                                                             |

| 15      | 0           | AA3             | Address bus AAO 7 for moment planes 0 and 1                                                                                                                                                 |

| 23      | О           | AA4             | Address bus AA0-7 for memory planes 0 and 1.                                                                                                                                                |

| 28      | 0           | AA5             |                                                                                                                                                                                             |

| 33      | 0           | AA6             |                                                                                                                                                                                             |

| 39      | 0           | _AA7            |                                                                                                                                                                                             |

| 4       | 0           | BA0             |                                                                                                                                                                                             |

| 8       | 0           | BA1             |                                                                                                                                                                                             |

| 13      | 0           | BA2             |                                                                                                                                                                                             |

| 18      | О           | BA3             | Address Bus BA0-7 for memory planes 2 and 3.                                                                                                                                                |

| 26      | 0           | BA4             | Address bus bao-r for filemory planes 2 and 5.                                                                                                                                              |

| 31      | Ō           | BA5             |                                                                                                                                                                                             |

| 36      | 0           | BA6             |                                                                                                                                                                                             |

| 44      | 0           | BA7             |                                                                                                                                                                                             |

| 2,41    | 1           | AAV14,<br>AAV15 | High address bits 14 and 15 for the A address bus. They are generated by the 82C432A Sequencer.                                                                                             |

| 3,46    | 1           | BAV14,<br>BAV15 | High address bits 14 and 15 for the B address bus.<br>They are generated by the 82C432A Sequencer.                                                                                          |

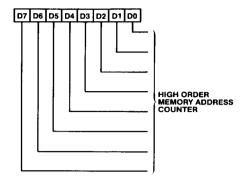

| 48,47   | 0           | MA14,<br>MA15   | Address bits 14, 15 is used by the 82C432A Sequencer to generate the high order address bits AAV14, AAV15, BAV14 and BAV15. These bits can be tri-stated through Mode Control register R17. |

| 20      | 0           | LG              | Line Graphics is an active low output. It is used by the 82C433 Attributes Controller.                                                                                                      |

# 82C434A Pin Description

(Continued)

| Pin No. | Pin<br>Type | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 50      | ı           | CHAIN    | CHAIN is a select input. It is generated by the 82C431 Graphics Controller. It is used with the SAM and MEMOPT inputs to select the LSB of the CPU address.                                                                                                                                                                                                                               |  |

| 49      | 1           | GRAPHICS | GRAPHICS is an active low input. It is generated by the 82C431 Graphics Controller. It is used to change RAM BA addresses from graphics to text mode.                                                                                                                                                                                                                                     |  |

| 51      | ı           | мих      | MULTIPLEXER input is used to multiplex the RAS and CAS address control. MUX is generated by the 82C432A Sequencer.                                                                                                                                                                                                                                                                        |  |

| 52      | ı           | RESET    | RESET initializes the CRT Controller as follows: a. It initializes the horizontal and vertical polarity control to logical 0. b. Mode register bits 4,7 are reset. c. All counters in the CRT Controller are reset. d. Address register bits 3,4 are reset. e. PGSEL is reset to logical 0. All other control registers remain unchanged. RESET must be active for at least 5 dot clocks. |  |

| 54      | I           | CRTL     | CRT Latch is an active low input. It latches M0D0-<br>M0D7 data. It is generated by the 82C432A Sequencer                                                                                                                                                                                                                                                                                 |  |

| 55      | 0           | DE       | Display Enable is an active high output. It enables display areas on the screen. When DE and Blank signals are inactive at the same time, the border is displayed on the monitor.                                                                                                                                                                                                         |  |

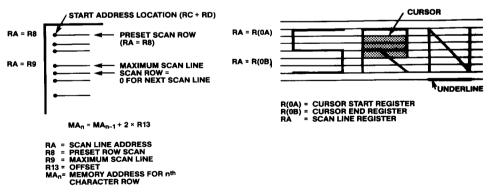

| 56      | 0           | CURSOR   | CURSOR serves dual functions. It indicates a valid cursor position when DE is active. In the other case CURSOR is active during the trailing edge of Blank signal, it signifies that the contents of the Underline Location register R14 are equal to the line count (contents of Raster Count register).                                                                                 |  |

| 57      | 0           | BLANK    | BLANK is an active high output for blanking the screen during retrace periods.                                                                                                                                                                                                                                                                                                            |  |

| 58      | ı           | CRT/CPU  | CRT/CPU is used by the CRT Controller to enable t CRT read address when CRT/CPU = 1. When CRT/CPU = 0, the CPU read or write address is enabled.                                                                                                                                                                                                                                          |  |

| 53      | 0           | HIN      | HIN is horizontal sync output. It is active high if horizontal polarity bit HPOL is low. It is active low if HPOL is high. HPOL is programmed through MODEIOW register. This signal is identical to the HPOI bit of the MISCELLANEOUS output register located in the Graphics Controller.                                                                                                 |  |

# 82C434A Pin Description

(Continued)

| Pin No.                         | Pin<br>Type | Symbol                           | Description                                                                                                                                                                                                                                                                                            |  |

|---------------------------------|-------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 59                              | 0           | VIN                              | VIN is vertical sync output. Like the HIN signal, VIN polarity is also controlled by VPOL. VPOL is programmed through the MODEIOW register. This signal is identical to the VPOL bit of the MISCELLANEOUS output register.                                                                             |  |

| 60                              | 0           | SYNC                             | SYNC is an active high output used by the Sequencer 82C432A to control the AS/ $\overline{L}$ output.                                                                                                                                                                                                  |  |

| 61                              | 0           | VRTC                             | VERTICAL SYNC is active high vertical retrace signal. it is used by the 82C433 Attributes Controller, to generate the blink clock required by the blinking displays.                                                                                                                                   |  |

| 62                              | l           | CLOCK                            | CLOCK is used to synchronize all the functions for the device except the bus interface. The active transition is high to low. It is the CCLK (Character Clock) output from the 82C432A Sequencer.                                                                                                      |  |

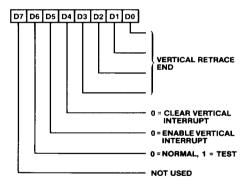

| 65                              | 0           | CRTINT                           | CRT INTERRUPT is an active high output. It is the frame interrupt generated by the 82C434A. It is enabled by bit 5 of the Vertical Retrace End register. It can be cleared by programming bit 4 of Vertical Retrace End register to 0. When not active, the CRTINT output is in a tri-state condition. |  |

| 66                              | 1           | MODEIOW                          | MODEIOW is used to program the MODEIOW registed bits D5 (PGSEL), D6 (HPOL) and D7 (VPOL). The MODEIOW register is cleared by a chip reset.                                                                                                                                                             |  |

| 67                              | I           | iow                              | I/O WRITE is an active low input. It is used to write to the 82C434A registers.                                                                                                                                                                                                                        |  |

| 68                              | ı           | ĪŌR                              | I/O READ is an active low input. It is used to read th 82C434A registers.                                                                                                                                                                                                                              |  |

| 69                              | I           | LPS                              | LIGHT PEN STROBE is used to latch the current refresh address in the light pen register. The address is latched on a low-to-high transition on this input.                                                                                                                                             |  |

| 71                              | ı           | SAM                              | SAM is used with MEMOPT and CHAIN to select LSB of the CPU address.                                                                                                                                                                                                                                    |  |

| 72                              | ı           | МЕМОРТ                           | MEMORY OPTION is used with SAM and CHAIN to select the LSB of CPU address. When MEMOPT is low, there are 256K Bytes of display memory configured. When MEMOPT is high, 64K Bytes of display memory is configured.                                                                                      |  |

| 32,38<br>45,37<br>9,14<br>19,27 | 1           | MD0,1<br>MD2,3<br>MD4,5<br>MD6,7 | Memory Data Bus 0-7 are the character data bits.                                                                                                                                                                                                                                                       |  |

| 1,22,43,64                      | _           | V <sub>SS</sub>                  | Ground.                                                                                                                                                                                                                                                                                                |  |

| 21,42,63,84                     | _           | V <sub>DD</sub>                  | 5 Volt Power Supply.                                                                                                                                                                                                                                                                                   |  |

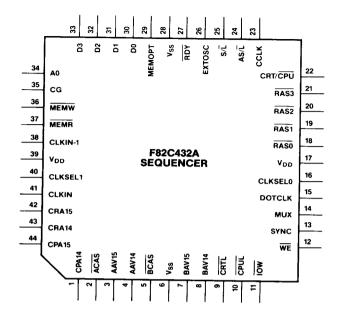

#### Flat Pack Package Options

The 82C432 Sequencer and 82C433 Attributes controller are also available in Plastic Flat-Pack (PFP) packages. The pin diagrams on pages 3-4 describe the pin assignments. Most of the pins on the PFP packages are the same as for 40-pin DIP packages. The differences between the DIP and PFP packages are described here.

#### F82C432A:

The F82C432A features an option to select input clock source from three sources: CLKIN, CLKIN-1 and EXT-OSC. The CLKIN and CLKIN-1 can be clock inputs of 14.318 MHz and 16.257 MHz respectively. Alternatively, a user defined EXT-OSC input clock source can also be selected. CLKSEL0 and CLKSEL1 inputs are used to select the clock input source.

| CLKSEL0 | CLKSEL1 | Clock Source |

|---------|---------|--------------|

| 0       | 0       | CLKIN        |

| 0       | 1       | CLKIN-1      |

| 1       | 0       | EXT-OSC      |

| 1       | 1       | ILLEGAL      |

The CLKSEL0 and CLKSEL1 inputs must be pulled high or low (as desired) for proper operation of the device.

The F82C432A also has only one Ready signal output, RDY. Note that CRDY output is not bonded out on the F82C432A.

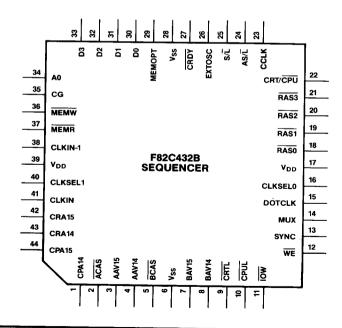

#### F82C432B:

The F82C432B is similar to F82C432A in all respects except for the ready output. In this package,  $\overline{CRDY}$  is bonded out as an output. Note that  $\overline{RDY}$  is not bonded out on this package. The differences between the  $\overline{RDY}$  and  $\overline{CRDY}$  signals are described under pin description for 82C432A. The CLKSEL0, CLKSEL1, CLKIN, CLKIN-1 and EXTOSC inputs operate exactly the same way as for F82C432A.

Note that CLKSEL0, CLKSEL1 and CLKIN-1 and EXTOSC inputs are not available on the 40-pin DIP packages. The inputs on CLKIN, CLKIN-1 and EXTOSC must meet the electrical specifications as described under D.C. and A.C. characteristics for 82C432A.

#### F82C433:

The F82C433 is the Plastic Flat Pack (PFP) package available for the Attributes controller. The input-output signals for the F82C433 are exactly the same as for the 40-pin DIP package. The pin diagram on page 4 describes the pin assignment for this package.

82C431

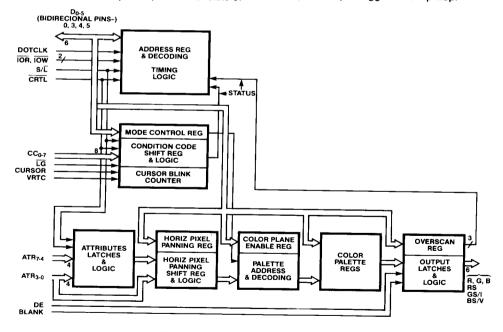

#### 82C431 Functional Description

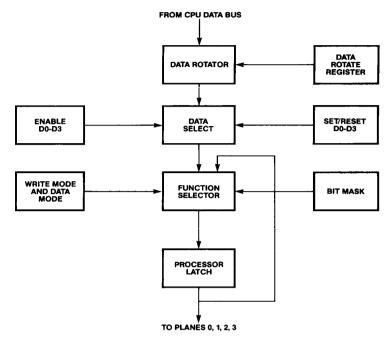

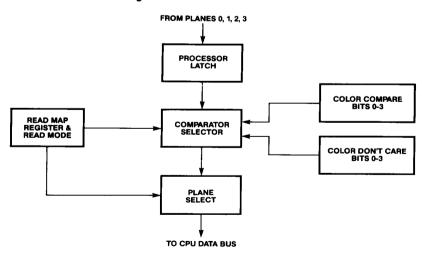

The 82C431 Graphics Controller is responsible for directing data from the display memory to the 82C433 Attributes Controller and the CPU. The 82C431 operates in two basic modes: Alphanumeric and Graphics. In the Alphanumeric Mode, the data is sent in parallel mode through the Graphics Controller directly to the 82C433 Attributes Controller. In the Graphics Mode, memory data is sent in serial mode to the 82C433 Attributes Controller. Figures 2 and 3 illustrate a typical write and read process for Graphics Controller.

The 82C431 formats the data for use in various compatible modes. The controller also provides color comparators which can be used in color painting modes. Data can be written to the display memory planes in 32 bit words to expedite fast color presetting of the display areas on the monitor. Logical functions on the chip allows for manipulation of the data before being written to the display memory.

The Graphics Controller has basically two major sections, Graphics A and Graphics B. The Graphics A writes to the display memory planes 0 and 1, and the Graphics B writes to the memory planes 2 and 3. The following description will refer to these two sections as Graphics A and Graphics B.

#### 82C431 Graphics Controller Register Summary

| Register<br>Number | Register<br>Name    | Pointer<br>Value in Hex |

|--------------------|---------------------|-------------------------|

| _                  | Graphics A Position |                         |

| _                  | Graphics B Position | _                       |

| _                  | Address Register    | _                       |

| R0                 | Set/Reset           | 00                      |

| R1                 | Enable Set/Reset    | 01                      |

| R2                 | Color Compare       | 02                      |

| R3                 | Data Rotate         | 03                      |

| R4                 | Read Map Select     | 04                      |

| R5                 | Mode Register       | 05                      |

| R6                 | Miscellaneous       | 06                      |

| R7                 | Color Don't Care    | 07                      |

| R8                 | Bit Mask            | 08                      |

#### 82C431 Internal Registers

82C431 internal registers are selected through address inputs A0-A2. The following table describes the addressing scheme:

| A2 | <b>A1</b> | A0 | Register selected         |  |

|----|-----------|----|---------------------------|--|

| 1  | 0         | 0  | Graphics A Position       |  |

| 0  | 1         | 0  | Graphics B Position       |  |

| 1  | 1         | 0  | Graphics Address register |  |

| 1  | 1         | 1  | Registers pointed to by   |  |

|    |           |    | Graphics Address register |  |

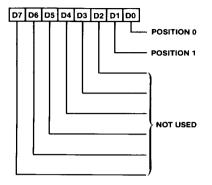

## **Graphics A Position Register:**

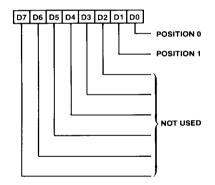

The Graphics A Position register is a write-only register. This register must be programmed to 0 to select Graphics A for the data bus input and output operations. Graphics A operates on the display memory planes 0 and 1, while the Graphics B operates on the display memory planes 2 and 3. CPU data bus signals D0 and D1 should be directed to Graphics A. D2 and D3 should be directed to Graphics B.

#### **Graphics B Position Register:**

The Graphics B Position register is a write-only register. This register must be programmed to 1 to select Graphics B for the data bus input and output operations. Graphics B operates on the display memory planes 2 and 3, while the Graphics A operates on the display memory planes 0 and 1. CPU data bus signals D0 and D1 should be directed to Graphics A. D2 and D3 should be directed to Graphics B.

Figure 2. 82C431 Write Process

Figure 3. 82C431 Read Process

**82C431** 16

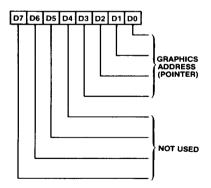

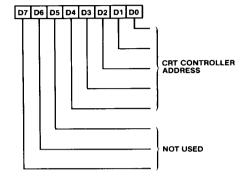

#### **Graphics Address Register:**

The Graphics Address register is used to point to other internal registers of the 82C431. The four least significant bits determine the register which will be pointed to in the next register write operation. In order to write to the registers selected by the pointer in this register, the position registers A and B should be programmed with 0 and 1, respectively. The data bus signals D0-D3 are used to write to the control registers of the 82C431. D0,D1 correspond to the planes 0 and 1, while D2, D3 correspond to the planes 2 and 3 of the display memory.

The following is a description of the registers pointed to by the Address register.

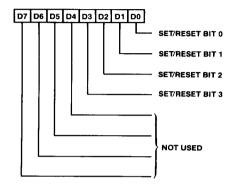

#### Set/Reset Register

The Set/Reset register is a write-only register. The pointer in the Graphics Address register must be 00H before this register can be written into.

When the Mode register (to be described later) selects the 'write' mode 0, and the Set/Reset mode is enabled through the Enable Set/Reset register (to be described later), bits D0-D3 are the value written to the display memory planes 0-3 respectively. The planes can be written to individually by separate writes to the Set/Reset register.

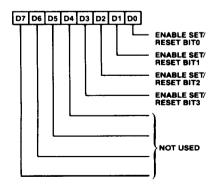

#### **Enable Set/Reset Register**

The Enable Set/Reset register is a write-only register. The register can be written to by setting the pointer in the Graphics Address register to 01H.

This register works in conjunction with the Set/Reset register. If the mode register is programmed to write mode 0, then the contents of the Set/Reset register are written to the respective display memory planes. If the write mode is 0 and Set/Reset is not enabled on a plane, the plane is written with the data from the CPU data bus.

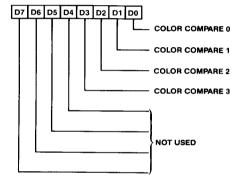

#### **Color Compare Register**

The Color Compare register is a write-only register. It can be written into by setting the pointer in the Graphics Address register to 02H.

If the Mode register has the 'read' mode set, the data read from the display memory planes 0-3, is compared to the bits D0 through D3 programmed in the Color Compare register. A match between the two bit fields will result in a logical 1 being output on the corresponding data bus bit. Following is an example to illustrate the mechanism:

If the contents of the Color Compare register are 0011 (D3-D0), and:

|                | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----------------|----|----|----|----|----|----|----|----|

| Plane 0 data = | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| Plane 1 data = | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| Plane 2 data = | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| Plane 3 data = | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| then data      | 0  | n  | n  | n  | O  | O  | n  | 1  |

| bus result     | Ŭ  | Ū  | Ŭ  | ŭ  | •  | ·  | ·  | •  |

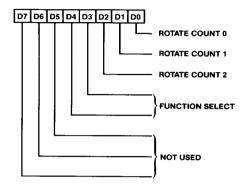

#### **Data Rotate Register**

The Data Rotate register is a write-only register. It is written to by setting the pointer in the Graphics Address register to 03H.

This register is used to perform a rotate function on the data written by the CPU. If the Mode register is programmed for the write mode 0, then the value in the Rotate Count field represents the number of bits the CPU data will be rotated during CPU write cycles.

The Function select bits (D3, D4) allow data in the CPU latches to be logically operated upon by the data written into the memory. The bits operate as follows:

#### D4 D3

- 0 0 No change to the Data

- 0 1 Logical 'AND' between Data and latched data.

- 1 0 Logical 'OR' between Data and latched data.

- 1 Logical 'XOR' between Data and latched data.

'Data' may be any of the various options available with the Write Mode register. Data cannot be the CPU latched data.

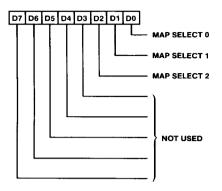

#### Read Map Select Register

Read Map Select register is a write-only register. It is written to by setting the pointer in the Graphics Address register to 04H.

The contents of the register represent the memory plane from which the CPU reads the data. This register does not effect the read operation performed through the Color compare register. The four memory plane or maps are selected as follows:

| D2 | D1 | D0 |       |

|----|----|----|-------|

| 0  | 0  | 0  | Map 0 |

| 0  | 0  | 1  | Map 1 |

| 0  | 1  | 0  | Map 2 |

| 0  | 1  | 1  | Map 3 |

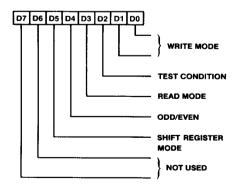

#### Mode Register

This is a write-only register. It can be written to by setting the pointer in the Graphics Address register to 05H.

The functions of the bits are as follows:

Write Mode (D0, D1) D0

- O Mode 0: Each of the four display memory plane is written with the CPU data rotated by the number of counts in the Rotate register. This is always true, except when the Set/ Reset register is enabled for any of the four planes. In this case, the corresponding plane is written with the data stored in the Set/Reset register.

- 0 1 Mode 1: Each of the four display memory planes is written with the data in the CPU latches. These latches are loaded during a previous CPU read operation.

- 0 Mode 2: Memory planes 0-3 is filled up with the value of data bits 0-3, respectively. For example, memory plane 0 is filled up with the value of data bit D0, memory plane 1 is filled up with value of data bus bit D1, and so on.

#### 1 Illegal

The operations specified above will also work in conjunction with the Function Select options available through Data Rotate register.

#### Test Condition (D2)

D2 = 1 will tri-state the Graphics Controller outputs, including the GRAPHICS, CHAIN, CDSEL0 and CDSEL1 outputs. This feature is used for testing the chip. The ATR0-3 outputs are not tri-stated.

## Read Mode (D3) D3

- When D3 = 0, the CPU reads the data 0 from the display memory planes. The plane is selected through the Read Map Select register.

- When D3 = 1, the CPU reads the 1 result of the logical comparison between the four display memory planes data and the contents of the Color Compare register.

#### Odd/Even (D4)

D4 = 1 will put the Graphics Controller in the Odd/Even addressing mode. This option is useful for emulating the IBM Color Graphics Adapter mode. The value of this bit should be the same as the value programmed in D3 of the 82C432 Sequencer Memory Mode register.

#### Shift Register (D5)

The data bits in the memory planes 0-3 are represented as M0D0-M0D7, M1D0-M1D7, M2D0-M2D7, and M3D0-M3D7, respectively. When D5 = 1, the data in the 4 serial shift registers will be formatted as follows:

#### MSB

LSB Output to

M1D0 M1D2 M1D4 M1D6 M0D0 M0D2 M0D4 M0D6 ATR0

M1D1 M1D3 M1D5 M1D7 M0D1 M0D3 M0D5 M0D7 ATR1

M3D0 M3D2 M3D4 M3D6 M2D0 M2D2 M2D4 M2D6 ATR2

M3D1 M3D3 M3D5 M3D7 M2D1 M2D3 M2D5 M2D7 ATR3

The Least Significant Bit (LSB) is shifted out first.

When D5 = 0, then M0D7-M0D0, M1D7-M1D0, M2D7-M2D0 and M3D7-M3D0 are shifted out with the bit D7 going out first in all cases. The output pins being ATR0-ATR3 respectively, for M0-M3 planes.

The first two registers correspond to the Graphics A shift registers, while the following two correspond to the Graphics B shift registers.

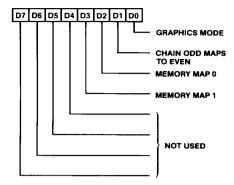

#### Miscellaneous Register

Miscellaneous register is a write-only register. It can be written into by setting the pointer in the Graphics Address register to 06H.

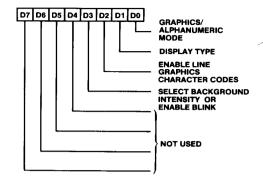

#### **Graphics Mode**

When D0 = 1, the graphics mode is selected. The character generator latches (which are located outside the chip) are disabled. The bit D0 is output on the GRAPHICS pin of the controller.

#### Chain Odd Maps to Even

When D1 = 1, the CPU address bit A0 is replaced by a higher order address bit. (The contents of A0 determine which memory map is to be selected. A '0' will select planes 0 and 2, and a '1' will select planes 1 and 3. This function is also provided outside the chip.) The 82C431 will output the D1 onto the output pin CHAIN of the controller.

#### Memory Maps

These bits control the mapping of the address memory buffers into the CPU address space. The D3 and D2 are output as CDSEL1 and CDSEL0 signals from the Graphics Controller. The mapping function is not performed on the chip.

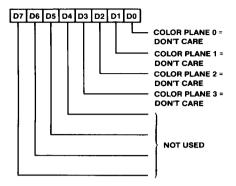

#### Color Don't Care Register

The Color Don't Care register is a write only register. It can be written into by setting the pointer in the Graphics Address register to 07H.

D0 = 0 will mean that color plane 0 is a don't care when the Color Compare register is performed.

D1 = 0 will mean that color plane 1 is a don't care when the Color compare register is performed.

D2 = 0 will mean that color plane 2 is a don't care when the Color compare register is performed.

D3 = 0 will mean that color plane 3 is a don't care when the Color Compare register is performed.

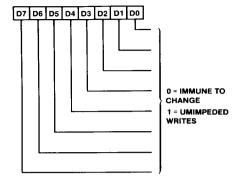

#### Bit Mask Register

Bit Mask Register is a write only register. It can be written into by setting the pointer in the Graphics Address register to 08H.

Any bit programmed to 0 in this register will cause the corresponding bit in each of the four memory planes to be immune to change. The data written into memory in this case will be the data which was read in the previous cycle, and was stored in an internal latch on the chip.

Any bit programmed to 1 will allow unrestricted manipulation of the data in the corresponding bit in each of the four memory planes.

The bit mask is applicable to any data written by the CPU, including rotate, logical functions (AND, OR, XOR), Set/Reset and No Change. The data to be preserved using the bit mask must be latched internally by reading the location. The bit mask applies to all the four planes simultaneously.

# 82C431 Absolute Maximum Ratings

| Parameter             | Symbol           | Min. | Max.                 | Units |

|-----------------------|------------------|------|----------------------|-------|

| Supply Voltage        | $v_{cc}$         | _    | 7.0                  | V     |

| Input Voltage         | V <sub>I</sub>   | -0.5 | V <sub>DD</sub> + .5 | ٧     |

| Output Voltage        | v <sub>o</sub>   | -0.5 | V <sub>DD</sub> + .5 | ٧     |

| Operating Temperature | T <sub>op</sub>  | -25  | 85                   | С     |

| Storage Temperature   | T <sub>stg</sub> | -40  | 125                  | С     |

**NOTE:** Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions described under Operating Conditions.

# **82C431 Operating Conditions**

| Parameter           | Symbol          | Min. | Max. | Units |

|---------------------|-----------------|------|------|-------|

| Supply Voltage      | V <sub>cc</sub> | 4.75 | 5.25 | ٧     |

| Ambient Temperature | T <sub>A</sub>  | 0    | 70   | С     |

# 82C431 DC Characterisitcs

| Parameter                                                          | Symbol           | Min. | Max. | Unita |

|--------------------------------------------------------------------|------------------|------|------|-------|

| Input High Voltage                                                 | V <sub>IL</sub>  |      | 0.8  | ٧     |

| Input High Voltage (Note 1)                                        | V <sub>IH</sub>  | 2.0  |      | V     |

| Output Low Voltage<br>I <sub>OL</sub> = 4mA (Note 2)               | V <sub>OL</sub>  |      | 0.45 | ٧     |

| Output High Voltage<br>I <sub>OH</sub> = -4mA (Note 2)             | V <sub>OH</sub>  | 2.4  |      | V     |

| Input Low Current<br>0 < V <sub>IN</sub> < V <sub>CC</sub>         | I <sub>IL</sub>  |      | ±10  | μΑ    |

| Output Short Circuit Current<br>V <sub>O</sub> =0V                 | Ios              | _    | 20   | mA    |

| Power Supply Current @ 20 MHz Clock                                | I <sub>CC</sub>  |      | 20   | mA    |

| Output HI-Z Leak Current 0.45 < V <sub>OUT</sub> < V <sub>CC</sub> | I <sub>OZ1</sub> |      | ±10  | μΑ    |

#### NOTES:

- Following inputs require VIH = 3.0V (min.): DOTCLK, CPUL, CRTL, S/L, WE. All other inputs require VIH = 2.0V (min.)

- 2. All outputs and bidirectional pins.

**82C431** 22

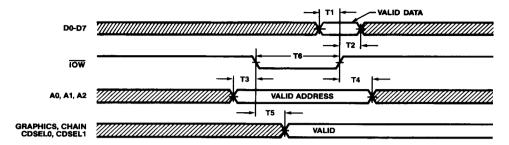

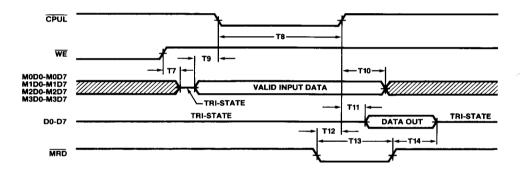

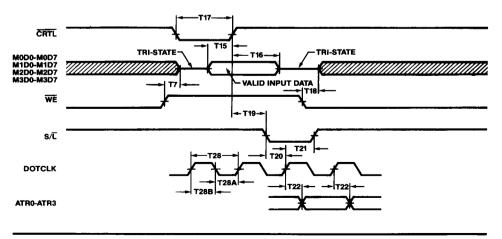

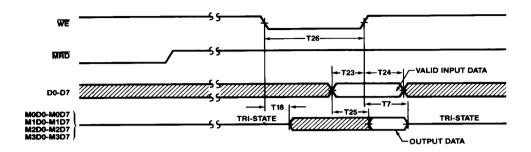

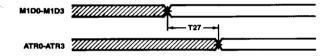

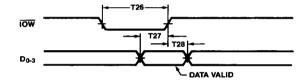

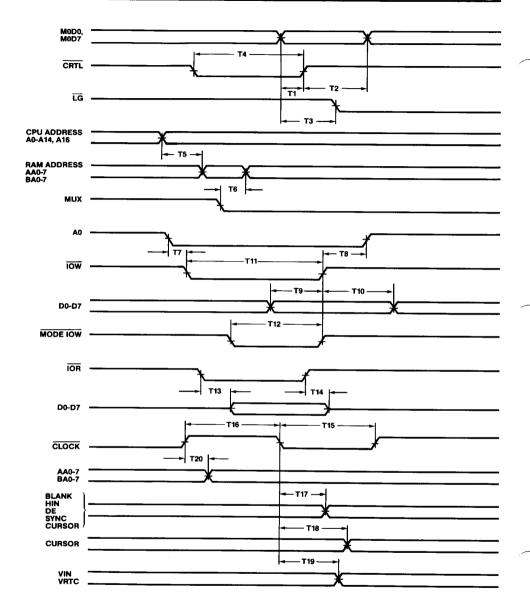

# **82C431 AC Characteristics**

(T<sub>A</sub> = 0°C to 70°C,  $V_{CC}$  = 5V  $\pm$  5%)

| Sym  | Description                                      | Min. | Max.  | Units | Notes                 |

|------|--------------------------------------------------|------|-------|-------|-----------------------|

| t1   | Data set-up time to IOW                          | 55   |       | ns    |                       |

| t2   | Data hold time from IOW                          | 16   |       | ns    |                       |

| t3   | Address set-up time to IOW                       | 10   | • • • | ns    |                       |

| t4   | Address hold time from IOW                       | 8    |       | ns    |                       |

| t5   | Miscellaneous register output delay              | 21   | 83    | ns    | See Note              |

| t6   | IOW pulse width                                  | 45   |       | ns    |                       |

| t7   | WE inactive to memory data bus float delay       | 9    | 35    | ns    |                       |

| t8   | CPUL pulse width                                 | 40   |       | ns    |                       |

| t9   | Input data set-up time to CPUL                   | 0    |       | ns    |                       |

| t10  | Input data hold time from CPUL                   | 14   |       | ns    |                       |

| t11  | Output data delay time                           | 16   | 56    | ns    |                       |

| t12  | MRD set-up time to CPUL                          | 10   |       | ns    |                       |

| t13  | MRD pulse width                                  | 66   |       | ns    |                       |

| t14  | MRD inactive to D0-D7 float delay                | 11   | 42    | ns    |                       |

| t15  | Display memory data M0-M3 bus set-up time        | 5    |       | ns    |                       |

| t16  | Display memory data M0-M3 bus hold time          | 13   |       | ns    |                       |

| t17  | CRTL pulse width                                 | 40   |       | ns    |                       |

| t18  | WE active to display memory data outputs enabled | 11   | 45    | ns    |                       |

| t19  | S/L to CRTL delay                                | 10   |       | ns    |                       |

| t20  | S/L to DOTCLK set-up time                        | 25   |       | ns    |                       |

| t21  | S/L to DOTCLK hold time                          | 8    |       | ns    |                       |

| t22  | Attributes output data delay from DOTCLK         | 9    | 37    | ns    | C <sub>L</sub> = 35pF |

| t23  | Data bus D0-D7 hold time from WE                 | 85   |       | ns    |                       |

| t24  | Data bus D0-D7 hold time from WE                 | 0    |       | ns    |                       |

| t25  | D0-D7 in to display memory data delay            | 26   | 103   | ns    |                       |

| t26  | WE pulse width                                   | 90   |       |       |                       |

| t27  | M1D0, M1D1, M1D2, M1D3 to ATTR0-3 delay          | 8    | 31    | ns    | C <sub>L</sub> = 30pF |

| t28  | Dot Clock period                                 | 42   |       | ns    |                       |

| t28A | Dot Clock low time                               | 19   | _     | ns    |                       |

| t28B | Dot Clock high time                              | 19   | _     | ns    |                       |

**NOTE:** A.C. TEST CONDITIONS: All A.C. timings are measured with a load capacitance of  $C_L$  = 85pF, except where noted otherwise.

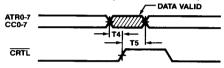

#### REGISTER WRITE TIMING

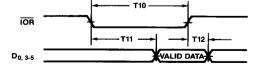

#### **CPU READ TIMING**

#### **CRT READ TIMING**

82C431

# CPU WRITE TIMING (MEMORY WRITE)

# M1D0-M1D3 TO ATR0-ATR3 DELAY (ALPHA MODE)

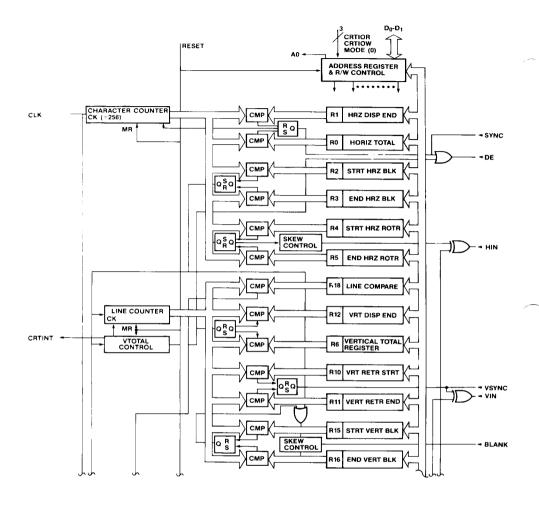

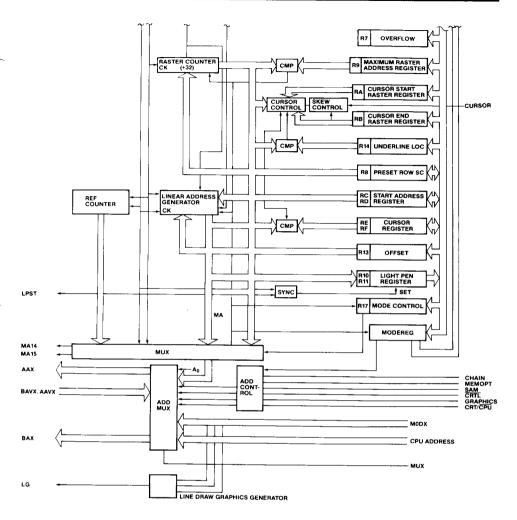

# 82C432A Functional Description

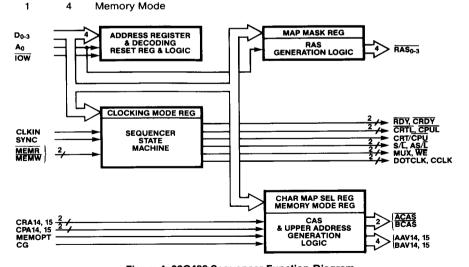

The 82C432A Sequencer generates memory timings for the display RAMs and the character clock for controlling the regenerative memory fetches. Figure 4 shows a functional diagram of the Sequencer. As shown in the figure, the Sequencer also provides control signals for other components in the Enhanced Graphics CHIPSet. The 82C432A allows the CPU to access memory during active display intervals by inserting dedicated CPU memory cycles. Figures 5-8 illustrate various memory cycles for different configurations. As is shown in the figures, the memory cycle selection allows different screen resolutions. The 82C432A also protects the entire memory from being altered, by selectively masking out planes through the configurable Mask register.

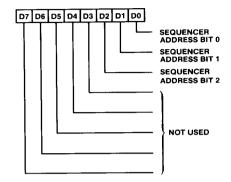

82C432A internal registers are selected through address input A0. The following table describes the addressing scheme:

# A0 POINTER REGISTER SELECTED

| U | _ | Address               |

|---|---|-----------------------|

| 1 | 0 | Reset                 |

| 1 | 1 | Clocking Mode         |

| 1 | 2 | Plane Mask (Map Mask) |

| 1 | 3 | Character Map Select  |

|   |   |                       |

#### **Address Register**

The Address Register is a 3-bit write-only pointer register. When loaded with a binary value (pointer) it points to the data register where data is to be written.

#### Reset Register

The Reset Register is a write-only register pointed to when the contents of the Address Register are 00H.

Figure 4: 82C432 Sequencer Function Diagram

#### NOTE

#### CONDITIONS:

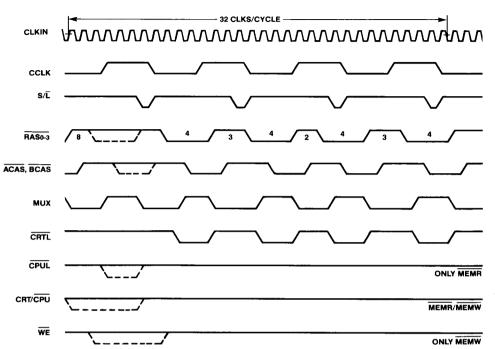

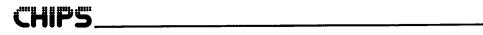

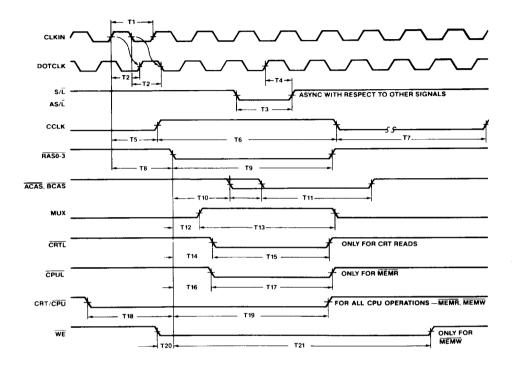

Mode Reg = 01H CRT read 4 out of 5 memory cycles 8 Dots/Char, load every char clock, normal DOTCLK

Figure 5. A Typical 640 × 350 Mode Operation

<sup>1. &</sup>lt;u>Dotted waveforms indicate CPU MEMR/MEMW</u>

RAS/CAS occur for both CPU MEMR/MEMW

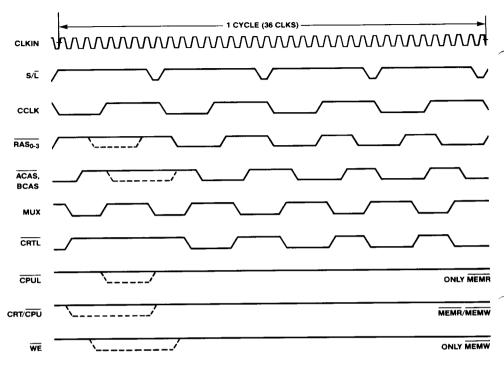

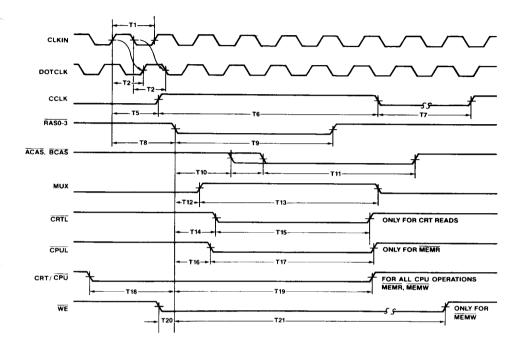

# **CONDITIONS:**

Mode Reg = 03H CRT reads 2 out of 5 memory cycles 8 Dots/Char, load every char clock, normal DOTCLK

Figure 6. A Typical 320 × 200 Mode of Operation

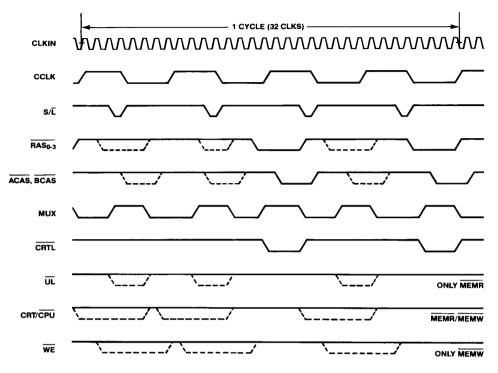

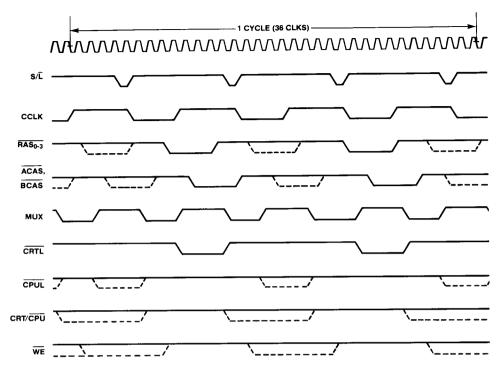

#### **CONDITIONS:**

Mode Reg = 00H CRT reads 4 out of 5 memory cycles 9 Dots/Char, load every char clock, normal DOTCLK

Figure 7. A Typical 720 × 350 Monochrome Operation

#### CONDITIONS:

Mode Reg = 02H CRT reads 2 out of 5 memory cycles

9 Dots/Char, load every char clock, normal DOTCLK

Figure 8. A Typical 9 Dots/Character with 2 out of 5 Memory Cycle Operation

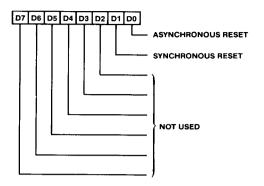

#### Asynchronous Reset

D0=0 causes the Sequencer to clear asynchronously and halt. It also places all the outputs in a high impedance state.

D0=1 causes the Sequencer to run unless D1=0 (Synchronous Reset).

Asynchronous Reset can cause data loss in the dynamic display RAMs.

#### Synchronous Reset

D1=0 causes the Sequencer to clear synchronously and halt. D1=1 causes the Sequencer to run unless D0 (Asynchronous Reset) is cleared to zero. Before changing the Clocking Mode Register, the Sequencer should be reset with this bit. This will preserve the memory contents. Both the Reset Register bits must be a logical 1 to allow the Sequencer to operate.

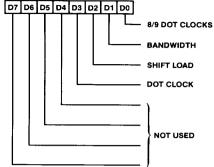

#### **Clocking Mode Register**

This register is a 4-bit write-only register pointed to when the contents of the Address Register are 01H.

### 8/9 Dot Clocks (D0)

D0=0 causes the Sequencer to generate character clocks which are 9 dots wide. D0=1 causes the Sequencer to generate character clocks which are 8 dots wide.

The only IBM mode that uses 9 dots wide character clocks is the monochrome alphanumeric mode. The resolution for this mode is 720 x 350. All other modes use 8 dots wide character clocks.

#### Bandwidth (D1)

D1=0 makes CRT memory cycles occur on 4 out of 5 available display memory cycles.

D1=1 makes CRT memory cycles occur on 2 out of 5 available display memory cycles. Medium resolution modes (horizontal resolution of 320 pixels) require less data to be fetched from the display memory driving the horizontal scan time. This allows the CPU greater access time to the display memory. All high resolution modes (horizontal resolution of 640 or 720 pixels) must provide the CRT Controller with 4 out of 5 available display memory cycles in order to refresh the display image.

#### Shift Load (D2)

D2=0 causes the display serializers in the Graphics Controller to be reloaded every character clock.

D2=1 causes the display serializers to be reloaded every other character clock. This mode is useful when 16 bits are fetched every memory cycle and chained together in the shift registers.

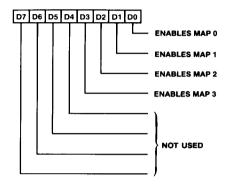

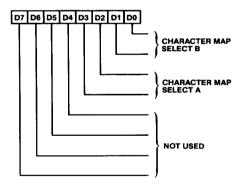

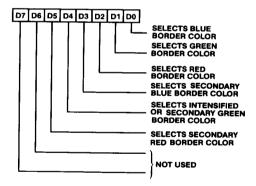

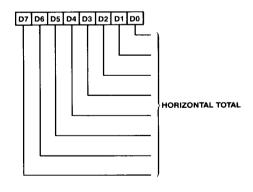

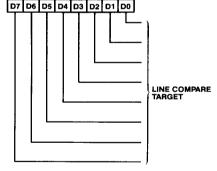

This bit is only set for APA (all-points-addressable) graphics modes.