# Mobile Intel® 915GM/PM/GME/GMS and 910GML/GMLE Express Chipset

**Specification Update**

**April 2007**

Document Number: 307167-012

NFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting <a href="Intel's Web Site">Intel's Web Site</a>.

This document contains information on products in the design phase of development.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

Code Names are only for use by Intel to identify products, platforms, programs, services, etc. ("products") in development by Intel that have not been made commercially available to the public, i.e., announced, launched or shipped. They are never to be used as "commercial" names for products. Also, they are not intended to function as trademarks.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel VPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2005–2007, Intel Corporation. All rights reserved.

This device is protected by U.S. patent numbers 5,315,448 and 6,516,132, and other intellectual property rights. The use of Macrovision's copy protection technology in the device must be authorized by Macrovision and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision. Devices incorporating Macrovision's copy protection technology can only be sold or distributed to companies appearing on Macrovision's list of "Authorized Buyers" at: www.macrovision.com. Reverse engineering or disassembly is prohibited.

#### Revision History

## **Contents**

| Revision History             | 4  |

|------------------------------|----|

| Preface                      | 5  |

| Summary Tables of Changes    | 6  |

| Identification Information   | 13 |

| Errata                       | 16 |

| Specification Changes        | 27 |

| Specification Clarifications | 30 |

| Documentation Changes        | 31 |

# **Revision History**

| Revision | Description                                                                              | Date           |

|----------|------------------------------------------------------------------------------------------|----------------|

| -001     | Initial public release                                                                   | March 2005     |

| -002     | Added Errata 25 – 27                                                                     | May 2005       |

|          | Added Specification Changes 2 – 5                                                        |                |

|          | Added Specification Clarification 1                                                      |                |

|          | Added Documentation Change 5                                                             |                |

| -003     | Added Erratum 28                                                                         | June 2005      |

|          | Added Erratum and Component Marking Information for C1 Stepping                          |                |

| -004     | Added Erratum 29                                                                         | July 2005      |

| -005     | Added Erratum 30                                                                         | August 2005    |

|          | Updated Erratum 7 & 25                                                                   |                |

|          | Updated Specification Clarification 1                                                    |                |

| -006     | Spec Clarification: DVMT 3.0 support configurations                                      | September 2005 |

|          | Doc Change : LBKLT_CRTL signal description update                                        |                |

| -007     | Corrected S-Spec numbers for 915GMS & 910GML PB-free parts (S-Spec numbers were swapped) | September 2005 |

| -008     | Added Erratum 31                                                                         | October 2005   |

| -009     | Updated Erratum 29 status                                                                | November 2005  |

|          | Added C-2 stepping information                                                           |                |

| -010     | Added Erratum 32                                                                         | January 2006   |

|          | Doc Change : register bit definition changed for CODRCO                                  |                |

|          | Doc Change : register bit definition changed for C0DRC1                                  |                |

| -011     | Added Erratum 33                                                                         | October 2006   |

| -012     | Added 915GME SKU to most references of 915GM                                             | April 2007     |

|          | Added 910GMLE SKU to most references of 910GML                                           |                |

§

## Preface

This document is an update to the specifications contained in the documents listed in the following Affected Documents table. It is a compilation of device and document errata and specification clarifications and changes, and is intended for hardware system manufacturers and for software developers of applications, operating system, and tools.

Information types defined in the Nomenclature section of this document are consolidated into this update document and are no longer published in other documents. This document may also contain information that has not been previously published.

#### **Affected Documents**

| Document Title                                                            | Document Location/Number |

|---------------------------------------------------------------------------|--------------------------|

| Mobile Intel® 915 and 910 Express Chipset Family of Products<br>Datasheet | <u>305264</u>            |

#### **Nomenclature**

**Errata** are design defects or errors. Errata may cause the behavior of the Intel® 915GM/PM/GMS/GME and 910GML/GMLE Express Chipset GMCH to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in the next release of the specifications.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specifications.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.

**Note:** Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

§

## Summary Tables of Changes

The following table indicates the Errata, Specification Changes, Specification Clarifications or Documentation Changes which apply to the listed Intel 915GM/PM/GMS/GME and 910GML/GMLE Express Chipset GMCH steppings. Intel intends to fix some of the errata in a future stepping of the component and to account for the other outstanding issues through documentation or Specification Changes as noted.

**Note:** B1 and C1 stepping parts will not be produced for the 915GME and the 910GMLE products.

This table uses the following notations:

## **Codes Used in Summary Table**

## **Stepping**

X: Erratum, Specification Change or Clarification that applies

to this stepping.

(No mark) or (Blank Box): This erratum is fixed in listed stepping or specification

change does not apply to listed stepping.

#### **Status**

Doc: Document change or update that will be implemented.

Plan Fix: This erratum may be fixed in a future stepping of the

product.

Fixed: This erratum has been previously fixed.

No Fix: There are no plans to fix this erratum.

#### Row

Shaded: This item is either new or modified from the previous version of the document.

|    | Steppings |       |    |     |      |     |    |      |    |      |          |    |        |                                                                                                                                                 |

|----|-----------|-------|----|-----|------|-----|----|------|----|------|----------|----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| No |           | 915PN | 1  | 915 | GM/G | SME | 9  | 15GM | S  | 9100 | GML/GMLE |    | Plans  | ERRATA                                                                                                                                          |

|    | СО        | C1    | C2 | В1  | C1   | C2  | СО | C1   | C2 | B1   | C1       | C2 |        |                                                                                                                                                 |

| 1  | Х         | Х     | Х  | Х   | Х    | Х   |    |      |    |      |          |    | No Fix | Reported LOs Exit<br>Latency Is Not<br>Updated When PCI<br>Express* Is Not<br>Operating in<br>Common Clock Mode                                 |

| 2  | Х         | Х     | Х  | Х   | Х    | Х   |    |      |    |      |          |    | No Fix | GMCH Will Not<br>Identify Back to Back<br>Malformed Packets                                                                                     |

| 3  | X         | Х     | Х  | X   | Х    | Х   |    |      |    |      |          |    | No Fix | The GMCH Is Limited to Reporting Poisoned TLPs through Standard PCI Error Status Reporting Structures                                           |

| 4  | X         | X     | X  | Х   | X    | X   |    |      |    |      |          |    | No Fix | Incorrect PCI Express Lane Transition after Receiving Several TS1 Packets                                                                       |

| 5  | Х         | Х     | Х  | X   | Х    | Х   | Х  | Х    | Х  | Х    | Х        |    | No Fix | DMI Link Egress Port<br>Address Is Not<br>Programmable                                                                                          |

| 6  | Х         | Х     | Х  | Х   | Х    | Х   | Х  | Х    | Х  | Х    | Х        |    | No Fix | DDR2 OCD<br>Nonfunctional                                                                                                                       |

| 7  | X         | X     | X  | X   | X    | X   |    |      |    |      |          |    | No Fix | PCI Express Graphics<br>Initiated Snooped<br>Reads to Memory<br>That Are Fast<br>Dispatched Could<br>Result in Incorrect<br>Data Being Returned |

| 8  | Х         | Х     | Х  | Х   | Х    | Х   |    |      |    |      |          |    | No Fix | PCI Express<br>Common Mode<br>Voltage Noise<br>Immediately<br>Following Receiver<br>Detect sequence                                             |

| 9  | Х         | Х     | X  | X   | X    | X   |    |      |    |      |          |    | No Fix | GMCH Does Not<br>Ignore a PCI Express<br>Null Packet                                                                                            |

#### Summary Tables of Changes

|    | Steppings |       |    |     |      |       |    |      |    |      |       |     |        |                                                                                                                                                                 |

|----|-----------|-------|----|-----|------|-------|----|------|----|------|-------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No | (         | 915PN | 1  | 915 | GM/G | SME . | 9  | 15GM | S  | 9100 | GML/G | MLE | Plans  | ERRATA                                                                                                                                                          |

|    | СО        | C1    | C2 | B1  | C1   | C2    | СО | C1   | C2 | B1   | C1    | C2  |        |                                                                                                                                                                 |

| 10 | Х         | Х     | X  | Х   | X    | Х     |    |      |    |      |       |     | No Fix | Data Payload Byte Count Supplied during an unsupported Upstream Configuration Read Is Not 4 Bytes                                                               |

| 11 | Х         | X     | X  | X   | Х    | Х     |    |      |    |      |       |     | No Fix | PCI Express Replay<br>Timer Register<br>Default Setting Is<br>Incorrect                                                                                         |

| 12 | Х         | X     | X  | X   | Х    | Х     | Х  | Х    | Х  | Х    | Х     | Х   | No Fix | E_SMERR Bit Set<br>Incorrectly                                                                                                                                  |

| 13 |           |       |    | X   |      |       |    |      |    |      |       |     | Fixed  | PCI Express Lane 3 Bit Errors Occur on a Small Percentage of GMCH B-1 Units on certain Boards. PCI Express x16 Interface Only Supported on C0 or Later Stepping |

| 14 |           |       |    | Х   | X    | X     | Х  | X    | X  | X    | Х     | X   | No Fix | Pixel Discoloration<br>Seen When Intel®<br>Dual Frequency<br>Graphics Technology<br>(Intel® DFGT) Is<br>Enabled                                                 |

| 15 | Х         |       |    | Х   |      |       | Х  |      |    | Х    |       |     | Fixed  | System Hang with<br>DDR-333 Memory<br>When Intel® Rapid<br>Memory Power<br>Management Is<br>Enabled during<br>C2/C3/C4                                          |

| 16 |           |       |    | X   |      |       | Х  |      |    |      |       |     | Fixed  | Display becomes a<br>solid Color with<br>Intel® S2DDT<br>Enabled (Only<br>supported on<br>915GM, 915GMS &<br>915GME)                                            |

| 17 | Х         | Х     | Х  | Х   | Х    | Х     |    |      |    |      |       |     | No Fix | PCI Express<br>Scrambling                                                                                                                                       |

|    | Steppings |       |    |     |      |     |    |      |    |      |       |     |        |                                                                                                        |

|----|-----------|-------|----|-----|------|-----|----|------|----|------|-------|-----|--------|--------------------------------------------------------------------------------------------------------|

| No |           | 915PN | 1  | 915 | GM/G | SME | 9  | 15GM | S  | 9100 | SML/G | MLE | Plans  | ERRATA                                                                                                 |

|    | СО        | C1    | C2 | B1  | C1   | C2  | СО | C1   | C2 | B1   | C1    | C2  |        |                                                                                                        |

| 18 |           |       |    | X   |      |     | X  |      |    | X    |       |     | Fixed  | Macrovision Failure<br>for 480p / 576p<br>Modes                                                        |

| 19 | X         | X     | X  | X   | X    | Х   | X  | X    | X  | X    | X     | X   | No Fix | Thermometer Read<br>Register is Non-<br>Functional with<br>Negative Calibration<br>Offset              |

| 20 | X         | X     | X  | X   | X    | X   | X  | X    | X  | X    | X     | X   | No Fix | Potential Electrical<br>Spec Violation If a<br>SO-DIMM Is Only<br>Populated in Channel<br>B            |

| 21 |           |       |    | Х   | Х    | Х   | Х  | Х    | Х  | Х    | Х     | Х   | No Fix | LVDS Panel Power<br>Down Timing<br>Violation during<br>System Reset                                    |

| 22 | Х         | Х     | Х  | Х   | Х    | Х   |    |      |    |      |       |     | No Fix | PCI Express<br>SKP/InitFCx<br>Contention                                                               |

| 23 | Х         |       |    | Х   |      |     | Х  |      |    | Х    |       |     | Fixed  | SMVREF High<br>Current Draw                                                                            |

| 24 |           |       |    | Х   | Х    | Х   | Х  | Х    | Х  | Х    | Х     | Х   | No Fix | Mobile Intel 915GM/GMS/GME and 910GML/GMLE Express Chipset Graphics Clock Crossing Issue               |

| 25 | Х         | Х     | X  | X   | X    | Х   | Х  | X    | X  | X    | X     | X   | NoFix  | Mobile Intel<br>915GM/PM/GMS/GM<br>E and 910GML/GMLE<br>Express Chipset<br>Memory Refresh<br>Queue     |

| 26 | Х         | Х     | Х  | Х   | Х    | Х   |    |      |    |      |       |     | NoFix  | Packet Dropped<br>When Replay Timer<br>Expires and Replay<br>Is in Progress                            |

| 27 | Х         | Х     | X  | Х   | X    | Х   | Х  | X    | X  | X    | Х     | X   | NoFix  | LOCK to non-DRAM<br>Memory Flag<br>(Register Dev 0, Fun<br>0, Offset C8, Bit 9)<br>Is Getting Asserted |

|    |    | Steppings |    |     |      |    |    |      |    |      |       |     |        |                                                                                                  |

|----|----|-----------|----|-----|------|----|----|------|----|------|-------|-----|--------|--------------------------------------------------------------------------------------------------|

| No |    | 915PN     | 1  | 915 | GM/G | ME | 9  | 15GM | s  | 9100 | SML/G | MLE | Plans  | ERRATA                                                                                           |

|    | СО | C1        | C2 | B1  | C1   | C2 | СО | C1   | C2 | B1   | C1    | C2  |        |                                                                                                  |

| 28 |    |           |    | Х   | Х    | Х  | Х  | Х    | X  | X    | Х     | X   | NoFix  | Mobile Intel 915GM/GMS/GME and 910GML/GMLE Express Chipset LVDS — CRT Switching                  |

| 29 |    |           |    | ×   | X*   |    | X  | X*   |    | ×    | X*    |     | Fixed  | Mobile Intel<br>915GM/GMS/GME<br>and 910GML/GMLE<br>Express Chipset<br>LVDS Vos                  |

|    |    |           |    |     |      |    |    |      |    |      |       |     |        | *C1 units with FPO date code of WW49 or later are not affected by the erratum.                   |

| 30 | Х  | X         | Х  | Х   | Х    | Х  |    |      |    |      |       |     | NoFix  | Mobile Intel<br>915PM/GM/GME<br>Express Chipset x1<br>False Detect                               |

| 31 | X  | X         | X  | X   | X    | X  |    |      |    |      |       |     | NoFix  | Mobile Intel 915PM/GM/GME Express Chipset PCI Express Ztx_diff_dc Impedance Violation            |

| 32 | Х  | Х         | Х  | Х   | Х    | Х  | Х  | Х    | Х  | Х    | Х     | X   | No Fix | Mobile Intel 915PM/GM/GMS/GM E and 910GML/GMLE Express Chipset DRAM Clock to CKE Power-up Timing |

| 33 | Х  | X         | Х  | Х   | Х    | Х  | Х  | Х    | Х  | X    | X     | Х   | No Fix | Mobile Intel<br>915PM/GM/GMS/GM<br>E and 910GML/GMLE<br>Express Chipset<br>SMRAM D_CLS Bit       |

**NOTE:** B1 and C1 stepping parts will not be produced for the 915GME and the 910GMLE products.

| Number | SPECIFICATION CHANGES                                                            |

|--------|----------------------------------------------------------------------------------|

| 1      | Graphics Render and Display Clock Frequency Combination Support                  |

| 2      | Intel 915GM Express Chipset Host/Memory/Graphics Clock Support Update            |

| 3      | Intel 915GM Express Chipset Host/Memory/Graphics Clock Support Table 11-1 Update |

#### Summary Tables of Changes

| Number | SPECIFICATION CHANGES                                                                               |

|--------|-----------------------------------------------------------------------------------------------------|

| 4      | Mobile Intel 915GM/GMS/GME and 910GML/GMLE Express Chipset Display and Render Clock Support Updates |

| 5      | Mobile Intel 910GML/GMLE Express Chipset Memory Channel Organization Support Update                 |

| Number | SPECIFICATION CLARIFICATIONS    |  |  |  |  |  |

|--------|---------------------------------|--|--|--|--|--|

| 1      | Slow Transfers for LPC Devices  |  |  |  |  |  |

| 2      | DVMT 3.0 Support Configurations |  |  |  |  |  |

| 1                                 |                                                                    |  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------|--|--|--|--|--|

| Number                            | DOCUMENTATION CHANGES                                              |  |  |  |  |  |

| 1 DRAM Enhanced Addressing Update |                                                                    |  |  |  |  |  |

| 2                                 | Section 5.2.15 C0DRC1 – Channel 0 DRAM Controller Mode 1           |  |  |  |  |  |

| 3                                 | Section 5.2.31 DCC – DRAM Channel Control                          |  |  |  |  |  |

| 4                                 | Section 2.2.33 GCFGC – Graphics Clock Frequency and Gating Control |  |  |  |  |  |

| 5                                 | Section 5.2.12 C0DRT1 – Channel 0 DRAM Timing Register 1           |  |  |  |  |  |

| 6                                 | Section 2.5.3 – LBKLT_CRTL Signal Description Update               |  |  |  |  |  |

| 7                                 | Section 17.2.14 CODRCO – Channel 0 DRAM Controller Mode 0          |  |  |  |  |  |

| 8                                 | Section 17.2.15 CODRC1 – Channel 0 DRAM Controller Mode 1          |  |  |  |  |  |

§

## Identification Information

## **Component Identification via Programming Interface**

The Intel 915PM/GM/GMS/GME and 910GML/GMLE Express Chipset family may be identified by the following register contents:

| Stepping  | Vendor ID <sup>1</sup> | Device ID <sup>2</sup> | Revision<br>Number <sup>3</sup> |

|-----------|------------------------|------------------------|---------------------------------|

| B1        | 8086h                  | 2590h                  | 03                              |

| CO        | 8086h                  | 2590h                  | 03                              |

| C1 and C2 | 8086h                  | 2590h                  | 04                              |

#### NOTES:

- The Vendor ID corresponds to bits 15:0 of the Vendor ID Register located at offset 00– 01h in the PCI function 0 configuration spaces.

- 2. The Device ID corresponds to bits 15:0 of the Device ID Register located at offset 02–03h in the PCI function 0 configuration spaces.

- 3. The Revision Number corresponds to bits 7:0 of the Revision ID Register located at offset 08h in the PCI function 0 configuration spaces.

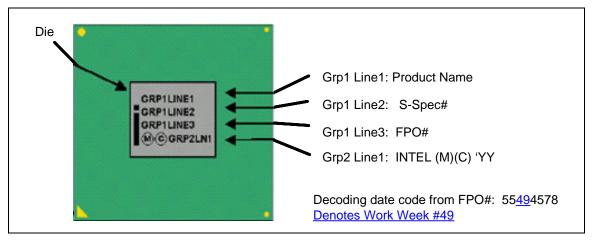

## **Component Marking Information**

The Intel 915PM/GM/GMS/GME and 910GML/GMLE Express Chipset family may be identified by the following component markings:

| Product                              | MM# or<br>S-Spec# | Stepping  | Notes   |

|--------------------------------------|-------------------|-----------|---------|

| Mobile Intel 915GM Express Chipset   | 865926            | B1        |         |

| Mobile Intel 915GM Express Chipset   | 865971            | B1        | Pb-free |

| Mobile Intel 910GML Express Chipset  | 865930            | B1        |         |

| Mobile Intel 910GML Express Chipset  | 865923            | B1        | Pb-free |

| Mobile Intel 915PM Express Chipset   | 867706            | C0        |         |

| Mobile Intel 915PM Express Chipset   | 867713            | C0        | Pb-free |

| Mobile Intel 915GMS Express Chipset  | 867708            | C0        |         |

| Mobile Intel 915GMS Express Chipset  | 867712            | C0        | Pb-free |

| Mobile Intel 915GM Express Chipset   | SL8G2             | C1 and C2 |         |

| Mobile Intel 915GM Express Chipset   | SL8G6             | C1 and C2 | Pb-free |

| Mobile Intel 915GME Express Chipset  | SLA9K             | C1 and C2 | Pb-free |

| Mobile Intel 915PM Express Chipset   | SL8G3             | C1 and C2 |         |

| Mobile Intel 915PM Express Chipset   | SL8G7             | C1 and C2 | Pb-free |

| Mobile Intel 915GMS Express Chipset  | SL8G4             | C1 and C2 |         |

| Mobile Intel 915GMS Express Chipset  | SL8G9             | C1 and C2 | Pb-free |

| Mobile Intel 910GML Express Chipset  | SL8G5             | C1 and C2 |         |

| Mobile Intel 910GML Express Chipset  | SL8G8             | C1 and C2 | Pb-free |

| Mobile Intel 910GMLE Express Chipset | SLA9L             | C1 and C2 | Pb-free |

Figure 1. Mobile 915PM/GM/GMS/GME & 910GML/GMLE Express Chipset Package Markings

§

## Errata

1. Reported LOs Exit Latency Is Not Updated When PCI Express\* Is Not

**Operating in Common Clock Mode**

Problem: When PCI Express is operating with separate reference clocks, L0s exit latency may be

greater than the setting in the LOs Exit Latency register.

Implication: If the PCI Express link is operating in non-common clock mode, the actual LOs exit

latency may be longer than advertised. In this situation the link will likely enter the

Recovery state before transitioning into the normal LO state.

Workaround: System BIOS can program the appropriate Exit Latency and advertised N\_FTS value if

it detects that the downstream device is not using the common reference clock (indicated in the Slot Clock Configuration bit 12 of the device's Link Status register).

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

2. GMCH Will Not Identify Back-to-Back Malformed Packets

Problem: If the GMCH receives two back-to-back malformed packets, the second malformed

packet is not trapped or logged.

**Implication:** The GMCH will not log or identify the second malformed packet. However, the 1<sup>st</sup>

malformed TLP is logged, and is considered a Fatal Error. Link behavior is not guaranteed at that point whether a 2<sup>nd</sup> malformed TLP is detected or not.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

3. The GMCH Is Limited to Reporting Poisoned TLPs through Standard

**PCI Error Status Reporting Structures**

**Problem:** The GMCH does not set the Non-Fatal Error Detected status bit, in the PCI Express

Device Status register when a poisoned TLP is received.

Implication: Future OS's (that comprehend PCI Express error reporting) will not be notified via

standard PCI Express mechanisms when a poisoned TLP is received.

Workaround: Standard PCI error status reporting must be used for Poisoned TLP reporting. The

reception of Poisoned TLP is reported by hardware setting the Detected Parity Error bit in Device 1, secondary status register, and if so enabled by additionally setting the

Master Data Parity Error bit in the same register.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

4. Incorrect PCI Express Lane Transition after Receiving Several TS1

**Packets**

Problem: If the GMCH receives several TS1 packets with Link and Lane numbers set to PAD,

after 4  $\mu s$  it will time out and transition into configuration state instead of going directly to the Detect state as it should. However, the link will still transition to the

Detect state after timing out of Configuration.

Implication: The GMCH will experience longer latency when transitioning to Detect state.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

5. DMI Link Egress Port Address Is Not Programmable

Problem: The PCI SIG approved ECR 04 to allow future system software (e.g., operating

system) to discover the link structure of the Root Complex. One of the registers in the GMCH that "points" from the DMI port to the ICH cannot be programmed correctly.

Implication: There is no impact on platform functionality. ECR's do not retroactively apply to the

current *PCI Express\* 1.0a Specification* and no existing software understands the Root Topology discovery structures. These structures are implemented in the GMCH only to aid future software development. Such software will need to comprehend the incorrect

pointer

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

6. DDR2 OCD Nonfunctional

**Problem:** During BIOS initialization the GMCH will not be able to adjust and set the DDR2-DRAM

Device DQ/DQS/DQS# buffer impedance.

Implication: Adjustable DQ/DQS/DQS# buffer impedance settings will not be programmed into the

DDR2-DRAM Devices, and the DRAM device OCD default output characteristics will be

used instead.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

7. PCI Express\* Graphics Initiated Snooped Reads to Memory That Are

Fast Dispatched Could Result in Incorrect Data Being Returned

**Problem:** This has only occurred at 1.05-V Core and 533-MHz FSB. GMCH could provide

incorrect data for a PCI Express Graphics initiated memory read.

Implication: Could cause a data miscompare or system hang.

Workaround: It is possible for system BIOS to contain a workaround. Contact your Intel field

representative for more details.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

Specification Update

8. PCI Express Common Mode Voltage Noise Immediately following

**Receiver Detect Sequence**

**Problem:** The PCI Express Common Mode Voltage is not stable immediately after Receiver

Detect Sequence when entering Polling. Active from Detect. Active states.

Implication: Common Mode Voltage noise may result in bit errors early in Polling. Active state. May

result in additional training time before transitioning on to Polling. Configuration.

Performance impact expected to be minimal.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

9. GMCH Does Not Ignore a PCI Express Null Packet

**Problem:** If the GMCH receives a PCI Express Null packet, it should drop the packet and not

perform sequence number checking or respond with any Ack or Nak DLLP. The issue is that the GMCH still performs sequence number checks for Null packets and may

respond with an ACK or NAK depending on the result of the check.

Implication: GMCH may send ACK or NAK DLLPs in response to a Null packet if the sequence

number is not as expected. This may cause unnecessary retries, but Null packets are

expected to be rare on the link.

Workaround: None

18

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

10. Data Payload Byte Count Supplied during an Unsupported Upstream

**Configuration Read Is Not 4 Bytes**

**Problem:** During configuration reads to unsupported PCI Express configuration space, the byte

count for data payload is not 4.

Implication: Data payload byte count is 5 and not the expected 4.

Workaround: Do not perform unsupported upstream PCI Express configuration cycles.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

11. PCI Express Replay Timer Register Default Setting Is Incorrect

**Problem:** The default Replay timer value is too aggressive and does not properly account for L0s

exit latency or internal pipeline delays. As a result the GMCH may initiate a replay

sooner than expected.

Implication: The GMCH may initiate a replay sooner than expected. This should not happen as long

as the downstream device complies with the PCI Express Ack Latency requirement.

Workaround: It is possible for BIOS to contain a workaround. Contact your Intel Field

Representative for more details.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

12. E\_SMERR Bit Set Incorrectly

**Problem:** The E\_SMERR bit may be incorrectly set when performing valid accesses to SMM

space.

Implication: If this bit is used by the SMI handler to determine cache line flushes, unnecessary

cache line flushes may occur when in SMM mode. A slight performance impact to the

SMI handler may result from unnecessary cache line flushes.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

13. PCI Express\* Lane 3 Bit Errors Occur on a Small Percentage of GMCH

**B-1 Units on Certain Boards**

Problem: On systems with External Graphics, a small percentage of GMCH B-1 units may

experience bit-errors on PCI Express lane 3 on certain boards. To date, we have only seen these bit errors on internal test (SV) boards at nominal core voltage (1.05 V).

Implication: A significant level of bit errors could lead to link retraining, link down, or hang

conditions. Intel is currently trying to understand the variables that affect the bit error rate. All samples shipped outside of Intel have been screened for this issue and Intel has not seen any system hangs with screened parts. *PCI Express x16 Graphics not*

supported on Mobile Intel 915GM/GME B1 stepping.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

14. Pixel Discoloration Seen When Intel® Dual Frequency Graphics

Technology (DFGT) Is Enabled

Problem: Pixel discoloration seen when Intel Dual Frequency Graphics Technology (Intel DFGT)

is enabled. Root caused to the internal render clocks getting misaligned during the

frequency switching.

Implication: Pixel discoloration seen on display.

Workaround: Disable the DFGT feature through VBT.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

15. System Hang with DDR-333 Memory When Intel® Rapid Memory

Power Management Is Enabled during C2/C3/C4

Problem: DDR333 systems may not exit self refresh state when memory self refresh is enabled

during C2/C3/C4.

Implication: System may hang.

Workaround: None.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

16. Display becomes a Solid Color with Intel® Smart 2D Display

Technology (Intel® S2DDT) Enabled

Problem: If Memory Self-Refresh during C3 (C3SR) occurs when the Intel Smart 2D Display

Technology (Intel S2DDT) recompresses at the start of a frame, the graphics engine may use the uncompressed frame instead of the recompressed frame. The issue may

occurs if the system is left idle (>20 minutes) with Intel S2DDT.

Implication: Display becomes a solid color or may cause a system hang.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

17. PCI Express Scrambling

**Problem:** While entering the Recovery state, 915PM/GM/GME PCI Express discrete graphics port

stops scrambling two symbols before the first TS (training sequence).

Implication: When these non-scrambled symbols are received by the endpoint, the de-scrambler of

the endpoint will observe two symbols of random data. The first symbol of TS1 will reset the endpoint's de-scrambler so that the endpoint should recognize the TS1 and TS2 ordered-sets being transmitted and move into the Recovery state as planned. There is no system level impact if the endpoint is PCI Express Specification 1.0a

compliant in ignoring the random data.

Workaround: None

**Problem:** For the steppings affected, see the *Summary Tables of Changes*.

18. Macrovision Failure for 480p / 576p Modes

**Problem:** GMCH does not encode Macrovision (content protection) properly for 480p and 578p

progressive modes and does not meet the Macrovision specification for these modes.

480p and 576p progressive modes will not pass MacroVision certification.

Implication: No DVD playback supported/available for these modes, other progressive scan modes

are not affected.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

19. Thermometer Read Register is Non-Functional with Negative

**Calibration Offset**

Problem: When initializing the Thermometer counter, a negative offset will cause an overflow

condition, causing the counter to stop. The GMCH will not update the Thermometer Read Register (TRR) register with the correct temperature trending values and the TRR will display "FF". All other thermal sensor features will still work (throttling, trip

points and interrupts) since these do not use the thermometer mode.

Implication: Thermometer Read Register (TRR) is not functional with negative Thermal Calibration

Offset value (TCO).

Workaround: Please contact your Intel representative for the latest information.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

20. Potential Electrical Spec Violation if an SO-DIMM Is Only Populated in

**Channel B**

**Problem:** When DDR or DDR2 memory devices are present on channel B, but not channel A,

memory control logic only looks at channel A and incorrectly performs Rcomp value

update. This could cause an electrical spec violation internal to the chip.

Implication: System with 915PM/GM/GME, or 910GML/GMLE may hang or experience other

anomalous system behavior. No impact on system with 915GMS.

Workaround: It is possible for BIOS to contain a workaround. Contact your Intel Field

Representative for more details.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

21. LVDS Panel Power Down Timing Violation during System Reset

Problem: During system reset, there is insufficient time for handshake between ICH and GMCH

LVDS logic. As a result, timing from panel backlight enable going low to LVDS data going low (TX) and timing from LVDS data going low to panel VCC enable going low (T3) do not match the programmed values. Panel backlight enable (LBKLT\_EN), panel

Vcc enable (LVDD\_EN) and LVDS data lines go low at the same time.

Implication: No system level issues have been observed.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

22. PCI Express SKP/InitFCx Contention

**Problem:** During GMCH PCI Express initialization, if a SKP is being transmitted immediately

before an InitFCx DLLP, then a partial InitFCx may be transmitted.

Implication: A slight delay (less than 100 ns) may occur during link initialization. Device may

report correctable error. InitFCx will automatically be repeated.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*

23. SMVREF High Current Draw

**Problem:** When SMOCDCOMP[1:0] are connected to ground (either directly or through a pull-

down resistor), SMVREF[1:0] may draw significantly more current than specified. If the corresponding voltage supply is not capable of handling the resulting current, the

SMVREF[1:0] voltage will droop below specification.

Implication: If SMVREF[1:0] droops below specification, the system may hang. Failure observed

during S3 only.

Workaround: Leave SMOCDCOMP[1:0] as NC (No Connect) for both DDR and DDR2 designs. This

limits the maximum current draw on SMVREF[1:0] to 200 µA (i.e. 100uA/pin). In

addition, use a voltage supply that can supply at least 200 µA (total) for

SMVREF[1:0].

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

24. Mobile Intel 915GM/GMS/GME and 910GML/GMLE Express Chipset

**Graphics Clock Crossing Issue**

**Problem:** While attempting to launch or exit an application that uses the overlay engine (e.g.

media playback software running a video clip), the system may hang (blue screen) or screen resolution may change to VGA mode. This event may occur when a signal pulse is missed inside the chip due to synchronization of the graphics render and display

clocks while graphics overlay mode is being turned off.

Implication: Failure is difficult to reproduce because this event only occurs under a very rare but

valid timing condition where graphics render and display clocks are aligned while the graphics overlay is being turned off. System will hang or screen resolution may change to VGA mode when launching or exiting an application that uses the overlay engine. Mobile Intel 915GM/GMS/GME and 910GML/GMLE platforms that use render

clock at 166 MHz are not affected by this sighting.

Workaround: It is possible for BIOS to contain a workaround. Contact your Intel Field

Representative for more details.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

25. Mobile Intel 915PM/GM/GMS/GME and 910GML/GMLE Express Chipset Memory Refresh Queue

Problem: When thermal based throttling is enabled, memory refresh commands get queued up

inside MCH/GMCH. As a result, MCH/GMCH may not perform memory refresh commands at a frequency needed by memory devices. Thermal based throttling happens only when either using the on-die memory thermal sensors or the external

thermal sensor.

Implication: When not enough refresh commands are issued to system memory to retain memory

content, data loss may occur. System is more susceptible to this issue when memory

devices approach temperature limit.

Workaround: It is possible for system BIOS to contain a workaround. Contact your Intel field

representative for more details.

**Status:** For affected steppings, see the *Summary Tables of Changes*.

26. Packet Dropped When Replay Timer Expires and Replay Is in Progress

Problem: When a packet replay is in progress on the PCI Express Port, and if some but not all of

the packets to be replayed are acknowledged and the replay timer expires on the same clock cycle as the replay start of the first unacknowledged packet, the next packet in the replay buffer may be sent with an old sequence number. That packet is

seen by receiver side as a duplicate and subsequently dropped.

Note: This has only been reproduced in a synthetic test environment.

**Implication:** Anomalous behavior may result if all of the above conditions are met.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

27. LOCK to non-DRAM Memory Flag (Register Dev 0, Fun 0, Offset C8, Bit

9) Is Getting Asserted

Problem: A CPU lock cycle request is unintentionally being recognized as request to a non-

system memory destination.

Implication: The GMCH may incorrectly flag an error for a valid lock cycle that targets DRAM. A

System Error (SERR) may be generated if enabled by System BIOS.

Note: The default setting for ERRCMD[9] Bus 0 Device 0 Offset CAh is to

disable this reporting.

Workaround: Do not enable or change default setting of ERRCMD[9] Bus 0 Device 0 Offset CAh

(SERR reporting for Lock cycles to non-DRAM Memory)

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

28. Mobile Intel 915GM/GMS/GME and 910GML/GMLE Express Chipset

LVDS - CRT Switching

**Problem:** 915GM/GMS/GME and 910GML/GMLE LVDS interface may hang while switching

between LVDS and CRT outputs.

**Implication:** Once LVDS interface hangs a system reset is required.

Workaround: Fixed in VBIOS, Please refer to release notes for VBIOS version 1220 or Newer.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

29. Mobile Intel 915GM/GMS/GME and 910GML/GMLE Express Chipset

**LVDS Vos**

Problem: On some Mobile Intel 915GM/GMS/GME and 910GML/GMLE Express devices, one or

more LVDS lanes may exceed Intel's Vos specification limits.

LVDS Interface: Functional Operating Range (VCC= 2.5V ±5%)

| Symbol                  | Parameter         | Min   | Nom  | Max   | Unit |

|-------------------------|-------------------|-------|------|-------|------|

| V <sub>OS(Tested)</sub> | Offset<br>Voltage | 0.700 | 1.25 | 1.600 | V    |

| V <sub>OS (Spec)</sub>  | Offset<br>Voltage | 1.125 | 1.25 | 1.375 | V    |

NOTES: Table reflects Intel tested Vos specification limits and the Mobile Intel

915GM/GMS/GME & 910GML/GMLE specification for Vos values. Intel may make changes to specifications, release dates and product descriptions from time to time.

Implication: LVDS Panels sensitive to Vos range may not detect transmitted LVDS data. Potential

visual anomalies on LVDS display panels may occur, although no visual anomalies

have been reported due to Vos levels in the above tested range.

Workaround: None

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

#### 30. Mobile Intel 915PM/GM/GME Express Chipset x1 False Detect

**Problem:** 915PM/GM/GME may falsely detect the presence of a PCIe endpoint while operating in PCIe Low Power Mode.

- False detect may occur for 915PM/GM/GME systems supporting x1 only endpoints.

- False detect may occur on PCIe\* lanes 1 through 15 for a graphics endpoint when switching from x16 to x1.

Implication: Systems may become inoperable when an endpoint is operating in x1 mode.

- The scenario occurs because false detection of a PCIe endpoint occurs on one or more lanes resulting in the GMCH's PCIe interface erroneously entering and looping continuously in Polling. Compliance.

- When an endpoint is operating in x1 mode, the scenario may occur at boot or during any subsequent attempt to retrain the link.

Workaround: For systems requiring x1 PCIe link operation:

- <u>Systems operating in x1 mode only</u>: It is possible for system BIOS to contain a workaround. Contact your Intel field representative for more details.

- Systems requiring run-time switching between x16 and x1 operation: A graphics driver workaround has been defined. Please contact your graphic's controller vendor for driver status.

- Use the erratum title when contacting graphic's controller vendor for driver status.

- For questions pertaining to the erratum or workaround please contact your Intel representative.

**Status:** For the steppings affected, see the *Summary Tables of Changes*.

## 31. Mobile Intel 915PM/GM/GME Express Chipset PCI Express Ztx\_diff\_dc Impedance Violation

**Problem:** 915PM/GM violates the PCI Express Ztx\_diff\_dc max impedance specification.

Implication: None

- No failures have been observed due to the violation of the PCI Express Ztx\_diff\_dc impedance specification.

- PCI Express Tx\_eye signal integrity specifications are still met.

Workaround: None

**Status:** For affected steppings, see the *Summary Tables of Changes*.

32. Mobile Intel 915PM/GM/GMS/GME and 910GML/GMLE Express

**Chipset DRAM Clock to CKE Power-up Timing**

**Problem:** During memory power-up and initialization, the timing between DRAM clock

stabilization to CKE going high is observed to be minimum of 35 ns against the JEDEC

spec of 200 µs.

Implication: None. No functional failures have been observed.

Intel has characterized the timing and shared the data with major DRAM suppliers.

Intel has determined and major DRAM suppliers agree that DRAM devices need

35 ns. This erratum should not cause memory-clock functionality or timing related issues. Please refer to latest Intel DRAM spec Addendum for power-up and

initialization timing requirements available at

http://developer.intel.com/technology/memory/#Specs

Workaround: None.

**Status:** For affected steppings, see the *Summary Tables of Changes*.

33. Mobile Intel 915PM/GM/GMS/GME and 910GML/GMLE Express

Chipset SMRAM D\_CLS Bit

Problem: Data and stack which residing in Extended SMRAM (TSEG/HSEG) is inaccessible if

D\_CLS bit (Bus 0, Device 0, Function 0, Register 9Dh, Bit 5) is set.

Implication: May result in system hang.

Workaround: It is possible for system BIOS to contain a workaround. Contact your Intel field

representative for more details.

**Status:** No Fix. For steppings affected, see the *Summary Tables of Changes*.

ş

## Specification Changes

#### 1. Graphics Core Clock Frequency Update

The following section replaces the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet*, Section 10.14.3.

# 10.14.3.1 Intel 915GM/GME Express Chipset Host/Memory/Graphics Clock Support

Table 10-16a. Intel 915GM/GME Express Chipset Graphics Clock Frequency Support at 1.05 V

| Host              | Memory              | 2D Display clock | 3D Render<br>Clock |

|-------------------|---------------------|------------------|--------------------|

| 400 MHz           | DDR 333             | 200              | 166                |

| 400 MHz           | DDR 333             | 213              | 200                |

| 533 MHz           | DDR 333             | 190              | 166                |

| 533 MHz           | DDR 333             | 213              | 190                |

| 400 MHz / 533 MHz | DDR2 400 / DDR2 533 | 200              | 160                |

| 400 MHz / 533 MHz | DDR2 400 / DDR2 533 | 213              | 200                |

**NOTE:** Mobile Intel 915GM/ 915GME / 910GML / 910GMLE Express Chipset will remove support for 133 MHz for both graphics render and display clock due to graphics clock crossing issue (Errata #24).

Table 10-16b. Intel 915GM/GME Express Chipset Graphics Clock Frequency Support at 1.5 V

| Host              | Memory              | 2D Display<br>clock | 3D Render<br>Clock |

|-------------------|---------------------|---------------------|--------------------|

| 400 MHz / 533 MHz | DDR2 400 / DDR2 533 | 200                 | 160                |

| 400 MHz / 533 MHz | DDR2 400 / DDR2 533 | 213                 | 200                |

| 400 MHz / 533 MHz | DDR2 400 / DDR2 533 | 333                 | 333                |

**NOTE:** Mobile Intel 915GM/GME/ 910GML/GMLE does not support DDR333 if chipset core voltage is designed for 1.5 V.

# 10.14.3.2 Intel 915GMS Express Chipset Host/Memory/Graphics Clock Support

## Table 10-17. Intel 915GMS Express Chipset Graphics Clock Frequency Support at 1.05 V

| Host    | Memory   | 2D Display<br>Clock | 3D Render<br>Clock |

|---------|----------|---------------------|--------------------|

| 400 MHz | DDR2 400 | 152                 | 133                |

| 400 MHz | DDR2 400 | 200                 | 160                |

# 10.14.3.3 Intel 910GML/GMLE Express Chipset Host/Memory/Graphics Clock Support

Table 10-18. Intel 910GML/GMLE Express Chipset Graphics Clock Frequency Support at 1.05 V

| Host    | Memory   | 2D Display<br>Clock | 3D Render<br>Clock |  |

|---------|----------|---------------------|--------------------|--|

| 400 MHz | DDR 333  | 200                 | 166                |  |

| 400 MHz | DDR2 400 | 200                 | 160                |  |

## 2. Intel 915GM/GME Express Chipset Host/Memory/Graphics Clock Support Update

Table 10-16 and Table 10-7 incorrectly state support for Display clocks for 400 MHz / DDR333 and 533 MHz/DDR333 frequency combinations. These combinations will result with a Display clock of 222 MHz. See Specification Change Item #1 above and Documentation Change #4 for updated information in grey shaded text.

## 3. Mobile Intel 915GM/GMS/GME and 910GML/GMLE Express Chipset Display and Render Clock Support Update

The following section replaces the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet, Graphics Clock Frequency Feature* section, on page 22.

- 2D Display core frequency at 190/200 or 213/222 MHz @ Vcc=1.05 V depending on the host/memory configurations

- 3D Render core frequency at 160/166 or 190/200 MHz @ Vcc=1.05 V depending on the host/memory configurations

- 2D Display core frequency at 200, 213 or 333 MHz @ Vcc=1.5 V depending on the host/memory configurations

- 3D Render core frequency at 166, 200 or 333 MHz @ Vcc=1.5 V depending on the host/memory configurations

The following section replaces the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet, Graphics Clock Frequency Feature* section, on page 25.

- 2D Display core frequency at 152 or 200 MHz @ Vcc=1.05 V depending on the host/memory configurations

- 3D Render core frequency at 133 or 160 MHz @ Vcc=1.05 V depending on the host/memory configurations

The following section replaces the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet, Graphics Clock Frequency Feature* section, on page 26.

- 2D Display core frequency at 200 MHz @ Vcc=1.05 V depending on the host/memory configurations

- 3D Render core frequency at 160/166 MHz @ Vcc=1.05 V depending on the host/memory configurations

## 4. Mobile Intel 910GML/GMLE Express Chipset Memory Channel Organization Support Update

The following section replaces the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet* in the *Mobile Intel 910GML Express Chipset Feature* section, on page 26 and in Section 10.2.

- Memory channel organization support for DDR is:

- Single Channel Mode

- Memory channel organization support for DDR2 is:

- Dual Channel Asymmetric Mode only

**Note:** Dual Channel Symmetric (Interleave) Mode not supported on Mobile Intel 910GML/GMLE Express Chipset

The following bullet replaces the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet*, Section 10.2, *System Memory Controller*.

Dual Channel Symmetric (Interleave) Mode not supported for Mobile Intel 910GML/GMLE Express Chipset.

§

## Specification Clarifications

#### 1. Slow DMA Transfers for LPC Devices

8-bit DMA transfers to some LPC devices, may incur latencies, that result in a slowed down transfer rate. Longer latencies may occur when the platform becomes idle and the GMCH dynamically asserts HCPUSLP# for Processor C2 states.

For example, a 4-Mbps FIR device may transmit faster than the resulting 8-bit DMA transfer rate resulting in data retransmission and lower FIR throughput.

So as not to impede the transfer rate of certain LPC Devices, the dynamic assertion of HCPUSLP# by GMCH during Processor C2 states can be disabled. Contact your Intel field representative for more details on how to disable HCPUSLP# assertion during C2 states

## 2. Dynamic Video Memory Technology (DVMT) 3.0 Support Configurations

The following note should be added to Section 1.1 of the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet:*

Please contact your local Intel field representative for additional information regarding DVMT 3.0 support configurations.

§

# **Documentation Changes**

#### 1. DRAM Enhanced Addressing Update

The following section is inserted into the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet* Chapter 10, Section 10.2.1.3

### 10.2.1.3 DRAM Address Mapping

Enhanced Addressing swaps the most significant bit controlling one of the Sx\_BS lines with bit 18 (which normally controls row address bit 2). Without Enhanced Addressing, rank bits are the most significant two bits of the address. With Enhanced Addressing, the rank bits are always bits 19 and 20.

Table 10-8 DRAM Device Configurations – Dual Channel Asymmetric Mode w/Enh. Addr. Swap (0)

| Technology<br>(Mb)  | 256          | 256  | 512  | 512  | 512  | 512   | 1024  | 1024  | 1024 | 1024  |

|---------------------|--------------|------|------|------|------|-------|-------|-------|------|-------|

| Row bits            | 13           | 13   | 13   | 13   | 13   | 14    | 14    | 14    | 13   | 14    |

| Column bits         | 9            | 10   | 10   | 11   | 10   | 10    | 10    | 11    | 10   | 10    |

| Bank bits           | 2            | 2    | 2    | 2    | 2    | 2     | 2     | 2     | 3    | 3     |

| Width (b)           | 16           | 8    | 16   | 8    | 16   | 8     | 16    | 8     | 16   | 8     |

| Rows                | 8192         | 8192 | 8192 | 8192 | 8192 | 16384 | 16384 | 16384 | 8192 | 16384 |

| Columns             | 512          | 1024 | 1024 | 2048 | 1024 | 1024  | 1024  | 2048  | 1024 | 1024  |

| Banks               | 4            | 4    | 4    | 4    | 4    | 4     | 4     | 4     | 8    | 8     |

| Page Size (KB)      | 4            | 8    | 8    | 16   | 8    | 8     | 8     | 16    | 8    | 8     |

| Devices per rank    | 4            | 8    | 4    | 8    | 4    | 8     | 4     | 8     | 4    | 8     |

| Rank Size<br>(MB)   | 128          | 256  | 256  | 512  | 256  | 512   | 512   | 1024  | 512  | 1024  |

| Depth (M)           | 16           | 32   | 32   | 64   | 32   | 64    | 64    | 128   | 64   | 128   |

| Addr bits [n:0]     | 26           | 27   | 27   | 28   | 27   | 28    | 28    | 29    | 28   | 29    |

| Available in DDR    | yes          | yes  | yes  | yes  | no   | no    | yes   | yes   | no   | no    |

| Available in DDRII  | yes          | yes  | no   | no   | yes  | yes   | no    | No    | yes  | yes   |

| Host Address<br>bit | Mem Addr-bit |      |      |      |      |       |       |       |      |       |

| 31                  | 1            | -    | -    | -    | 1    | -     | -     | -     | -    | -     |

| 30                  | -            | -    | -    | -    | -    | -     | -     | r 3   | -    | r 3   |

| 29                  | -            | -    | -    | r 3  | -    | r 3   | r 3   | r 13  | r 3  | r 13  |

|                     |              |      |      |      |      |       |       |       |      |       |

|    | •    |      |      |      |      | •    |      | •    |      |      |

|----|------|------|------|------|------|------|------|------|------|------|

| 28 | -    | r 3  | r 3  | r 11 | r 3  | r 13 | r 13 | r 11 | r 11 | r 11 |

| 27 | r 3  | r 12 |

| 26 | r 10 |

| 25 | r 9  | r 9  | r 9  | r 9  | r 9  | r 9  | r 9  | r 9  | r 9  | r 9  |

| 24 | r 8  | r 8  | r 8  | r 8  | r 8  | r 8  | r 8  | r 8  | r 8  | r 8  |

| 23 | r 7  | r 7  | r 7  | r 7  | r 7  | r 7  | r 7  | r 7  | r 7  | r 7  |

| 22 | r 6  | r 6  | r 6  | r 6  | r 6  | r 6  | r 6  | r 6  | r 6  | r 6  |

| 21 | r 5  | r 5  | r 5  | r 5  | r 5  | r 5  | r 5  | r 5  | b 2  | b 2  |

| 20 | r 4  | r 4  | r 4  | r 4  | r 4  | r 4  | r 4  | r 4  | r 4  | r 4  |

| 19 | s 0  | s 0  | s 0  | s 0  | s 0  | s 0  | s 0  | s 0  | s 0  | s 0  |

| 18 | b 1  | b 1  | b 1  | b 1  | b 1  | b 1  | b 1  | b 1  | b 1  | b 1  |

| 17 | r 1  | r 1  | r 1  | r 1  | r 1  | r 1  | r 1  | r 1  | r 1  | r 1  |

| 16 | r 0  | r 0  | r 0  | r 0  | r 0  | r 0  | r 0  | r 0  | r 0  | r O  |

| 15 | r 11 | r 11 | r 11 | r 2  | r 11 | r 11 | r 11 | r 2  | r 5  | r 5  |

| 14 | r 12 | r 2  | r 2  | b 0  | r 2  | r 2  | r 2  | b 0  | r 2  | r 2  |

| 13 | r 2  | b 0  | b 0  | c 11 | b 0  | b 0  | b 0  | c 11 | b 0  | b 0  |

| 12 | b 0  | с 9  | с 9  | c 9  | с 9  | с 9  | с 9  | с 9  | c 9  | с 9  |

| 11 | c 8  | c 8  | c 8  | c 8  | c 8  | c 8  | c 8  | c 8  | c 8  | c 8  |

| 10 | c 7  | c 7  | c 7  | c 7  | c 7  | c 7  | c 7  | c 7  | c 7  | c 7  |

| 9  | с 6  | с 6  | с 6  | с 6  | с 6  | с 6  | с 6  | c 6  | с 6  | с 6  |

| 8  | c 5  | c 5  | c 5  | c 5  | c 5  | c 5  | c 5  | c 5  | c 5  | c 5  |

| 7  | с 4  | с 4  | с 4  | с 4  | с 4  | c 4  | c 4  | c 4  | c 4  | c 4  |

| 6  | с 3  | с 3  | с 3  | с 3  | с 3  | с 3  | с 3  | с 3  | с 3  | с 3  |

| 5  | c 2  | c 2  | c 2  | c 2  | c 2  | c 2  | c 2  | c 2  | c 2  | c 2  |

| 4  | c 1  | c 1  | c 1  | c 1  | c 1  | c 1  | c 1  | c 1  | c 1  | c 1  |

| 3  | c 0  | c 0  | c 0  | c 0  | c 0  | c 0  | c 0  | c 0  | c 0  | c 0  |

|    |      |      |      |      |      |      |      |      |      |      |

Table 10-9 DRAM Device Configurations -Dual Channel Interleaved Mode w/ Enh. Addr. Swap (0)

| Technology (Mb)     | 256  | 256  | 512  | 512  | 512  | 512     | 1024  | 1024  | 1024 | 1024  |

|---------------------|------|------|------|------|------|---------|-------|-------|------|-------|

| Row bits            | 13   | 13   | 13   | 13   | 13   | 14      | 14    | 14    | 13   | 14    |

| Column bits         | 9    | 10   | 10   | 11   | 10   | 10      | 10    | 11    | 10   | 10    |

| Bank bits           | 2    | 2    | 2    | 2    | 2    | 2       | 2     | 2     | 3    | 3     |

| Width (b)           | 16   | 8    | 16   | 8    | 16   | 8       | 16    | 8     | 16   | 8     |

| Rows                | 8192 | 8192 | 8192 | 8192 | 8192 | 16384   | 16384 | 16384 | 8192 | 16384 |

| Columns             | 512  | 1024 | 1024 | 2048 | 1024 | 1024    | 1024  | 2048  | 1024 | 1024  |

| Banks               | 4    | 4    | 4    | 4    | 4    | 4       | 4     | 4     | 8    | 8     |

| Page Size (KB)      | 4    | 8    | 8    | 16   | 8    | 8       | 8     | 16    | 8    | 8     |

| Devices per rank    | 4    | 8    | 4    | 8    | 4    | 8       | 4     | 8     | 4    | 8     |

| Rank Size<br>(MB)   | 128  | 256  | 256  | 512  | 256  | 512     | 512   | 1024  | 512  | 1024  |

| Depth (M)           | 16   | 32   | 32   | 64   | 32   | 64      | 64    | 128   | 64   | 128   |

| Addr bits [n:0]     | 26   | 27   | 27   | 28   | 27   | 28      | 28    | 29    | 28   | 29    |

| Available in DDR    | yes  | yes  | yes  | yes  | no   | no      | yes   | Yes   | no   | no    |

| Available in DDRII  | yes  | yes  | no   | no   | yes  | yes     | no    | No    | yes  | yes   |

| Host Address<br>bit |      |      |      |      | Mem  | Addr-bi | t     |       |      |       |

| 31                  | -    | -    | -    | -    | -    | -       | -     | r 3   | -    | r 3   |

| 30                  | -    | -    | -    | r 3  | -    | r 3     | r 3   | r 13  | r 3  | r 13  |

| 29                  | -    | r 3  | r 3  | r 11 | r 3  | r 13    | r 13  | r 11  | r 11 | r 11  |

| 28                  | r 3  | r 12    | r 12  | r 12  | r 12 | r 12  |

| 27                  | r 10    | r 10  | r 10  | r 10 | r 10  |

| 26                  | r 9  | r 9  | r 9  | r 9  | r 9  | r 9     | r 9   | r 9   | r 9  | r 9   |

| 25                  | r 8  | r 8  | r 8  | r 8  | r 8  | r 8     | r 8   | r 8   | r 8  | r 8   |

| 24                  | r 7  | r 7  | r 7  | r 7  | r 7  | r 7     | r 7   | r 7   | r 7  | r 7   |

| 23                  | r 6  | r 6  | r 6  | r 6  | r 6  | r 6     | r 6   | r 6   | r 6  | r 6   |

| 22                  | r 5  | r 5  | r 5  | r 5  | r 5  | r 5     | r 5   | r 5   | b 2  | b 2   |

| 21                  | r 4  | r 4  | r 4  | r 4  | r 4  | r 4     | r 4   | r 4   | r 4  | r 4   |

| 20                  | s 0  | s 0  | s 0  | s 0  | s 0  | s 0     | s 0   | s 0   | s 0  | s 0   |

| 19                  | b 1  | b 1  | b 1  | b 1  | b 1  | b 1     | b 1   | b 1   | b 1  | b 1   |

| 18                  | r 1  | r 1  | r 1  | r 1  | r 1  | r 1     | r 1   | r 1   | r 1  | r 1   |

| 17                  | r 0  | r 0  | r 0  | r 0  | r 0  | r 0     | r 0   | r 0   | r 0  | r 0   |

| 16                  | r 11 | r 11 | r 11 | r 2  | r 11 | r 11    | r 11  | r 2   | r 5  | r 5   |

| 15                  | r 12 | r 2  | r 2  | b 0  | r 2  | r 2     | r 2   | b 0   | r 2  | r 2   |

| 14 | r 2 | b 0 | b 0 | c 11 | b 0 | b 0 | b 0 | c 11 | b 0 | b 0 |

|----|-----|-----|-----|------|-----|-----|-----|------|-----|-----|

| 13 | b 0 | с 9 | с 9 | с 9  | c 9 | с 9 | с 9 | с 9  | с 9 | с 9 |

| 12 | c 8 | c 8 | c 8 | c 8  | c 8 | c 8 | c 8 | c 8  | c 8 | c 8 |

| 11 | c 7 | c 7 | c 7 | c 7  | c 7 | c 7 | c 7 | c 7  | c 7 | c 7 |

| 10 | с 6 | с 6 | с 6 | с 6  | с 6 | с 6 | с 6 | с 6  | с 6 | с 6 |

| 9  | c 5 | c 5 | c 5 | c 5  | c 5 | c 5 | c 5 | c 5  | c 5 | c 5 |

| 8  | c 4 | c 4 | c 4 | c 4  | c 4 | c 4 | c 4 | c 4  | c 4 | c 4 |

| 7  | с 3 | с 3 | с 3 | c 3  | c 3 | с 3 | с 3 | с 3  | с 3 | с 3 |

| 6  | h   | h   | Н   | h    | h   | h   | h   | Н    | h   | h   |

| 5  | c 2 | c 2 | c 2 | c 2  | c 2 | c 2 | c 2 | c 2  | c 2 | c 2 |

| 4  | c 1 | c 1 | c 1 | c 1  | c 1 | c 1 | c 1 | c 1  | c 1 | c 1 |

| 3  | c 0 | c 0 | c 0 | c 0  | c 0 | c 0 | c 0 | c 0  | c 0 | c 0 |

#### 2. Section 5.2.15 CODRC1 – Channel 0 DRAM Controller Mode 1

The following register bits definition replaces the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet, Section 5.2.15*

#### 5.2.15 CODRC1—Channel O DRAM Controller Mode 1

PCI Device: MCHBAR

Address Offset: 124h

Default Value: 00000000h

Access: RO, R/W

Size: 32 bits

| Bit | Access<br>and<br>Default | Description                                                                                                    |  |  |  |  |

|-----|--------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     |                          | Swap Mode Enable:                                                                                              |  |  |  |  |

| 31  | R/W                      | 0 = Swap mode disabled. Dram Address Map Follows the standard address map described in the EDS.                |  |  |  |  |

|     | 0 b                      | 1 = Swap mode enabled. This bit can be enabled if all dimm are either single sided or symmetrically populated. |  |  |  |  |

| 30  | R/W                      | Reserved                                                                                                       |  |  |  |  |

| 30  | 0 b                      |                                                                                                                |  |  |  |  |

|     | R/W                      | Address Swap Mode:                                                                                             |  |  |  |  |

| 29  | 00 b                     | 0 = Swap Enabled for Bank Selects and Rank Selects.                                                            |  |  |  |  |

|     | 00 0                     | 1 = Swap Enabled for Bank Selects only.                                                                        |  |  |  |  |

| Bit   | Access<br>and<br>Default | Description                                             |                                |                     |                     |                     |                |     |  |  |  |

|-------|--------------------------|---------------------------------------------------------|--------------------------------|---------------------|---------------------|---------------------|----------------|-----|--|--|--|

| 20.27 | RO                       | Reserved                                                |                                |                     |                     |                     |                |     |  |  |  |

| 28:27 | 0 b                      |                                                         |                                |                     |                     |                     |                |     |  |  |  |

|       |                          | Swap Addr                                               | Swap Address Selection:        |                     |                     |                     |                |     |  |  |  |

|       |                          | Single Cha                                              | nnel and As                    | ymm-Stack           | ced Dual Ch         | nannel:             |                |     |  |  |  |

|       |                          | Mode                                                    | Rank<br>Select                 | Bank<br>Select<br>0 | Bank<br>Select<br>1 | Bank<br>Select<br>2 | Dimm<br>Select |     |  |  |  |

|       |                          | 000                                                     | A19                            | std                 | A18                 | A21                 | A20            |     |  |  |  |

|       |                          | 001                                                     | A20                            | std                 | A19                 | A22                 | A21            |     |  |  |  |

|       |                          | 010                                                     | A18                            | std                 | A17                 | A20                 | A19            |     |  |  |  |

|       |                          |                                                         | 011                            | A17                 | Std                 | A16                 | A19            | A18 |  |  |  |

|       | R/W                      | Others                                                  | Rsvd.                          | Rsvd.               | Rsvd.               | Rsvd.               |                |     |  |  |  |

| 26:24 | 000 b                    | Recommended Priority: 0, 1, 2  Dual Channel Interleaved |                                |                     |                     |                     |                |     |  |  |  |

|       |                          | Mode                                                    | Rank<br>Select                 | Bank<br>Select<br>0 | Bank<br>Select<br>1 | Bank<br>Select<br>2 | Dimm<br>Select |     |  |  |  |

|       |                          | 000                                                     | A20                            | std                 | A19                 | A22                 | A21            |     |  |  |  |

|       |                          | 001                                                     | A21                            | Std                 | A20                 | A23                 | A22            |     |  |  |  |

|       |                          | 010                                                     | A19                            | std                 | A18                 | A21                 | A20            |     |  |  |  |

|       |                          | 011 A18 std A17 A20                                     |                                |                     |                     |                     |                |     |  |  |  |

|       |                          | Others                                                  | Others Rsvd. Rsvd. Rsvd. Rsvd. |                     |                     |                     |                |     |  |  |  |

|       |                          | Recommend                                               | led Priority:                  | 2, 3, 0             |                     |                     |                |     |  |  |  |

#### 3. Section 5.2.31 DCC – DRAM Channel Control

The following register bits definition replaces the *Mobile Intel® 915 and 910 Express Chipset Family of Products Datasheet;* Section 5.2.31

### Section 5.2.31 DCC—DRAM Channel Control

MMIO Range: MCHBAR Address Offset: 200h

Default Value: 00000000h

Access: RO, R/W

Size: 32 bits

This register controls how the DRAM channels work together. It affects how the CxDRB registers are interpreted and allows them to steer transactions to the correct channel.

| Bit | Access<br>and<br>Default | Description                                                                                                                                                                                                                          |

|-----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | R/W<br>O b               | Channel XOR Randomization Disable (CXRDIS): When enabled, the DRAM Controller will try to spread page accesses evenly among the channels by including more address bits in the choice for which channel holds the requested address. |

|     |                          | 0: Channel XOR Randomization is enabled. CXRSEL's bit will be XORed with CHSEL's bit to pick the channel for a given address.                                                                                                        |

|     |                          | 1: Channel XOR Randomization is disabled                                                                                                                                                                                             |

| 9   | R/W                      | Channel XOR Randomization Control Bit (CXRSEL): When Channel                                                                                                                                                                         |

|     | 0 b                      | XOR Randomization is in use (see CXRDIS), the channel select will be randomized by XORing it with either host address bit 11 or 17.                                                                                                  |

|     |                          | 0: Bit 11 will be XORed with the Channel Select bit                                                                                                                                                                                  |

|     |                          | 1: Bit 17 will be XORed with the Channel Select bit                                                                                                                                                                                  |

## 4. Section 7.2.33 GCFGC – Graphics Clock Frequency and Gating Control