# intel

- High Quality Display for Text and Graphics Applications

- Provides Proportional Spacing, Simultaneous Superscript/Subscript, Soft Font Support and Bit Map Graphics

- High Performance Manipulation of Text/Graphics Strings

- Programmable Bus Interface Handles 8 or 16 Bit Data and 16 or 32 Bit Addressing; iAPX 86/88/186/188 Compatible

- On-Chip Processing Unit Simplifies Software Design by Executing High Level Commands and Supporting Linked List Data Structures

- Extremely Flexible; Programmable Features Include Screen and Row Formats, Two Cursors, Character and Field Attributes and Smooth Scrolling

- Supports Multiple Windows

- High Resolution Display; Up to 200 Characters/Graphics Cells per Row and 2048 Scan Lines per Frame

- Separate Bus and Video Clocks Allow Optimization of Overall System Performance

- Provides a Complete LSI Solution for Display Control when Used in Conjunction with the 82731 Video Interface Controller

- 68 Pin JEDEC Package: (See Intel packaging: Order Number: 210931-004)

The 82730 Text Coprocessor is a high performance VLSI solution for raster scan text and graphics displays. The 82730 works as a coprocessor and has processing capabilities specifically tailored to execute data manipulation and display tasks. It provides the designer the ability to functionally partition his system thereby offloading the system CPU and achieving maximum performance through concurrent processing. The 82730 supports the generation of high quality text displays through features like proportional spacing, simultaneous superscript/subscript, dynamically reloadable fonts and user programmable field and character attributes. It supports high quality graphics with fast manipulation and display of bit map strings. An intelligent system interface and efficient software capabilities makes 82730 based systems easy to design.

82730 TEXT COPROCESSOR

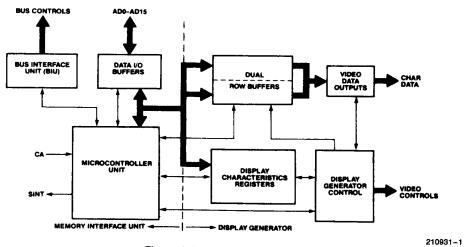

Figure 1. 82730 Block Diagram

# int<sub>e</sub>ľ

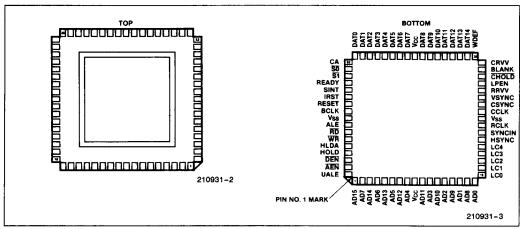

#### Figure 2. 82730 Pinout Diagram

Table 1. 82730 Pin Description

| The 82730 is packaged in a 68 pin JEDEC Type A ceramic package | The 82730 i | s packaged in a ( | 68 pin JEDEC Ty | be A ceramic package. |

|----------------------------------------------------------------|-------------|-------------------|-----------------|-----------------------|

|----------------------------------------------------------------|-------------|-------------------|-----------------|-----------------------|

| Symbol   | Pin<br>Number | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

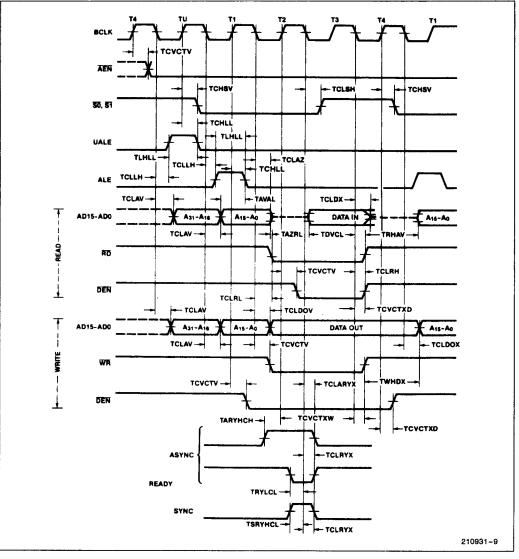

| AD15-AD0 | 1-8<br>10-17  | 1/0  | ADDRESS DATA BUS: these lines output the time multiplexed<br>address (TU, T1 states) and data (T2, T3, T4 and TW) bus. The bus is<br>active HIGH and floats to 3-state OFF when the 82730 is not driving<br>the bus (i.e., HOLD is not active or when HOLD is active but not<br>acknowledged, or when RESET is active).                                                                                                     |

| BCLK     | 59            | I    | BUS CLOCK: provides the basic timing for the Memory Interface Unit.                                                                                                                                                                                                                                                                                                                                                         |

| RD       | 62            | 0    | <b>READ STROBE:</b> indicates that the 82730 is performing a memory read cycle on the bus. RD is active low for T2, T3 and TW of any read cycle and is guaranteed to remain high in T2 until the address is removed from the bus. RD is active low and floats to 3-state OFF when 82730 is not driving the bus. RD will return high before entering the float state and will not glitch low when entering or leaving float. |

| WR       | 63            | 0    | WRITE STROBE: indicates that the data on the bus is to be written in a memory device. WR is active for T2, T3 and TW of any write cycle. It is active LOW and floats when 82730 is not driving the bus. WR will return high before entering the float state and will not glitch low when entering or leaving float.                                                                                                         |

| ALE      | 61            | 0    | LOWER ADDRESS LATCH ENABLE: provided by the 82730 to latch<br>the address into an external address latch such as 8282/8283 (active<br>HIGH). Addresses are guaranteed to be valid on the trailing edge of<br>ALE.                                                                                                                                                                                                           |

| UALE     | 68            | 0    | UPPER ADDRESS LATCH ENABLE: it is similar to ALE except that it occurs in upper address output cycle (TU).                                                                                                                                                                                                                                                                                                                  |

| AEN      | 67            | 0    | <b>ADDRESS ENABLE:</b> AEN is active LOW during the entire period when 82730 is driving the bus. It can be used to unfloat the outputs of the Upper and Lower Address latches.                                                                                                                                                                                                                                              |

| Table 1. 82730 Pin Description (Continued) |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|--------------------------------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                                     | Pin<br>Number  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| DEN                                        | 66             | Ο    | <b>DATA ENABLE:</b> provided as a data bus transceiver output enable for transceivers like the 8286/8287. DEN is active LOW during each bus cycle and floats when 82730 is not driving the bus. DEN will not glitch when entering or leaving the float state.                                                                                                                                                                                                                                                                                                                              |  |  |  |

| <u>50, 51</u>                              | 53, 54         | 0    | STATUS PINS: encoded to provide bus-transaction information:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                            |                |      | S1   S0     Bus Cycle Initiated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                            |                |      | 0       0       (Reserved)         0       1       Memory Read         1       0       Memory Write         1       1       Passive (No Bus Cycle)                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                            |                |      | These pins are directly compatible with iAPX 86, 186 status outputs S1 and S0. The status pins are floated when 82730 is not driving the bus. They will not glitch when entering or leaving the 3-state condition.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| READY                                      | 55             | I    | <b>READY:</b> signal to inform the 82730 that the data transfer can be completed. Immediately after RESET, READY is asynchronous (internally synchronized) but can be programmed during initialization to bus synchronous.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

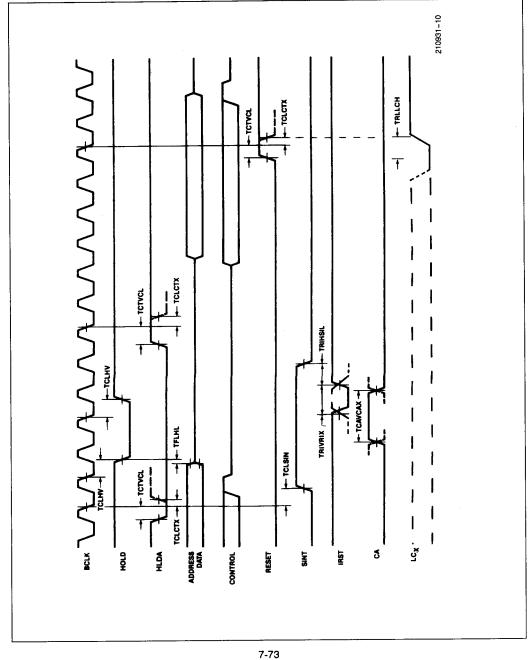

| HOLD                                       | 65             | 0    | HOLD: indicates that the 82730 wants bus access. HOLD stays active HIGH during the entire period when 82730 is driving the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| HLDA                                       | 64             | I    | HOLD ACKNOWLEDGE: indicates to 82730 that it is granted the bus<br>access as requested. HLDA may be asynchronous to 82730 clock. If<br>HLDA goes inactive (LOW) in the middle of an 82730 bus cycle, the<br>82730 will complete the current bus cycle first, then it will drop HOLD<br>and float address and bus control outputs.                                                                                                                                                                                                                                                          |  |  |  |

| CA                                         | 52             | I    | <b>CHANNEL ATTENTION:</b> used to notify 82730 that a command in the command block is waiting to be processed. CA is latched on its falling edge.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| SINT                                       | 56             | 0    | STATUS INTERRUPT: used to inform the processor that an unmasked<br>interrupt has been generated in the 82730 status register.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| IRST                                       | 57             | 1    | INTERRUPT RESET: SINT is cleared by activating the IRST pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RESET                                      | 58             | I    | <b>RESET:</b> causes 82730 to immediately terminate its present activity and enter a dormant state. The signal must be active HIGH for at least 4 BCLK cycles and is internally synchronized to the bus clock.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

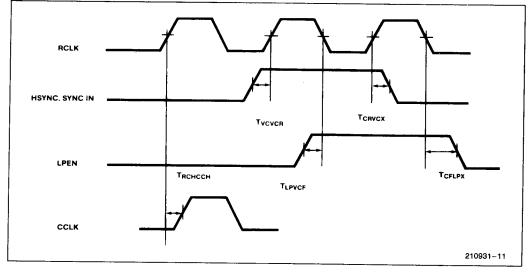

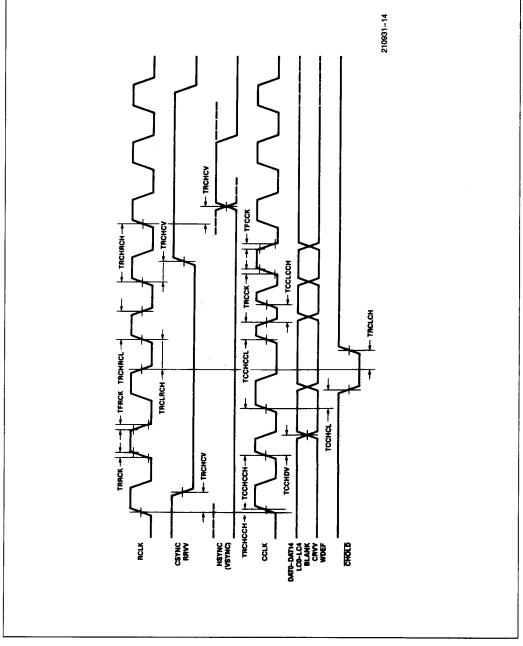

| CCLK                                       | 27             | l    | CHARACTER CLOCK: input used to clock row buffer data, attribute,<br>cursor and line count out of 82730. When more than one 82730 is<br>connected in cluster mode, CCLK is used to synchronize output from<br>both master and slave chips. A character data word will be output at<br>every rising edge of CCLK.                                                                                                                                                                                                                                                                            |  |  |  |

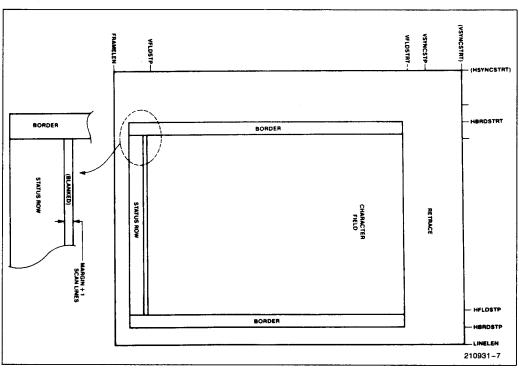

| RCLK                                       | 25             | I    | <b>REFERENCE CLOCK:</b> input used to generate timings for the screen layout and to define screen columns for data formatting. All raster output signals are specified relative to the rising edge of RCLK.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DAT0-DAT14                                 | 36-42<br>44-51 | 0    | VIDEO DATA BUS OUTPUT: the least significant 15 bits of the character data words are passed through the 82730 row buffer and made available on the pins DATO-DAT14. The user has the flexibility to partition the data word into character and attribute bits per his requirements. The bits that are assigned for internally generated attributes may also be available at pin DATO-DAT14. New character data will be shifted to these output pins at every rising edge of the CCLK. Together with LCO-LC4, they may be used to address the character generator or as attribute controls. |  |  |  |

| Table 1. 82730 Pin Description (Continued) |

|--------------------------------------------|

|--------------------------------------------|

7-36

This Material Copyrighted By Its Respective Manufacturer

| Symbol          | Pin<br>Number | Туре                    | Name and Function                                                                                                                                                                                                                                                                                                                                       |

|-----------------|---------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDEF            | 35            | 0                       | WIDTH DEFEAT: is used to indicate when the character is allowed<br>to be a variable width or must be of fixed width. WDEF is LOW if the<br>character being output is normal, but is HIGH if it is a superscript/<br>subscript character or visible attribute (TAB or GPA). Optionally,<br>WDEF can be held high by user command.                        |

| LC0-LC4         | 18–22         | 0                       | LINE COUNT OUTPUTS: used to address the character generator<br>for the line positions in a row. The line number output is a function<br>of the display mode and character attributes programmed by the<br>user.                                                                                                                                         |

| CSYNC           | 28            | 0                       | CCLK SYNCHRONIZATION OUTPUT: used to synchronize<br>external character clock generator to reference clock timing. This<br>output is active (high) outside the display field.                                                                                                                                                                            |

| CHOLD           | 32            | 0                       | CCLK INHIBIT OUTPUT: used by external logic to inhibit CCLK generation. This output is active (low) during the tab and end-of-row function.                                                                                                                                                                                                             |

| SYNCIN          | 24            | t                       | SYNCHRONIZATION INPUT: used to synchronize the vertical timing counters to an externally generated VSYNC signal. Used by slave mode 82730 to synchronize to a master mode 82730 and by the master 82730 to lock the frame to an external source such as the power line frequency.                                                                       |

| HSYNC           | 23            | O (MASTER)<br>I (SLAVE) | HORIZONTAL SYNC: in master mode, it is used to generate the CRT monitor's horizontal sync signal. It is active HIGH during the programmed horizontal sync interval. In interlace slave mode it is used in conjunction with SYNCIN to indicate the start of the even field for timing counter reset. At RESET, pin is set as an output in the LOW state. |

| VSYNC           | 29            | 0                       | VERTICAL SYNC: active HIGH during the programmed vertical<br>sync interval and used to generate the CRT monitor's vertical sync<br>signal.                                                                                                                                                                                                              |

| BLANK           | 33            | 0                       | BLANKING OUTPUT: used to suppress the video signal to the CRT. BLANK is clocked by CCLK.                                                                                                                                                                                                                                                                |

| CRVV            | 34            | 0                       | CHARACTER REVERSE VIDEO (CCLK OUTPUT): used to<br>externally invert video data output. CRVV is clocked by CCLK.                                                                                                                                                                                                                                         |

| RRVV            | 30            | 0                       | <b>REFERENCE REVERSE VIDEO (RCLK OUTPUT):</b> to externally<br>invert video in the field and border area if so programmed by user. It<br>is LOW outside the border area, RRVV is clocked by RCLK.                                                                                                                                                       |

| LPEN            | 31            | 4                       | LIGHT PEN INPUT: used to latch the position of a light pen. At the rising edge of this input, the column position and the row position of the 82730 will be loaded into the LPENROW and LPENCOL locations in the Command block.                                                                                                                         |

| V <sub>CC</sub> | 9, 43         |                         | POWER: + 5V nominal potential.                                                                                                                                                                                                                                                                                                                          |

| V <sub>SS</sub> | 26, 60        |                         | POWER: ground potential.                                                                                                                                                                                                                                                                                                                                |

#### Table 1: 82730 Pin Description (Continued)

7-37

Inte

Figure 1 shows a basic block diagram of the 82730 Text Coprocessor. The chip is divided into two main sections, the Memory Interface Unit and the Display Generator. The Memory Interface Unit controls fetching of the data and commands and handles interrupts and status. The Display Generator takes the data fetched by the Memory Interface Unit and presents it to the Video Interface logic which in turn drives the CRT monitor.

# **Memory Interface Unit**

The Memory Interface Unit is divided into two sections: The Bus Interface Unit and the Microcontroller Unit. The Bus Interface Unit does the acutal interfacing to the memory bus. It fetches or writes data under the control of the Microcontroller Unit. The Microcontroller Unit is a microprogrammed controller which is designed to efficiently fetch data from memory (up to 4 Mbytes/sec), and decode and execute various control and data handling commands. The Bus Interface Unit may be configured for 8 or 16 bit bus operation. With 8 bit bus selection, the user may specify either 8 or 16 bit character data. It also handles address manipulation automatically after being loaded from the Microcontroller Unit.

# **Display Generator**

The Display Generator takes the data fetched from memory plus the modes programmed into it at initialization and produces all the video timing and the data transfers to support the CRT monitor at the character level. The 82730 works with an external character generator and the 82731 Video Interface Controller. The data is passed to the Display Generator from the Memory Interface Unit through the dual row buffers (similar in operation to the one in the 8275 CRT controller). The row buffers allow the user to use cheaper and slower main memory for display needs, provide on-chip attribute and display function generation, and avoid the conflict of access to the display memory (that would otherwise take place) by using an ordinary DMA access mechanism.

# SYSTEM BUS INTERFACE

The Memory Interface Unit provides communication with system processor as well as memory interactions. Communication between the processor and the 82730 is performed via messages placed in communication blocks in shared memory. The processor can issue commands by preparing message blocks and directing the 82730's attention to them by asserting a hardware channel attention. The 82730 can cause interrupts on certain conditions, if enabled by the processor by activating its System Interrupt output, with status and error reporting taking place through the communication block in memory.

# **BUS INTERFACE UNIT**

The 82730 Bus Interface Unit provides an 8086 compatible bus interface which consists of:

- a 16/32 bit multiplexed Address/Data Bus: AD<sub>0</sub>-AD<sub>15</sub>

- A complete set of local bus control signals compatible with 8086 min mode: RD, WR, ALE, DEN, and READY

- Two status signals S0 and S1, compatible with 8086 max mode so that a bus controller (8288) can be shared for Multibus<sup>®</sup> access.

- Local bus arbitration through HOLD/HLDA

- Two upper Address Latch controls: UALE and AEN

The BUS INTERFACE UNIT (BIU) utilizes the same Bus structure as the 80186 or basically the same bus structure as the 8086 in both Min. and Max. mode, (with the exception of RQ/GT) and it performs a bus cycle only on demand (e.g., to fetch a command from the command block, or fetch a character from display data memory). The same set of Tstates (T1, T2, T3, T4 and TW) of 8086 are used to handle the time multiplexed address/data bus. However, adaptations are made to handle 32 bit addresses as explained in the following sections where specific details of the BIU operation are described. Those details not mentioned can be assumed to be the same as those of the 80186.

# ADDRESS BUS

The 82730 can be programmed during initialization to operate on either 16 bit or 32 bit (including any length between 17 and 32) physical addresses. Note that the 82730 does not use memory segmentation. The programmer must calculate physical addresses from segment and offset values to manipulate data structures.

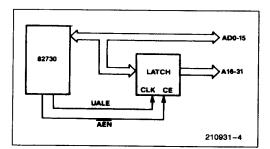

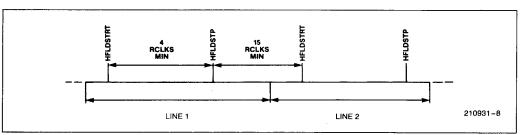

To support 32 bit physical addresses with a 16 bit physical bus, multiplexing is again used. An upper address output cycle, TU, is inserted between T4 and T1 to output the upper 16 bits of address. The upper address latch enable, UALE, is used to latch the upper addresses during TU. Figure 3 shows the configuration of a 32 bit address bus. TU occurs only when the 32 bit mode is specified and the upper address register of BIU is reloaded by MCU. This may result from:

- i) Initialization

- ii) Manipulation of display data or command pointers, for example, when a new string pointer is loaded during the execution of the END OF STRING command.

- iii) DMA address incrementing across a 64K byte segment boundary.

- iv) Regaining the bus after losing it to a higher priority master.

Timing of UALE is identical to that of ALE.  $\overline{\text{AEN}}$  is equivalent to the active period of 82730 driving the bus.

If 16 bit address mode is programmed, TU will never occur in any bus cycle since the MIU treats all display pointers as 16 bit quantities and loading of internal upper address register is bypassed during address calculation. UALE always stays inactive, but AEN still goes active to indicate the 82730 has control of the bus.

#### DATA BUS

The 82730 is capable of operating on either an 8 bit or a 16 bit Data bus, as programmed during initialization on the SYSBUS byte.

When an 8 bit data bus is specified, the address present on AD15 to AD8 Address/Data lines is maintained for the complete bus cycle. Therefore, compatibility with 80188, 8088, 8089 and 8085 multiplexed address peripherals is maintained. Since the internal processing of the 82730 generally operates on 16 bit data quantities, two Bus fetch cycles are performed for each 16 bit data item. The first cycle fetches the low order byte, the second cycle the high order byte. These 2 fetch cycles are always executed back to back. If HLDA drops during the first cycles, the 82730 will not respond until the second cycle is completed. An 8 bit data mode can be selected in an 8 bit bus system that requires only 8 bit character data be fetched.

In 16 bit bus system, the 82730 requires all 16 bit quantities to start on even address boundary. Word transfer to or from odd boundary is not allowed since this type of transfer not only doubles the use of bus bandwidth but also can be easily avoided in application software. All that is required is to make sure all address pointers be an even number (A0 = 0).

Figure 3. Address Extension up to 32 Bits

# **BUS CONTROLS**

The 82730 BIU provides both the 8086 MIN. Mode (Local Bus Control) and MAX. mode bus control signals simultaneously in any bus cycle. By providing a complete set of Local Bus control signals, the component count of the Local processing module is minimized.

Because only two types of Bus operations, Memory Read and Memory Write, are executed in the 82730 BIU, the 8086's S2 status signal is omitted from the Max. mode controls. S2 could be set to "1" during any 82730 Bus cycle. AEN can be used to produce S2 since it stays active whenever 82730 is driving the bus. The status signals become valid at the middle of the cycle before T1 which could be either T4 or TU.

BHE is not provided on the 82730 because, the 82730 only writes words to even address boundaries and bytes to the upper byte position. For these writes BHE is always high. A pullup resistor or a three-state buffer controlled by AEN, can provide this signal.

DT/R is also not provided on the 82730 because its function can be replaced with  $\overline{S1}$ , latched by ALE.

After RESET is applied, READY is set to be an asynchronous input. An on-board synchronization circuit provides reliable operation for any type of system. During initialization, READY may be programmed to be bus synchronous. For those systems that can meet the set-up time specifications, this mode provides more efficient bus utilization.

# LOCAL BUS ARBITRATION

The 82730 BIU is designed to function as a bus master in a multimaster Local bus environment using the HOLD/HLDA protocol for Bus arbitration.

7-39

int<sub>e</sub>r

In the Self Contained Arbitration scheme, one processor and one 82730 share access to the local bus. The 82730 raises its HOLD request whenever it needs bus access. After HLDA is granted from the processor, the 82730 will not start driving the bus until 2 clock cycles later. This latency allows sufficient time for the 8086 or 80186 processor to get off the bus. When 82730 completes it bus accesses, it will first float its output drivers before dropping the hold request.

In a Local bus configuration with three or more bus masters, a higher priority DMA Peripheral device can preempt the HLDA from a 82730 which is the current bus master. The 82730 will complete its current bus cycle, then float its output drivers and drop the HOLD request. However, the 82730 may raise the HOLD request again 2 clock cycles later if it still needs the bus to complete the interrupted burst DMA activities.

### DMA BURST AND SPACE

Some system configurations using the 82730 would be adversely affected by the long burst data transfers which the Memory Interface Unit (MIU) may occasionally desire. Since the 82730 will normally be configured as one of the higher priority bus masters, burst lengths must be limited for these systems. For this reason, the length of a burst transfer and the number of memory cycles between burst transfers are both programmable via the mode registers:

|      | 15 | 14    | 8  | 7 | 6 | 0      |

|------|----|-------|----|---|---|--------|

| MPTR |    | BRSTL | EN | _ | В | RSTPAC |

BRSTLEN—Burst Length. Determines the number of contiguous word-fetch cycles which may be requested. Programmable from 1 to 127. Note that in an 8 bit bus, 16 bit data system, the burst counter only increments once for the 2 bus cycles required to complete a word fetch. (Note: burst length = 0 is not defined and should not be programmed with a non-zero burst space.)

BRSTSPAC—Burst Space. Determines a minimum number of bus clocks to occur between burst accesses. Programmable from 0-511 in increments of four. Zero space selects an infinite burst length.

A DMA burst could be terminated before the programmed burst length is reached in the following circumstances:

- i) The MIU does not need any more bus accesses, for example, when the row buffer if filled.

- ii) A datastream command is encountered and the MIU must execute the command first before it resumes data accessing.

iii) The bus is taken away by a higher priority device in multi-master bus configuration.

In these cases, the burst counter is cleared. The BIU must complete a full burst before it waits through the SPACE cycles. DMA Burst/Space will be set to zero space until the completion of the first MODESET command.

# INITIALIZATION OF BIU

Upon activation of the RESET input, the 82730 BIU will stop all operations in progress and deactivate all outputs. It will stay in this quiescent state until memory access is requested by the MCU after MCU receives its first channel attention after RESET. The following table shows the state of all MIU outputs during and after reset.

Table 2. 82730 Bus During and After Reset

| Signals       | Condition                      |

|---------------|--------------------------------|

| AD15-0        | Three-state                    |

| RD, WR, DEN   | Driven to '1' then three-state |

| <u>50, 51</u> | Driven to '1' then three-state |

| ALE, UALE     | Low                            |

| AEN           | High                           |

| HOLD          | Low                            |

| SINT          | Low                            |

# 82730 COMPATIBILITY ISSUES

# 82730 Bus Clock Compatibility

The 82730 uses the 50% duty cycle output of the iAPX-186 at 8 MHz or that generated by a clock generator such as the 82285. A different duty cycle clock may be used at lower frequencies, so the 82730 is also usable with the iAPX-86, 88 family.

# 82730 Bus Interface Compatibility

The bus interface compatibility between the 82730 and another bus master has four main issues: data bus width, addressability, control bus structure and local bus mastership arbitration.

#### Data Bus

Data Bus width compatibility with all 85/86 family processors (8085, 8086, 8088, 80188, 80186, and 80286) is being supported by the 8/16 data bit pro-

grammability already discussed. This allows interfacing to the above processors either directly or through a Multibus-like interface.

#### **Address Bus**

The 82730 uses real 32-bit addresses. The user's software must calculate real addresses; this general addressing scheme allows the 82730 to be used with any microprocessor.

# **Control Bus**

The 82730 implements both 8086 minimum and maximum mode bus control structures. This was done to maximize compatibility with the 80186 which has the same structure. This allows the 82730 to be run locally (minimum mode) with a 8085, 8086, 8088, 80188, or 80186. The 80186/188 and 82730 can run together at 8 MHz because of clock duty cycle considerations. The 82730 can only communicate to an 80286 via a system bus (such as MULTIBUS), bus interface, or dual-port RAM.

# INITIALIZATION SEQUENCE

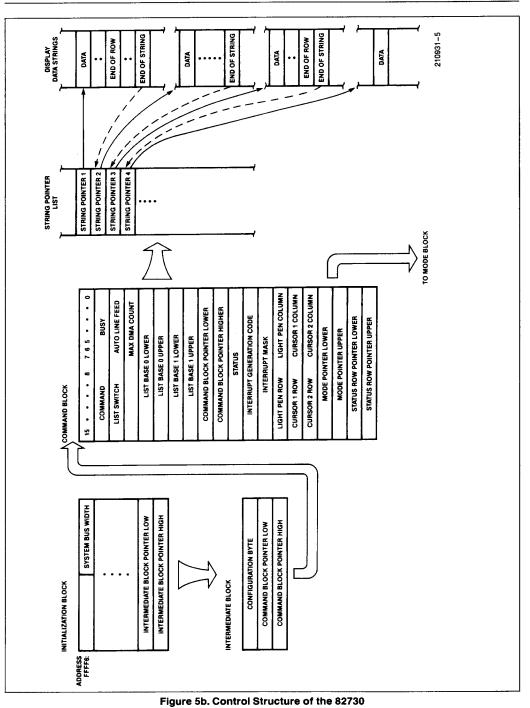

The first CA (Channel Attention) after Reset causes an Initialization Sequence to be executed. The system processor must set up the appropriate initialization information in memory and set the BUSY flag in the Intermediate Block to a non-zero value prior to issuing this CA.

Initially, 32-bit addressing and 8-bit bus width are assumed until the corresponding information is fetched during the initialization. First the SYSBUS byte is fetched from memory location FFFF FFF6. (When the address bus is less than 32 bits wide, the higher order bits are unused.) The format for SYSBUS byte is shown in Figure 4 and is the same as that used for 8089. The data bus width is specified by the least significant bit w, with w = 0 indicating an 8-bit bus and w = 1 signifying a 16-bit bus.

A 32-bit real address pointer is then fetched from memory locations FFFF FFFC through FFFF FFFF, with lower bytes of the pointer residing in lower addresses. This pointer is used as an Intermediate Block Pointer (IBP).

The Intermediate Block Pointer (IPB) is incremented by two and is used to locate the Command Block Pointer (CBP). Four bytes are fetched irrespective of whether a 16-bit or 32-bit addressing option is used. The System Configuration byte (SCB) is then fetched from location (IBP + 6).

The least significant, (U of the SCB) specifies 16 or 32-bit addressing option, with U = 0 indicating 16 bit addressing and U = 1 specifying 32-bit addressing. The SCB also contains information about cluster operation. Since up to four 82730's can be connected in a cluster with their respective data interleaved in memory, cluster information is needed for the data access task. The SCB specifies Cluster Number (CL NO), which is the number of 82730's connected in a cluster and Cluster Position (CL POS) which is the position of this particular 82730 within the cluster. CL NO = 0, 1, 2 or 3 indicates a cluster containing 1, 2, 3 or 4 82730's respectively. Simlarly, CL POS = 0, 1, 2 or 3 indicates 1st, 2nd, 3rd or 4th position respectively. Each 82730 adds an offset equal to 2 \* CLPOS to the SPTR fetched from memory and increments the pointer by 2 \* (CL NO + 1). The programming of CL NO and CL POS is independent. No checking is done for CL POS greater than CL NO on the 82730. Note that at least one 82730, in a cluster (even if it is a cluster of one), must be assigned as cluster position zero (CL POS = 0) for Virtual Display mode to work properly.

intel

| 7    |        |            |           |       |            |       | 0                  |             |  |

|------|--------|------------|-----------|-------|------------|-------|--------------------|-------------|--|

| 0    | 0      | 0          | 0         | 0     | 0          | 0     | W                  | SYSBUS Byte |  |

|      |        |            | w         | _     | Data Bus V | Vidth |                    |             |  |

|      |        |            | 0         |       | 8-Bit      |       | _                  |             |  |

|      |        |            | 1         |       | 16-Bit     |       |                    |             |  |

| 7    | 6      | 5          | 4         | 3     | 2          | 1     | 0                  |             |  |

| SRDY | DTW16  | M/S        | CL        | POS   | CL         | NO    | U                  | SCB Byte    |  |

|      | SRDY   | READY MODE |           |       | DTW16      | 0     | Display Data Mode  |             |  |

| -    | 0      | A          | synchron  | nous  | 0          |       | 8-bit data         |             |  |

|      | 1      |            | Synchron  |       | 1          |       | 16-bit d           | ata         |  |

|      | M/S    | Mode       |           |       | CL POS     |       | Position<br>Cluste |             |  |

| -    | 0      |            | Slave     |       | 00         |       | 1st                |             |  |

|      | 1      |            | Master    | r     | 01         |       | 2nd                |             |  |

|      |        |            |           |       | 10         |       | 3rd                |             |  |

|      |        |            |           |       | 11         |       | 4th                |             |  |

|      |        | N          | o. of 827 | '30's |            |       |                    |             |  |

| _    | CL NO. |            | In Clust  | er    | U          |       | ADDR BUS           | WIDTH       |  |

|      | 00     |            | 1         |       | 0          |       | 16-bi              |             |  |

|      | 01     |            | 2         |       | 1          |       | 32-bi              | t           |  |

|      | 10     |            | 3         |       |            |       |                    |             |  |

|      | 11     |            | 4         |       |            |       |                    |             |  |

Figure 4. SYSBUS and SCB Encoding

The SCB also contains an  $M/\overline{S}$  bit which specifies a master or slave mode. The  $M/\overline{S}$  bit is stored internally for use by the Display Generator (DG).  $M/\overline{S} = 1$  indicates a master mode and  $M/\overline{S} = 0$  specifies a slave mode. The format for the System Configuration Byte (SCB) is shown in Figure 4. Following these actions, the BUSY flag in the Intermediate Block at address IBP is cleared and a normal Channel Attention sequence is then executed.

The last two bits in the SCB are DTW16 and SRDY. DTW16 specifies whether the display data in 8 bit bus mode (W = 0) is 8 or 16 bit. If a 16 bit system is specified (W = 1) then DTW16 is ignored and forced internally to a "one". SRDY specifies whether the clock synchronization circuit for the READY pin is internal (SRDY = 0) or external (SRDY = 1).

The Initialization Control Blocks in memory are illustrated in Figure 5a. How these fit into the control structure of the 82730 is shown in Figure 5b.

#### **Channel Attention Sequence**

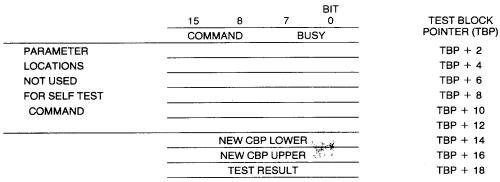

When the processor activates CA, an internal latch in 82730 is set on the falling edge of CA input and this latch is sampled by the MCU. The first CA activation after reset causes the 82730 to execute an initialization sequence. Any subsequent activation will cause the MCU to start processing the command block by fetching a channel command.

If a display is in progress, the MCU will sample CA at each end of frame, otherwise it will sample CA every cycle until it is found active. When CA is found active, the MCU will fetch the command byte from "COMMAND" location in the command block, execute the command and clear the BUSY flag upon completion. The internal CA latch is also cleared by the MCU. An invalid command code has the effect of NOP and the BUSY flag is cleared. It will also cause the Reserved Channel Command (RCC) status bit to be set. intel

|                  | 15 | 8           | 7      | 0 |           |

|------------------|----|-------------|--------|---|-----------|

| INTERMEDIATE     |    | IBP UPPE    | R      |   | FFFF FFFE |

| BLOCK POINTER    |    | IBP LOWE    | R      |   | FFFF FFFC |

|                  |    |             |        |   |           |

|                  |    | (RESERVED S | YSBUS) |   | FFFF FFF6 |

|                  |    | (RESERVED)  | SCB)   |   | IBP + 6   |

| INTERMEDIATE     |    | CBP UPPE    |        |   | IBP + 4   |

| BLOCK            |    | CBP LOW     | ER     |   | IBP + 2   |

|                  |    | (RESERVED)  | BUSY   |   | IBP       |

| COMMAND<br>BLOCK |    |             |        | * |           |

|                  |    | COMMAND E   | BUSY   |   | CBP       |

|                  | L  | OW SYSTEM M | EMORY  |   |           |

7-43

7-44

intel

PRELIMINARY

# 82730 TEST FEATURES

The 82730 has built in Self-Test features that provide testability at the component or at the board level. These features include the test commands and the output pin force capability and are described below.

# **Output Pin Force Capability**

A capability to force logic state (high, low, high impedance) on all output pins is provided in the 82730 Text Co-Processor. This is accomplished by providing a stimulus on pins LCO-LC2 during chip reset. This feature is used for dc parametric tests on the output pins.

The state of pins LCO-LC2 is monitored during chip reset. The state of these pins is latched internally on the falling edge of chip reset. If no external inputs are applied during reset, the state observed will be all 1's and no action will be taken by the 82730. If any external inputs are applied to pins LCO-2 during reset, the resulting action will depend upon the state latched on the falling edge of reset. The 82730 maintains pins LCO-LC2 in high impedance state for the duration of chip reset to avoid contention with external inputs. Also internal pull-ups ensure that a state of all 1's will be detected if no external inputs are applied.

The actions corresponding to each of the observed states of pins LC0-LC2 are summarized in Figure 6a.

# Stand-Alone "Self Test"

The built-in Self Test capability of the 82730 can be invoked in a stand-alone mode by applying an external stimulus through pins LC0–LC2 during chip reset. This is the same mechanism as the one used for forcing logic states on output pins. Figure 6a.

If pin LC2 is pulled low during chip reset, the 82730 executes a built-in self test. Upon completion of the self-test, a 16-bit signature, generated internally as the test result, is output via pins WDEF, DAT14-DAT0. The completion is signalled by providing a logic "O" output on pin LC3 as a completion flag. The signature will remain on the output pins until the next chip reset. The 82730 will enter an idle state awaiting chip reset and will not respond to any external inputs until a reset signal is applied. During the process of presenting the signature onto WDEF, DAT14-DATO, the signature will also appear briefly on the AD bus in the form of a bus cycle with two 8bit accesses to addresses, AAAAH, AAABH. However, this phenomenon is only incidental. Pins WDEF, DAT14-DATO should be used for observing the signature.

The stand-alone self test includes the testing of internal address pointer registers. These registers are not tested when the self test is invoked by issuing a "Self Test" command. (See under Channel Commands below). Therefore, the signature generated during stand-alone self test will be different from that generated by the "Self Test" command.

| State of Pins LC0-LC2<br>During Chip Reset |             |                | Action                                    |

|--------------------------------------------|-------------|----------------|-------------------------------------------|

| LC2                                        | LC1         | LC0            |                                           |

| 0                                          | х           | х              | Invoke Stand-Alone Self Test              |

| 1                                          | 0           | 0              | Force all Outputs to High Impedance State |

| 1                                          | 0           | 1              | Force all Outputs to Logic High State     |

| 1                                          | 1           | 0              | Force all Outputs to Logic Low State      |

| 1                                          | 1           | 1              | NOP                                       |

| Figu                                       | IFO FO OUNT | the Dim Enviro |                                           |

Figure 6a. Output Pin Forcing and Stand-Alone Self Test Invocation

# 82730 CHANNEL COMMANDS

#### **Table 3. Channel Commands**

| Command            | OP CODE              |

|--------------------|----------------------|

| 1 START DISPLAY    | 0000 0001 01 H       |

| 2 START VIRTUAL    | 0000 0010 02 H       |

| DISPLAY            |                      |

| 3 STOP DISPLAY     | 0000 0011 03 H       |

| 4 MODE SET         | 0000 0100 04 H       |

| 5 LOAD CBP         | 0000 0101 05 H       |

| 6 LOAD INTMASK     | 0000 0110 06 H       |

| 7 LPEN ENABLE      | 0000 0111 07 H       |

| 8 READ STATUS      | 0000 1000 08 H       |

| 9 LD CUR POS       | 0000 1001 09 H       |

| 10 SELF TEST       | 0000 1010 0A H       |

| 11 TEST ROW BUFFEF | 0000 1011 0B H       |

| 12 NOP             | 0000 0000 00 H       |

| 13 (RESERVED)      | From: 0000 1100 0C H |

|                    | To: 1111 1111 FF H   |

The system processor issues channel commands to 82730 via the Command Block. The processor first checks if the BUSY flag in the command block has been cleared. It should wait for the BUSY flag to be cleared before proceeding with the issuing of a command. When the BUSY flag is cleared, the processor places a command byte in the "COMMAND" location in command block, sets the BUSY flag to a nonzero value and asserts Channel Attention (CA), by activating the CA input to 82730. A Channel Attention should not be issued, if the BUSY flag has not been cleared.

#### START DISPLAY

| 0000 | 0001 | CMD Byte |

|------|------|----------|

|      |      |          |

LISTSWITCH, Auto Linefeed, Max DMA Count and Cursor Position values are fetched from the Command Block and stored internally after this command is received. The BUSY flag is cleared and the normal display process is activated.

The MCU fetches strings of data from the memory, using the parameters LISTSWITCH, LBASE0 and LBASE1. The data fetched is interpreted as datastream commands or character data to be displayed by the Display Generator. The MCU loads the data into one of the two Row Buffers in the CRT controller, while the Display Generator displays the data from the other buffer, the buffers being swapped at the end of the row. Any datastream commands encountered during data fetch are immediately executed. The display process is continued until it is deactivated by a STOP DISPLAY command or a Reset. Other channel commands can be issued while a display is in progress and they will be executed when CA is found active at one of the periodic samplings at each end of frame.

The DIP (Display in Progress) status bit is set and the VDIP (Virtual Display in Progress) is cleared upon receiving a START DISPLAY command. Both bits are reset upon receiving a STOP DISPLAY command or a Reset.

It is necessary to load in proper mode information through a MODESET command before activating the display. Following Reset, START DISPLAY command will not be executed, i.e., will result in a NOP until a MODESET command has been issued.

#### START VIRTUAL DISPLAY

| 0000 | 0010 | CMD Byte |

|------|------|----------|

|      |      |          |

LISTSWITCH, Auto Linefeed, Max DMA Count and Cursor Positions are fetched from the Command Block and stored internally upon receiving this command. The BUSY flag is cleared and the Virtual Screen display process is activated.

The operation of Virtual Screen display process is similar to that of a regular display process, except for following a different data access mechanism. The parameters LISTSWITCH, LBASE0 and LBASE1 in the command block represent ACCESS SWITCH, ACCESS BASE0 and ACCESS BASE1 respectively, in virtual screen display.

The VDIP (Virtual Display in Progress) status bit is set and the DIP status bit is cleared upon receiving a START VIRTUAL DISP command: Both DIP and VDIP are reset upon receiving a STOP DISPLAY command or a Reset.

START VIRTUAL DISPLAY command will not activate a display and results in a NOP until a MODE-SET command is issued after a Reset.

#### STOP DISPLAY

| 0000 | 0011 | CMD Byte |

|------|------|----------|

|------|------|----------|

The display process is deactivated upon receiving this command. The DIP and VDIP status bit are reset and the BUSY flag is cleared.

This command blanks the display. HSYNC and VSYNC are **not** affected.

7-46

# MODESET

| 0000 | 0100 | CMD Byte |

|------|------|----------|

|      |      |          |

The Mode Pointer contained in command block location (CBP + 30) is used to access the Mode Block and the modes are fetched sequentially and loaded into the corresponding internal registers in 82730. LISTSWITCH, Auto Linefeed, Max DMA Count and Cursor Positions are fetched from the Command Block and stored internally upon completion and the BUSY flag is cleared.

The organization of mode words in the mode block and the parameters supplied by them are shown below (See Figure 10). Some of these parameters which are critical to the operation of a text coprocessor are required to remain unchanged over most of normal operation. No provision is made to prevent MODESET from changing these parameters and it is left to the designer to insure that they are not changed.

The modes provide horizontal and vertical mode display parameters, interlace information, DMA burst and spacing specifications, cursor characteristics as well as attribute enables and bit-selects. Typically, this would be the first command issued after initialization. The Mode Block provides all the parameters needed for a complete initialization of the 82730 for display. Thus a single Modeset command can fully initialize the chip. Note that until the first Modeset command is sent, certain functions such as VSYNC and HSYNC are not enabled.

It is necessary to set up proper mode information, before activating a display. Therefore, a display activating command should not be issued unless proper mode information has been loaded through a MODESET command. START DISPLAY and START VIRTUAL DISPLAY commands will result in a NOP if a MODESET command has not been issued since the most recent Reset.

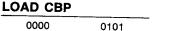

CMD Byte

The address pointer "NEW CBP" contained in the command block is fetched and stored in the CBP register in the text coprocessor, replacing the old CBP. This effectively moves the command block in the memory. The Command byte from the new Command Block is fetched and the specified channel command is executed. The BUSY flag in the new Command Block is cleared upon completion.

# LOAD INTMASK

| 0000 | 0110 |

|------|------|

|      | 0110 |

CMD Byte

The interrupt mask contained in location "INT-MASK" in the command block is fetched and stored internally in the CRT controller. When a particular mask bit is set, the interrupt is disabled for a status bit in the corresponding bit position. An interrupt is generated by the text coprocessor by activating the SINT pin, if a status bit is 1 and the corresponding bit in the interrupt mask is 0. The BUSY flag is cleared upon completion.

Interrupts can be enabled for the following status bits.

| 7 | 6   | 5   | 4   | 3   | 2    | 1   | 0   | BIT    |

|---|-----|-----|-----|-----|------|-----|-----|--------|

| _ | RDC | RCC | FDE | EOF | DBOR | LPU | DUR | STATUS |

|   |     |     |     |     |      |     |     | WORD   |

RDC: Reserved Datastream Command Encountered

- RCC: Reserved Channel Command Executed

- FDE: Frame Data Error (Fetching characters past physical End of Frame)

- EOF: End of "n" frames (Logical end of nth frame)

- DBOR: Data Buffer Overrun (Row Buffer filled completely without encountering END OF ROW command)

- LPU: Light Pen Update

- DUR: Data Underrun (Buffer swap initiated before finishing Row Buf loading)

#### READ STATUS

| 1000 | CMD Byte |

|------|----------|

|      | 1000     |

The internal status register is written to "STATUS" location in the command block. The status register is then cleared, however DIP and VDIP status bits are not cleared. LISTSWITCH, AUTO LINEFEED, Max DMA Count and Cursor Positions are fetched from the Command Block and stored internally. The BUSY flag is then cleared.

#### STATUS WORD

| 15-9 | 8    | 7   | 6   | 5   | 4   | з   | 2    | 1   | 0   |

|------|------|-----|-----|-----|-----|-----|------|-----|-----|

|      | VDIP | DIP | RDC | RCC | FDE | EOF | DBOR | LPU | DUR |

0111

#### LPEN ENABLE

0000

CMD Byte

7-47

The Light Pen detection process is enabled to search for a rising edge on the LPEN pin. The BUSY flag is then cleared.

If the display process is active and a rising edge is detected on the LPEN input, the corresponding row and column position on the screen is stored internally. At the next end of frame, the LPEN position is written to locations "LPENROW" and "LPENCOL" in the command block and the LPU (Light Pen Update) status bit is set.

If the display process is not active, **Precommand** has no immediate effect. However, the **LPEN** detection process remains enabled and will take effect if a display is activated subsequently.

| LD | CU | R | Ρ | OS |

|----|----|---|---|----|

|----|----|---|---|----|

| 0000 | 1001 | CMD Byte |

|------|------|----------|

|      |      |          |

The display row and column positions of cursors 1 & 2 as set in locations "CUR1 ROW," "CUR1 COL," "CUR2 ROW" and "CUR2 COL" in the command block are loaded into internal registers in the CRT controller. Also LISTSWITCH Auto Linefeed and Max DMA Count are loaded from the Command Block and the BUSY flag is cleared. Ths command is used to change the cursors only. Note that the cursor positions are also updated with the execution of other channel commands.

The cursor characteristics for display are defined by the mode. During the display process, a cursor will be displayed accordingly at the position specified above.

# **TEST COMMANDS**

The test commands for the 82730 are issued in the same manner as the normal channel commands. However, the parameters used by test commands are different from those used by the channel commands in normal operation. Therefore, a Test Block which is similar in format to the Command Block is defined. Switching between Command Block and Test Block is accomplished using the "Load CBP" command. The Test Block differs only in the parameter locations associated with the command. The locations for New CPB, command Block and Test Block. The "Test Result" location in Test Block corresponds to the "Status" location in Command Block.

The test commands can be executed, following chip reset, only until the first Modeset command is issued. Once a Modeset command has been executed following chip reset, any subsequent test commands will not be executed and will result in a NOP.

#### "Self Test" Command

| 0000 | 0010 | CMD Byte |

|------|------|----------|

|      |      |          |

A built-in Self test is performed using an internal test pattern. The signature generated during the test is written to the Test Result location (TBP + 18) in the Test Block. The Busy Flag in the Test Block is then cleared. The Self Test command must be immediately preceded by a chip reset in order to ensure a consistent signature.

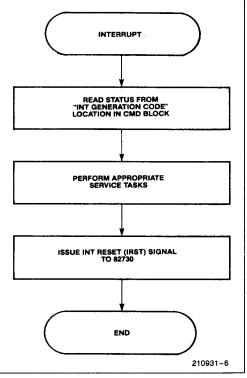

The Test Block format for issuing the Self Test command is shown in Figure 6b.

#### "Row Buffer Test" Command

| 0000 | 1011 | CMD Byte |

|------|------|----------|

|      |      |          |

The Load Pointer in Test Block is fetched. It points to the system memory area storing the test pattern to be used for testing the on-chip RAM (i.e. - the Row Buffers). The Store Pointer, which points to memory area where the data read back from the RAM will be written, is also fetched from Test Block.

Successive words are fetched from memory and written to the Row Buffer, until it is completely filled. Note that three extra words beyond the maximum. Row Buffer capacity will be fetched. If N = Max Row Buffer capacity, (N + 3) words will be fetched from memory. The extra words fetched will be ignored. The Row Buffer contents are then read back and are written to successive locations in memory area pointed to by the Store Pointer. The test is then repeated on the second Row Buffer. Note that the (N + 4)th word in the pattern stored in memory constitutes the first word written to the second Row Buffer. The data storage for the Row Buffer test patterns is illustrated in Figure 6c.

Internally, the Row buffers are 17-bits wide, while the data path is 16-bits wide. During the writing of data to Row Buffers, a complement of bit 15 is written to bit 16 of the Row Buffer in order to test all 17 bits. During the read back, two data words are stored in system memory for each location in the Row Buffer. The first word will consist of bits 0–15 read from the Row Buffer, while the second word will consist of bits 0–14 and bit 16 from the Row Buffer. Thus a total of 4\*N words will be stored back in system memory as a result of the Row Buffer Test (2\*N for each Row Buffer).

Figure 6b. Test Block Format for "Self Test" Command (For both 16-bit and 32-bit addressing modes)

A signature is generated during the test and is written to Test Result location in Test Block upon completion. The BUSY flag in the Test Block is then cleared. The Test Block format for issuing the Row Buffer Test command is illustrated in Figures 6d.1 and 6d.2. Note that the locations for Load Pointer and Store Pointer parameters are different for 16-bit and 32-bit addressing modes.

| LOAD POINTER |   | WORD 1      | •       | -                              |

|--------------|---|-------------|---------|--------------------------------|

|              | - | WORD 2      | •       |                                |

|              |   | WORD 3      | •       |                                |

|              |   | •           | n WORDS |                                |

|              |   | •           | •       | TEST PATTERN                   |

|              |   | •           | •       | FOR ROW BUFFER 1               |

|              |   | •           | •       |                                |

|              |   | •           | •       |                                |

|              |   | WORD n      | •       |                                |

|              |   |             |         |                                |

|              |   | WORD n+3    |         |                                |

|              |   | WORD n+4    | •       |                                |

|              |   | WORD n+5    | •       |                                |

|              |   | WORDHING    | •       |                                |

|              |   | •           | n WORDS |                                |

|              |   | •           | •       | TEST PATTERN                   |

| •            |   | •           | •       | FOR ROW BUFFER 2               |

|              |   | •           | •       |                                |

|              |   | •           | •       |                                |

|              |   | WORD 2n + 2 | •       |                                |

|              |   | WORD 2n+3   | •       |                                |

|              |   |             |         |                                |

|              |   | WORD 2n+6   |         | n = MAX ROW BUFFER<br>CAPACITY |

# PRELIMINARY

|            |                                |                               |      | віт    |               |  |  |  |

|------------|--------------------------------|-------------------------------|------|--------|---------------|--|--|--|

| 15         | 8                              | 7                             |      | 0      | TEST BLOCK    |  |  |  |

| COMMAI     | ND                             |                               | BUSY |        | POINTER (TBP) |  |  |  |

|            | (RESERV                        | ED)                           |      |        | TBP + 2       |  |  |  |

|            | LOAD POINTEF                   | LOWER                         |      |        | TBP + 4       |  |  |  |

|            | LOAD POINTER                   | RUPPER                        |      |        | TBP + 6       |  |  |  |

|            | STORE POINTE                   | R LOWER                       |      |        | TBP + 8       |  |  |  |

|            | STORE POINTER UPPER            |                               |      |        |               |  |  |  |

|            | (RESERVI                       | ED)                           |      |        | TBP + 12      |  |  |  |

|            | NEW CBP LC                     | OWER                          |      |        | TBP + 14      |  |  |  |

|            | NEW CBP U                      | PPER                          |      |        | TBP + 16      |  |  |  |

| <u>., </u> | TEST RESULT                    |                               |      |        |               |  |  |  |

| Fig        | ure 6d.1 Test Block F<br>(32-b | ormat for "I<br>bit addressin |      | Comman | ıd            |  |  |  |

|            |                                |                               |      | BIT    |               |  |  |  |

| 15         | 8                              | 7                             |      | 0      | TEST BLOCK    |  |  |  |

| 15      | 8                 | 1      |             | U | TEST BLOCK    |

|---------|-------------------|--------|-------------|---|---------------|

| COMMANI | 2                 |        | BUSY        |   | POINTER (TBP) |

|         | (RESERV           | /ED)   |             |   | TBP + 2       |

|         | (RESERV           | /ED)   |             |   | TBP + 4       |

|         | LOAD POI          | NTER   |             |   | TBP + 6       |

|         | (RESERV           | /ED)   |             |   | TBP + 8       |

|         | STORE PO          | INTER  |             |   | TBP + 10      |

|         | (RESERV           | /ED)   |             |   | TBP + 12      |

|         | NEW CBP L         | OWER   |             |   | TBP + 14      |

|         | NEW CBP UPPER     |        |             |   |               |

|         | TEST RES          | SULT . |             |   | TBP + 18      |

| Flour   | - Ed O Test Black |        | w Duffer To | - |               |

#### Figure 6d.2 Test Block Format for "Row Buffer Test" Command (16-bit addressing mode)

#### NOP

0000 0000 CMD Byte

LISTSWITCH, Auto Linefeed, Max DMA Count, and Cursor Positions are fetched from the command block and stored internally as in all other channel commands. The Busy flag is then cleared.

### 82730 DATASTREAM COMMANDS

#### **Datastream Commands**

Datastream commands are commands embedded in the data fetched from memory by the data access task. These commands are differentiated from character data by the command bit. The most significant bit (MSB) of each data word is designated as the command bit. If the command bit is "1", the lower 15 bits of the data word are interpreted as a datastream command, while if the command bit is "0" the lower 15 bits (or 7 bits if DTW16 = 0) are interpreted as character data.

# Datastream Command Operation

During the data access task, the Micro Controller Unit (MCU) examines the command bit of each data word fetched. If the command bit is 1, it executes the datastream command specified in the data word. Otherwise, it stores the lower 15 bits of the data word in the Row Buffer as character data. This process is repeated for each data word fetched.

# **Datastream Command List**

|    | Command                    |      | Command Code |                                       |          |         |  |

|----|----------------------------|------|--------------|---------------------------------------|----------|---------|--|

|    |                            | Ор   | Code         | Para                                  | neters   | OP Code |  |

| 1  | ENDROW                     | 1000 | 0000         | XXXX                                  | XXXX     | 80      |  |

| 2  | EOF                        | 1000 | 0001         | XXXX                                  | XXXX     | 81      |  |

| 3  | END OF STRING & END OF ROW | 1000 | 0010         | XXXX                                  | XXXX     | 82      |  |

| 4  | FULROWDESCRPT              | 1000 | 0011         |                                       | n''      | 83      |  |

| 5  | SL SCROLL STRT             | 1000 | 0100         | 1                                     |          | 84      |  |

| 6  | SL SCROLL END              | 1000 | 0101         |                                       |          | 85      |  |

| 7  | TAB TO n                   | 1000 | 0110         | , , , , , , , , , , , , , , , , , , , |          |         |  |

| 8  | LD MAX DMA COUNT           | 1000 | 0111         | COUNT                                 |          | 86      |  |

| 9  | ENDSTRG                    | 1000 | 1000         | XXXX                                  | XXXX     | 87      |  |

| 10 | SKIP n                     | 1000 | 1001         |                                       | n"       | 88      |  |

| 11 | REPEAT n                   | 1000 | 1010         |                                       | י<br>יי  | 89      |  |

| 12 | SUB SUP n                  | 1000 | 1010         |                                       | י<br>ז"  | 8A      |  |

| 13 | RPT SUB SUP n              | 1000 | 1100         |                                       | י<br>זיי | 8B      |  |

| 14 | SET GEN PUR ATTRIB         | 1000 | 1101         | GPA                                   |          | 8C      |  |

| 15 | SET FIELD ATTRIB           | 1000 | 1110         |                                       | -        | 8D      |  |

| 16 | INIT NEXT PROCESS          | 1000 | 1111         |                                       | XXXX     | 8E      |  |

|    | (Command process command)  | 1000 |              | XXXX                                  | XXXX     | 8F      |  |

| 17 | (RESERVED)                 | 10XX | ~~~~         |                                       |          |         |  |

| 18 | NOP                        |      | XXXX         | XXXX                                  | XXXX     | 90-BF   |  |

|    |                            | 11XX | XXXX         | XXXX                                  | XXXX     | C0-FF   |  |

Table 4. 82730 Datastream Commands

Datastream commands can be used for changing Row Characteristics on a row by row basis, for carrying out editing functions and for formatting data into rows and frames. These commands are executed by the MCU immediately after they are encountered. As a convenience for the user, the set of all possible command codes starting with "1" in the two most significant bits has been designated as NOP commands. The user can use these command codes for any desired purpose. All other command codes which are not presently defined, are reserved for future expansion and should not be used by the user. The currently undefined codes cause the RDC (Reserved Datastream Command) status bit to be set and also generate an interrupt, if enabled. Reserved command codes should not be used.

The preceding commands are recognized as valid datastream commands. The corresponding command codes are also indicated. It should be noted that the most significant bit of the command bit is always 1, in order for the word to be interpreted as command.

The "Init Next Process" command can be issued only through a command process in Virtual Screen Display. It is included in this list because its operation is analogous to a datastream command in a virtual screen access environment. Also, in virtual screen display certain datastream commands are interpreted differently, depending upon whether they are encountered in a process datastream or as command process commands. When a command is ignored (becomes a NO-OP) in a virtual display, any parameters that are associated with it are also ignored. The command process command operation is discussed separately. The operation of all other datastream commands is described below.

#### ENDROW

| 15 | 14  | 8    | 7    | 0    |

|----|-----|------|------|------|

| 1  | 000 | 0000 | XXXX | XXXX |

This command signifies that no more characters will be loaded in the Row Buffer for this row and an End of Row indicator is stored accordingly. When the row currently being loaded is displayed, the Display Generator (DG) will blank the screen from the end of row character position until the physical end of row.

The Micro Controller Unit (MCU) stops fetching data and waits for DG to swap the Row Buffers. The data access task is resumed following the buffer swap. If a physical end of frame is reached while the MCU is waiting for a buffer swap the MCU ceases to wait and executes an EOF (End of Frame) command.

In virtual display, this command is interpreted as a VEOR (Virtual End of Row) if encountered in a virtual process datastream.

# int<sub>e</sub>ľ

# VEOR

ENDROW command in a virtual process datastream is interpreted as VEOR (Virtual End of Row) and it terminates a virtual row. The current LPTR is stored in the process header addressed by the "Process Addr" register. The Max Count register is also stored in the Max DMA Count location in the process header. Similarly, the Field Attribute Mask is also stored in the header. In addition, in auto linefeed mode (ALF = 1) other parameters characterizing the process state are also saved in the header. The "Process Addr" register is loaded with the address of the header of the next process fetched from the Access table. The "Access Tab Addr" register is post-incremented by two if a 16-bit addressing option is used and by four if 32-bit addressing is used. The data access task is then resumed for the next process.

| EOF |     |      |      |      |

|-----|-----|------|------|------|

| 15  | 14  | 8    | 7    | 0    |

| 1   | 000 | 0001 | XXXX | XXXX |

This command (End of Frame) signifies that no more characters will be loaded in the Row Buffers for this frame. The Micro Controller Unit (MCU) stops fetching data words and waits for the physical end of frame. If a virtual display is in progress, this command is interpreted as VEOS (Virtual End of Frame), if encountered in a virtual process datastream.

The Display Generator (DG) swaps the row buffers at the end of the current display row and starts displaying the row containing the EOF command. When the character preceding the EOF command is displayed, the DG blanks the screen until the physical end of frame. The MCU fetches the Status Row data then waits until its display is completed. It then performs the actions described below.

If LPEN has been enabled and a rising edge on the LPEN input has been detected, the LPENROW and LPENCOL positions in the command block are updated and the LPU status bit is set. If a Channel Attention has occurred, i.e., if CA has been activated, the command byte is fetched from command block and the specified channel command is executed. If the command issued is a "Stop Display" command, the MCU will terminate the display process and wait for the next channel attention. Otherwise, the MCU resumes the data access task be reinitializing pointers for the new frame and continues to fill the Row Buffers.

# VEOF

EOF command in a virtual process datastream is interpreted as VEOF (Virtual End of Frame). It provides for reinitialization of LPTR using LISTSWITCH, LBASE0 AND LBASE1 for each process, analogous to the automatic reinitialization of LPTR at each end of frame in a Normal Display.

LPTR for the current process is reinitialized using LISTSWITCH, LBASE0 and LBASE1 contained in the process header. The End of Display (EOD) bit in the header is set to 1. The current process is terminated as in a VEOR and the next process in Access Table is accessed.

| EOL |     |      |      |      |

|-----|-----|------|------|------|

| 15  | 14  | 8    | 7    | 0    |

| 1   | 000 | 0010 | XXXX | XXXX |