# **Trademark Acknowledgements**

$MGA, ^{TM} MGA-1064SG, ^{TM} MGA-1164SG, ^{TM} MGA-2064W, ^{TM} MGA-2164W, ^{TM} MGA-VC064SFB, ^{TM} MGA Marvel, ^{TM} MGA Millennium, ^{TM} MGA Mystique, ^{TM} MGA Rainbow Runner, ^{TM} MGA DynaView, ^{TM} PixelTOUCH, ^{TM} MGA Control Panel, ^{TM} and Instant ModeSWITCH, ^{TM} are trademarks of Matrox Graphics Inc.$

Matrox<sup>®</sup> is a registered trademark of Matrox Electronic Systems Ltd.

VGA,<sup>®</sup> is a registered trademark of International Business Machines Corporation; Micro Channel<sup>TM</sup> is a trademark of International Business Machines Corporation.

Intel<sup>®</sup> is a registered trademark, and 386,<sup>TM</sup> 486,<sup>TM</sup> Pentium,<sup>TM</sup> and 80387<sup>TM</sup> are trademarks of Intel Corporation.

Windows<sup>TM</sup> is a trademark of Microsoft Corporation; Microsoft,<sup>®</sup> and MS-DOS<sup>®</sup> are registered trademarks of Microsoft Corporation.

AutoCAD<sup>®</sup> is a registered trademark of Autodesk Inc.

Unix<sup>TM</sup> is a trademark of AT&T Bell Laboratories.

X-Windows<sup>™</sup> is a trademark of the Massachusetts Institute of Technology.

AMD<sup>TM</sup> is a trademark of Advanced Micro Devices. Atmel<sup>®</sup> is a registered trademark of Atmel Corporation. Catalyst<sup>TM</sup> is a trademark of Catalyst Semiconductor Inc. SGS<sup>TM</sup> is a trademark of SGS-Thompson. Toshiba<sup>TM</sup> is a trademark of Toshiba Corporation. Texas Instruments<sup>TM</sup> is a trademark of Texas Instruments. National<sup>TM</sup> is a trademark of National Semiconductor Corporation. Microchip<sup>TM</sup> is a trademark of Microchip Technology Inc.

All other nationally and internationally recognized trademarks and tradenames are hereby acknowledged.

# This document contains confidential proprietary information that may not be disclosed without written permission from Matrox Graphics Inc.

© Copyright Matrox Graphics Inc., 1997. All rights reserved.

Disclaimer: Matrox Graphics Inc. reserves the right to make changes to specifications at any time and without notice. The information provided by this document is believed to be accurate and reliable. However, no responsibility is assumed by Matrox Graphics Inc. for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Matrox Graphics Inc. or Matrox Electronic Systems Ltd.

#### **Chapter 1: MGA Overview**

| 1.1 I   | ntroduction                               | 2 |

|---------|-------------------------------------------|---|

| 1.2 \$  | System Block Diagram                      | 3 |

| 1.3 A   | Application Areas                         | 3 |

| 1.4 7   | Typical Implementation                    | 3 |

|         | 1.4.1 Target Markets                      | 3 |

| 1.5 F   | Features                                  | ŧ |

|         | 1.5.1 Core GUI Accelerator 1-4            | ŧ |

|         | 1.5.2 3D Texture Mapping Engine 1-4       | ŧ |

|         | 1.5.3 Digital Video Engine                | 5 |

|         | 1.5.4 DirectDraw Support                  | 5 |

|         | 1.5.5 Direct 3D Support 1-5               | 5 |

|         | 1.5.6 Integrated DAC                      | 3 |

|         | 1.5.7 Synchronous Memory Interface        | 3 |

|         | 1.5.8 Miscellaneous                       | 3 |

| 1.6 7   | Typographical Conventions Used.       1-7 | 7 |

| 1.7 L   | Locating Information                      | 7 |

| Chapter | 2: MGA-1064SG Overview                    |   |

| 2.1 I   | ntroduction.                              | 2 |

| 2.2 F   | PCI Bus interface                         | 2 |

| 2.3 \   | /GA Graphics Controller                   | 2 |

| 2.4 \   | /GA Attributes Controller                 | 2 |

| 2.5 0   | CRTC                                      | 2 |

| 2.6 \   | /ideo Interface                           | 2 |

| 2.7 A   | Address Processing Unit (APU)             | ŧ |

| 2.8 [   | Data Processing Unit (DPU)2-4             | 1 |

| 2.9 1   | ۲exture Mapper                            | ŧ |

| 2.10    | Memory Controller                         | ŧ |

| Chapter | 3: Resource Mapping                       |   |

# 3.1 Memory Mapping 3-2 3.1.1 Configuration Space Mapping 3-2 3.1.2 MGA General Map 3-3 3.1.3 MGA Control Aperture 3-4 3.2 Register Mapping 3-5

# **Chapter 4: Register Descriptions**

| 4.1 | Power Graphic Mode Register Descriptions.              | 4-2 |

|-----|--------------------------------------------------------|-----|

|     | 4.1.1 Power Graphic Mode Configuration Space Registers | 4-2 |

| 4.1.2 Power Graphic Mode Memory Space Registers | 4-19   |

|-------------------------------------------------|--------|

| 4.2 VGA Mode Registers                          | 4-85   |

| 4.2.1 VGA Mode Register Descriptions            | . 4-85 |

| 4.3 DAC Registers 4                             | 1-159  |

| 4.3.1 DAC Register Descriptions4                | 1-159  |

# **Chapter 5: Programmer's Specification**

| 5.1 PCI Interface                                                        | 5-2 |

|--------------------------------------------------------------------------|-----|

| 5.1.1 Introduction                                                       | 5-2 |

| 5.1.2 PCI Retry Handling                                                 | 5-3 |

| 5.1.3 PCI Burst Support                                                  | 5-3 |

| 5.1.4 PCI Target-Abort Generation                                        | 5-4 |

| 5.1.5 Transaction Ordering5                                              | 5-4 |

| 5.1.6 Direct Access Read Cache5                                          | 5-4 |

| 5.1.7 Big Endian Support5                                                | 5-5 |

| 5.1.8 Host Pixel Format5                                                 | 5-8 |

| 5.2 Memory Interface 5-7                                                 | 14  |

| 5.2.1 Frame Buffer Organization5-                                        | 14  |

| 5.2.2 Pixel Format                                                       | 18  |

| 5.3 Chip Configuration and Initialization 5-                             | 19  |

| 5.3.1 Reset                                                              | 19  |

| 5.3.2 Operations After Hard Reset                                        | 20  |

| 5.3.3 Power Up Sequence                                                  |     |

| 5.3.4 Operation Mode Selection                                           | 22  |

| 5.4 Direct Frame Buffer Access 5-2                                       |     |

| 5.5 Drawing in Power Graphic Mode 5-2                                    | 25  |

| 5.5.1 Drawing Register Initialization Using General Purpose Pseudo-DMA5- |     |

| 5.5.2 Overview                                                           | 26  |

| 5.5.3 Global Initialization (All Operations)                             |     |

| 5.5.4 Line Programming                                                   |     |

| 5.5.5 Trapezoid / Rectangle Fill Programming                             | 33  |

| 5.5.6 Bitblt Programming5-4                                              | 40  |

| 5.5.7 ILOAD Programming                                                  |     |

| 5.5.8 Scaling Operations5-                                               | 51  |

| 5.5.9 IDUMP Programming                                                  | 60  |

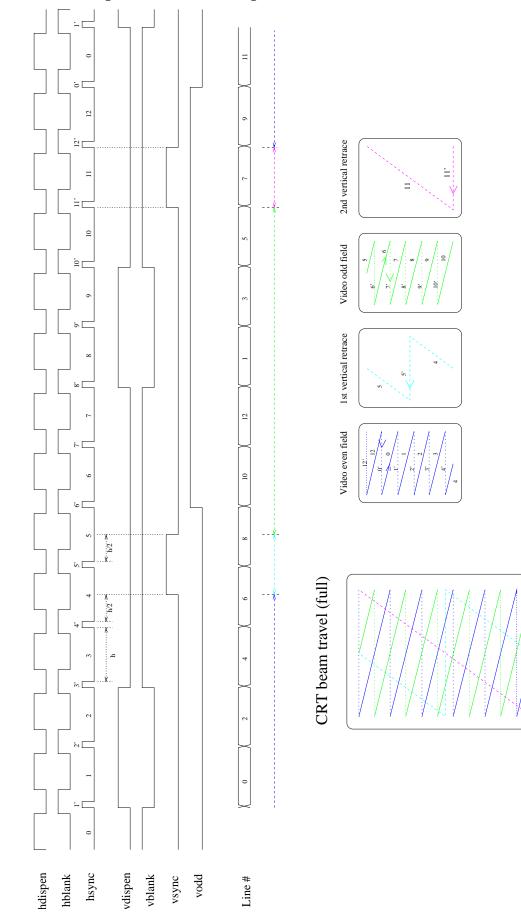

| 5.6 CRTC Programming 5-6                                                 | 62  |

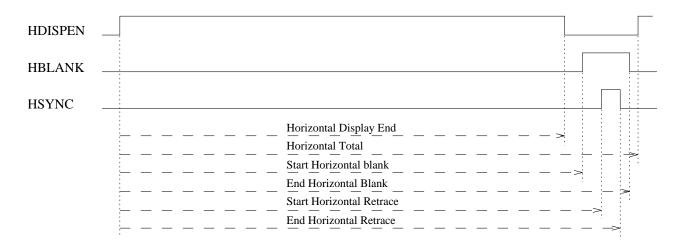

| 5.6.1 Horizontal Timing5-6                                               |     |

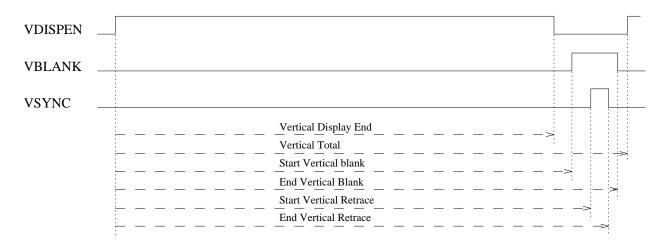

| 5.6.2 Vertical Timing5-6                                                 | 63  |

| 5.6.3 Memory Address Counter                                             | 64  |

|                                                                          | - · |

| 5.6.4 Programming in VGA Mode5-6                                         |     |

| 5    | .7 Video Interface                                                                                                                                                                                                                                                                                                                                             |                                                             |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|      | 5.7.1 Operation Modes 5-                                                                                                                                                                                                                                                                                                                                       | -70                                                         |

|      | 5.7.2 Palette RAM (LUT)                                                                                                                                                                                                                                                                                                                                        | -73                                                         |

|      | 5.7.3 Hardware Cursor                                                                                                                                                                                                                                                                                                                                          | -73                                                         |

|      | 5.7.4 Keying Functions                                                                                                                                                                                                                                                                                                                                         | -74                                                         |

|      | 5.7.5 Zooming                                                                                                                                                                                                                                                                                                                                                  | -74                                                         |

|      | 5.7.6 Feature Connector                                                                                                                                                                                                                                                                                                                                        | -74                                                         |

|      | 5.7.7 Test Functions                                                                                                                                                                                                                                                                                                                                           | -74                                                         |

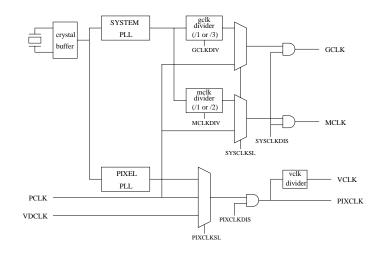

|      | 5.7.8 PLL Clock Generators                                                                                                                                                                                                                                                                                                                                     | -75                                                         |

| 5    | .8 Interrupt Programming                                                                                                                                                                                                                                                                                                                                       | -78                                                         |

|      | .9 Power Saving Features                                                                                                                                                                                                                                                                                                                                       |                                                             |

|      |                                                                                                                                                                                                                                                                                                                                                                |                                                             |

| Cha  | star 6. Hardwara Dagianar'a Natag                                                                                                                                                                                                                                                                                                                              |                                                             |

| Glia | oter 6: Hardware Designer's Notes                                                                                                                                                                                                                                                                                                                              |                                                             |

|      |                                                                                                                                                                                                                                                                                                                                                                | 6-2                                                         |

| e    | -                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| e    | .1 Introduction.                                                                                                                                                                                                                                                                                                                                               | 6-2                                                         |

| 6    | .1 Introduction                                                                                                                                                                                                                                                                                                                                                | 6-2<br>6-2                                                  |

| 6    | .1 Introduction                                                                                                                                                                                                                                                                                                                                                | 6-2<br>6-2<br>6-3                                           |

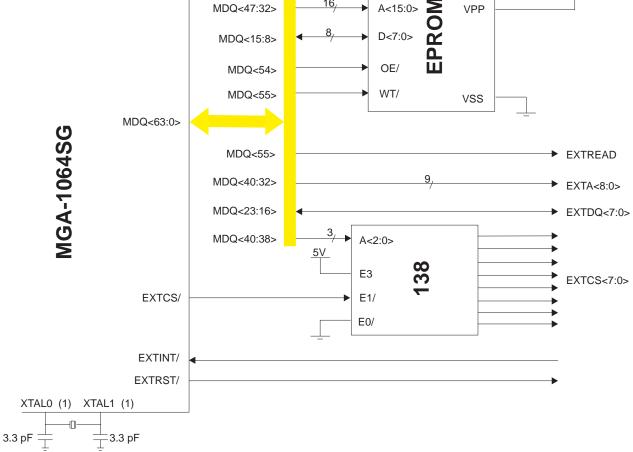

| 6    | .1 Introduction.       .2         .2 PCI Interface       .2         .3 External Devices.       .2         .4 Memory Interface       .2                                                                                                                                                                                                                         | 6-2<br>6-2<br>6-3<br>6-5                                    |

| 6    | .1 Introduction.                                                                                                                                                                                                                                                                                                                                               | 6-2<br>6-2<br>6-3<br>6-5<br>6-5                             |

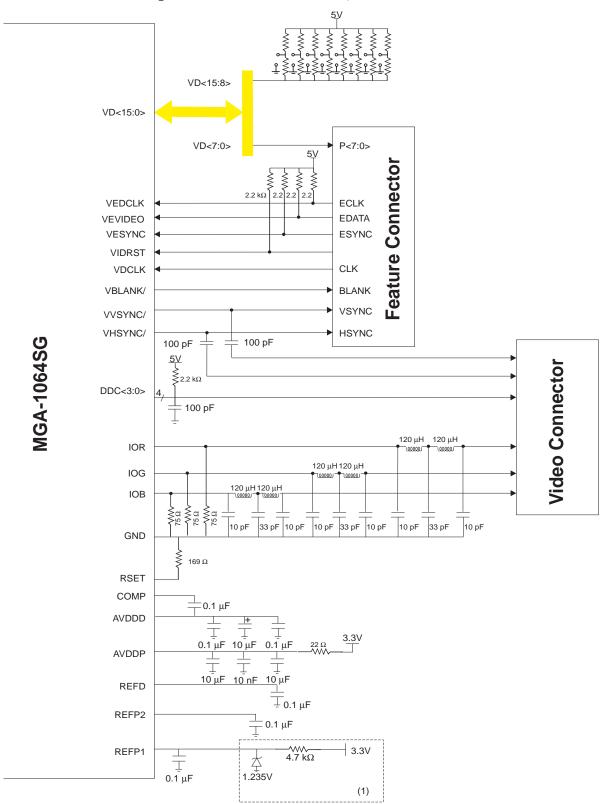

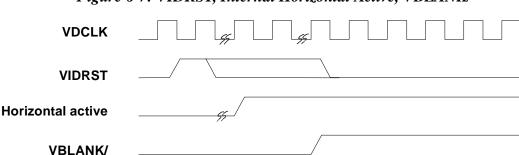

| 6    | .1 Introduction.       .2         .2 PCI Interface       .2         .3 External Devices.       .2         .4 Memory Interface       .2         .6.4.1 SDRAM/SGRAM Configurations.       .2         .5 Video interface       .6                                                                                                                                 | 6-2<br>6-3<br>6-5<br>6-5<br>-10                             |

| 6    | .1 Introduction.                                                                                                                                                                                                                                                                                                                                               | 6-2<br>6-3<br>6-5<br>6-5<br>-10<br>-11                      |

| 6    | .1 Introduction.                                                                                                                                                                                                                                                                                                                                               | 6-2<br>6-3<br>6-5<br>6-5<br>-10<br>-11<br>-12               |

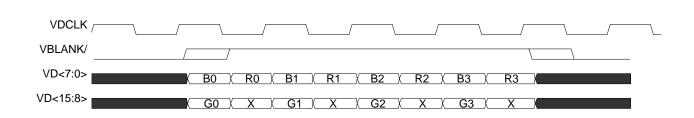

|      | .1 Introduction.       .2         .2 PCI Interface       .2         .3 External Devices.       .2         .4 Memory Interface       .2         .6.4.1 SDRAM/SGRAM Configurations.       .2         .5 Video interface       .2         .6.5.1 Slaving the MGA-1064SG.       .6         .6.5.2 Genlock Mode       .6         .6.5.3 MAFC Data Sequence       .6 | 6-2<br>6-3<br>6-5<br>6-5<br>-10<br>-11<br>-12<br>-13        |

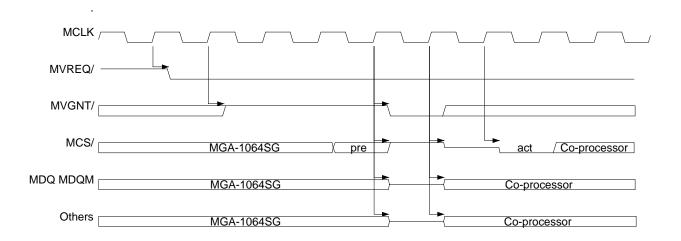

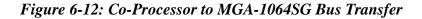

|      | .1 Introduction.                                                                                                                                                                                                                                                                                                                                               | 6-2<br>6-3<br>6-5<br>6-5<br>-10<br>-11<br>-12<br>-13<br>-13 |

Contents 4

| Chapter 1: MGA Overview Figure 1-1: System Block Diagram                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2: MGA-1064SG Overview Figure 2-1: MGA-1064SG Block Diagram                                                                                                                                                                                                                                |

| Chapter 3: Resource Mapping Not Applicable                                                                                                                                                                                                                                                         |

| Chapter 4: Register Descriptions Not Applicable                                                                                                                                                                                                                                                    |

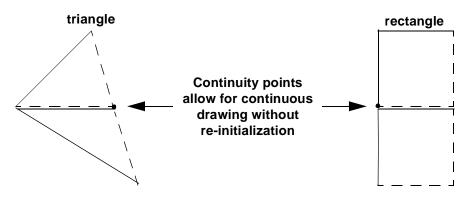

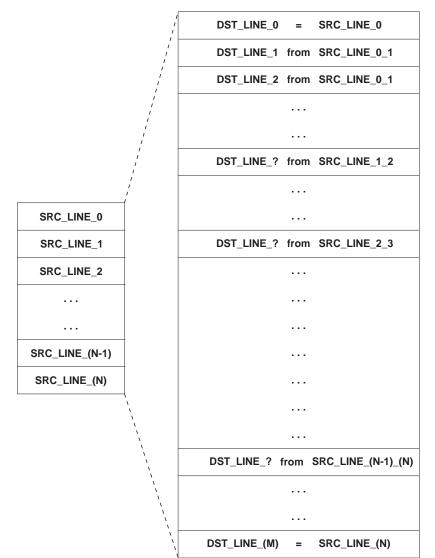

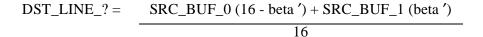

| Chapter 5: Programmer's Specification<br>Figure 5-1: Drawing Multiple Primitives                                                                                                                                                                                                                   |

| Figure 5-6: Clock Scheme                                                                                                                                                                                                                                                                           |

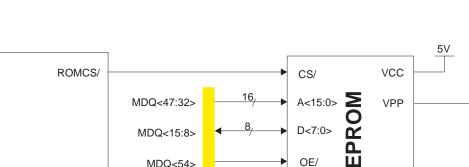

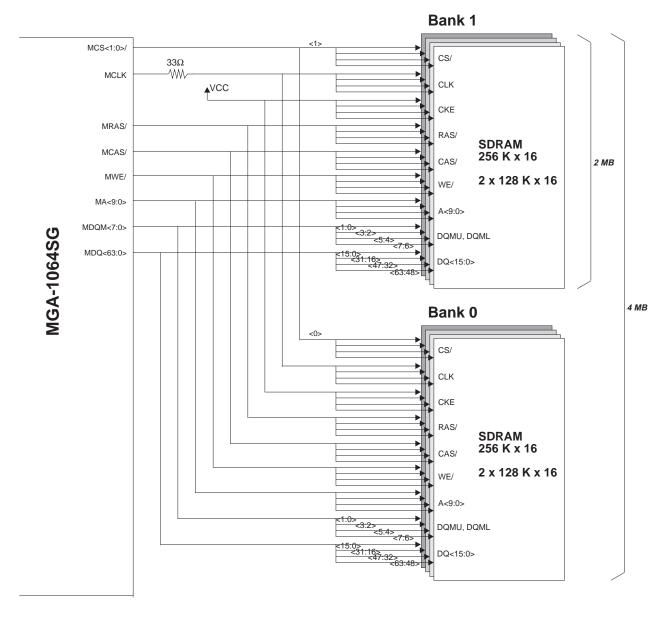

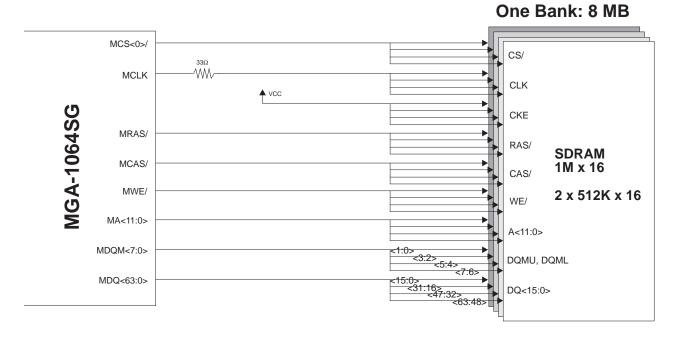

| Figure 6-1: PCI Interface6-2Figure 6-2: External Device Connections6-4Figure 6-3: SGRAM Connection6-7Figure 6-4: SDRAM Connection (256Kx16)6-8Figure 6-5: SDRAM Connection (1Mx16)6-9                                                                                                              |

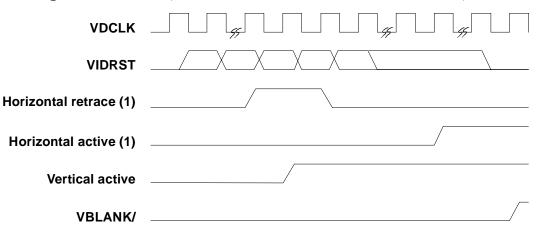

| Figure 6-6: Feature Connector, Video Connector6-10Figure 6-7: VIDRST, Internal Horizontal Active, VBLANK/.6-11Figure 6-8: VIDRST, Internal Horizontal Retrace/Vertical Active, VBLANK/.6-11Figure 6-9: VIDRST, Internal Horizontal/Vertical Active, and VBLANK/.6-12Figure 6-10: MAFC Waveform6-13 |

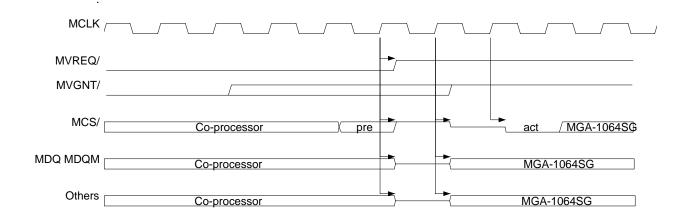

| Figure 6-11: MGA-1064SG to Co-Processor Bus Transfer                                                                                                                                                                                                                                               |

#### **Chapter 1: MGA Overview**

| Table 1-1: Typographical Conventions.         1- | -7 | • |

|--------------------------------------------------|----|---|

|--------------------------------------------------|----|---|

#### Chapter 2: MGA-1064SG Overview

Not Applicable

### **Chapter 3: Resource Mapping**

| Table 3-1: MGA-1064SG Configuration Space Mapping         MGA-1064SG Configuration Space Mapping | 3-2 |

|--------------------------------------------------------------------------------------------------|-----|

| Table 3-2: MGA General Map                                                                       | 3-3 |

| Table 3-3: MGA Control Aperture (extension of Table 3-2)                                         | 3-4 |

| Table 3-4: Register Map                                                                          | 3-5 |

#### **Chapter 4: Register Descriptions**

Not Applicable

#### **Chapter 5: Programmer's Specification**

| -22  |

|------|

| -47  |

| -49  |

| -50  |

| HIQH |

| 5-51 |

| 5-58 |

| 5-58 |

| 5-61 |

| 61   |

|      |

#### **Chapter 6: Hardware Designer's Notes**

| Table 6-1: Supported SGRAM/SDRAM Commands                     | 6-5 |

|---------------------------------------------------------------|-----|

| Table 6-2:       12-bit Address Configuration (memconfig = 1) | 6-6 |

| Table 6-3: 10-bit Address Configuration (memconfig = 0)       | 6-6 |

# Chapter 1: MGA Overview

| Introduction                   | 1-2 |

|--------------------------------|-----|

| System Block Diagram           | 1-3 |

| Application Areas              | 1-3 |

| Typical Implementation         | 1-3 |

| Features                       | 1-4 |

| Typographical Conventions Used | 1-7 |

| Locating Information           | 1-7 |

#### 1.1 Introduction

The Matrox MGA-1064SG is a next generation 3D graphics, multimedia and Windows accelerator. In one low-cost package, the MGA-1064SG:

- Provides superior Windows performance

- Accelerates 3D texture mapped consumer applications such as PC games with the Matrox Fast Texture Architecture

- Is fully Microsoft DirectDraw and Direct 3D compliant

- Accelerates digital video including software MPEG

- Has fast VGA acceleration

- Includes an integrated DAC.

The Matrox MGA-1064SG has special features specifically designed to provide superior 3D game performance in a 2 MByte frame buffer. Matrox MGA-1064SG is intended to provide a complete solution for home PC users who are interested in top performance in 3D game and multimedia applications, but who are also interested in leveraging their home PC as a home office and education center. It is also suitable for GUI environments such as Windows NT, IBM OS/2 PM, Unix X-Windows, and AutoCAD.

The MGA-1064SG series has the same Windows acceleration core as the award-winning Matrox MGA-2064W used on the MGA Millennium graphics card, but works with either SGRAM or SDRAM rather than WRAM. The MGA-1064SG is capable of supporting frame buffer sizes from 2 to 8 MBytes. A key design feature of MGA-1064SG is the memory/graphics clock generator. This supports a ratio of 1.5:1 which optimizes memory bandwidth and the graphics engine clock.

The integrated DAC in MGA-1064SG eliminates the need for an external DAC. This substantially lowers the cost and space required for the graphics sub-system.

The centerpiece of MGA-1064SG is the Matrox Fast Texture Architecture, a full-featured 3D rendering engine, the capabilities of which are aimed squarely at optimizing 3D texture mapped games. This 3D engine is an advanced renderer with full perspective correct texture mapping, lighting, Gouraud shading, optional 16-bit Z-buffering, bus mastering, efficient use of texture memory, keying on textures, high color output (16 bpp), and the ability to work in conjunction with the video engine to use video as a source for texturing. The key feature of the Matrox Fast Texture Architecture is excellent cost/performance. Matrox's texture compression model saves on memory usage, enabling low cost and high performance in a 2 MByte frame buffer

The MGA-1064SG core engine fully implements the Matrox Video Architecture with its integrated digital video scaling, filtering and color space conversion engine. This architecture supports both shared frame buffer and split frame buffer (overlay) modes of operation to provide maximum flexibility in combining video with graphics. This architecture supports video sprites, video texture maps, graphics overlay, and many other methods of combining video with graphics. The MGA-1064SG can be upgraded with the Matrox Rainbow Runner proprietary video engine to achieve a comprehensive set of high quality video capabilities.

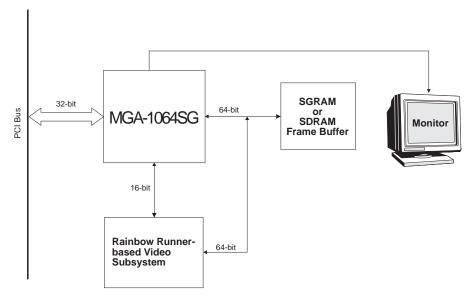

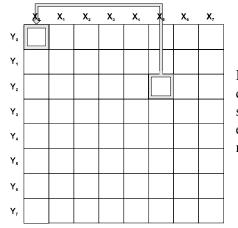

#### 1.2 System Block Diagram

Figure 1-1: System Block Diagram

## 1.3 Application Areas

- Windows accelerator with high performance levels, which is ideal for mid-range system requirements. The MGA-1064SG will broaden the MGA family's market penetration by delivering a strong price/performance point for users who do not need the top performance at ultra high resolution and color depths provided by MGA Millennium.

- Full acceleration of the next generation of Windows multimedia and game applications. Specifically, 3D texture mapped games achieve a significant boost in performance and image quality with the MGA-1064SG 3D engine. In addition, all other types of games will be accelerated by a combination of the MGA-1064SG's DirectDraw and Direct Video engine.

- Digital video playback is accelerated to full screen, full motion, with high-quality scaling. The architecture supports all of today's popular CODECs including Indeo and software MPEG. OM-1 and Quartz compatibility is provided.

- Full acceleration of all MS-DOS applications via MGA-1064SG's ultra-fast 32-bit VGA core.

# **1.4 Typical Implementation**

MGA-1064SG is ideal for use as an add-in graphics card, or on the motherboard with frame buffer RAM.

#### 1.4.1 Target Markets

- The home, SOHO, and multimedia PC markets

- Mainstream business markets

- The computer gaming market

# 1.5 Features

#### 1.5.1 Core GUI Accelerator

- Based on the current award-winning MGA-2064W core

- Line draw engine with patterning

- 3D polygons with Gouraud shading

- Optional Z-buffer

- 2D polygons with patterning capabilities

- BITBLT engine

- Sync reset input for video genlock and overlay

- DPMS and Green PC support

- Hardware pan and zoom

- DDC level 2B compliant

- 44 MHz drawing engine

- 66 MHz operation for the memory interface

#### 1.5.2 3D Texture Mapping Engine

- Perspective Correct Texture Mapping

- True color lighting of textures

- Hardware dithering of lit textures

- 16-bit Z-buffer (optionally enabled or disabled)

- Double buffering

- Screen transparency

- Storage of source textures in off-screen frame buffer memory

- Source textures may be in following formats:

- Color Look Up Table (compressed) 4 bpp, 8bpp.

- 3:3:2, 5:6:5, 5:5:5.

- Look-up table translations from CLUT4 and CLUT8 to 5:6:5 on-the-fly

- Command list processing via bus mastering

- Keying on textures is supported

- Digital video as source for texturing is supported

#### 1.5.3 Digital Video Engine

- True linear interpolation scaling filter in both X and Y

- Hardware color space conversion engine

- 8 MByte window for ILOAD and IDUMP operations

- Split frame buffer support for true graphics overlay (graphics and video are in separate sections of the frame buffer, with keying in the DAC):

- 2G8/V16 : graphics 8-bit pseudo color or 3:3:2, video 5:5:5 dithered

- G16/V16 : graphics 5:6:5 & 5:5:5, video 5:5:5 dithered

- Synchronized video/graphics updates (no tearing) are supported

- Supports any number of video windows/sprites simultaneously

- Split frame buffer is supported simultaneously with shared frame buffer mode layering

- Direct frame buffer access sees each buffer linearly

- Shared frame buffer mode supports graphics and video written to a shared surface through layering

- Supports 8, 16, 24, or 32 bit/pixel configurations

- Graphics and video pixels must have the same pixel depth

#### 1.5.4 DirectDraw Support

- Hardware scaling and color space conversion engine fully accelerates digital video

- Support BITBLT & ILOAD functions with color key for full transparent blit support

- Full 8 MByte window on linear mapping of frame buffer

- Equality compare with plane masking for transparent blits

- Single register page flip

- Programmable blitter stride

- Ability to read the current scan line

- Ability to tell when the vertical blank begins

- Interrupt generated on VSYNC

#### 1.5.5 Direct 3D Support

- Texture mapping

- Perspective correct

- Monochrome and true color lighting

- Decal

- Texture wrapping and clamping

- 16-bit true color or 8- or 4-bit palettized

- Gouraud shading

- Optional Z-buffer and Z-test

- Color and Z-masking

- Dithering

- Sub-pixel positioning

- Transparency

- Flat alpha stipple

- Bus mastering

#### 1.5.6 Integrated DAC

- 135 MHz operation

- Supports shared memory and graphic overlay modes

- $\blacksquare$  3 x 256 x 8 lookup table

- Hardware cursor

- VGA compatible

#### 1.5.7 Synchronous Memory Interface

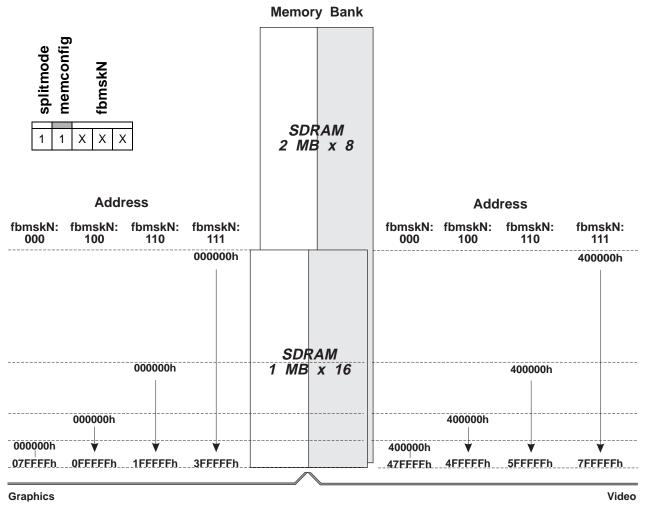

- SGRAM 256K x 32. Supports block write and write per bit for added performance

- SDRAM 256K x 16, 1M x 16, 2M x 8

- Supports from 2 to 8 MBytes of memory

- Up to 4 banks of 256K x 32 SGRAM

- Up to 2 banks of 256K x 16 SDRAM

- 1 bank of 1M x 16 SDRAM

- 1 bank of 2M x 8 SDRAM.

#### 1.5.8 Miscellaneous

- Feature connector interface

- 8-bit VGA mode

- 16 bit output mode for the Rainbow Runner video encoder (32 bpp multiplexed to 16 bit bus).

- Host interface

- PCI 2.1 compliant.

- PCI bus master capable. Primarily used to increase 3D performance by offloading the CPU.

- VESA 2.0-compliant DOS applications running at a resolution of 320 x 200 can be scaled up to 640 x 480.

- Higher resolutions are possible without changing the frame rate.

- Filtering in the X-direction is supported.

## **1.6 Typographical Conventions Used**

Table 1-1: Typographical Conventions

| Description                                                                                                                                                                                           | Example                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Active low signals are indicated by a trailing forward slash. Signal names appear in upper-case characters.                                                                                           | VHSYNC/                       |

| Numbered signals appear within angle brackets, separated by a colon.                                                                                                                                  | MA<8:0>                       |

| Register names are indicated by upper-case bold sans-serif letters.                                                                                                                                   | DEVID                         |

| Fields within registers are indicated by lower-case bold sans-serif letters.                                                                                                                          | vendor                        |

| Bits within a field appear within angle brackets, separated by a colon.                                                                                                                               | vendor<15:0>                  |

| Hexadecimal values are indicated by a trailing letter 'h'.                                                                                                                                            | CFFFh                         |

| Binary values are indicated by a trailing letter 'b' or are enclosed in single quotes, as: '00' or '1'. Also, in a bulleted list in a register description field, 0: and 1: are assumed to be binary. | 0000 0010b                    |

| Special conventions are used for the register descriptions. Refer to the sample re-<br>in Sections 4.1.1, 4.1.2, 4.2.1, and 4.3.1.                                                                    | gister description pages      |

| In a table, X = "don't care" (the value doesn't matter)                                                                                                                                               | 1X = Register Set C           |

| Emphasized text and table column titles are set in bold italics.                                                                                                                                      | This bit <i>must be set</i> . |

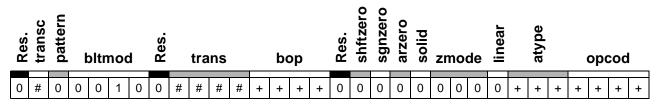

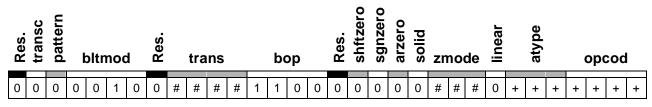

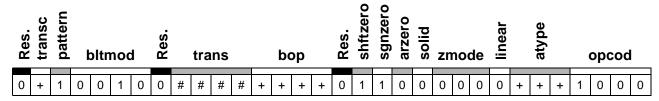

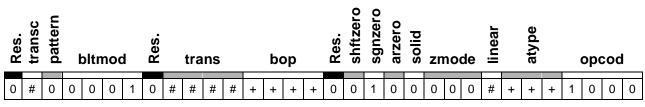

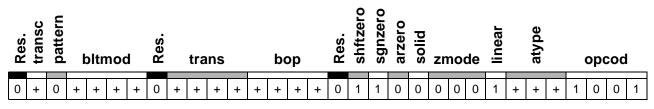

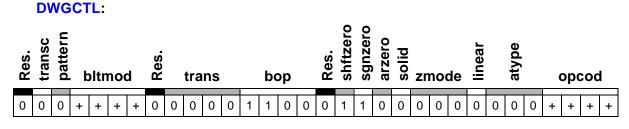

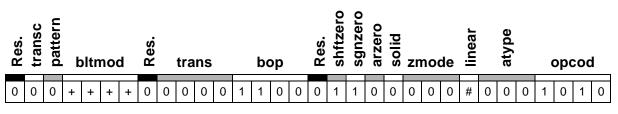

| In Chapter 5's <b>DWGCTL</b> illustrations, the '+' and '#' symbols have a special meaning. This is explained in 'Overview' on page 5-26.                                                             | trans                         |

• A vertical bar in the margin (as seen here on the right) indicates a change made since the release of Revision 1 of this manual, which was dated April 5, 1996.

# **1.7 Locating Information**

The MGA-1064SG register descriptions are located in Chapter 4. They are divided into several sections, and arranged in alphabetical order within each section.

- To look up a register by name when you know which section it's in, go to that section and search the running headers at the top of the page for the register you want. (The sections are identified in 'Contents' at the front of the manual, on page 4-1, and within the page footers of Chapter 4.)

- If you don't know which section it's in, look the register up in the Index in the back.

- To look up a register by its index or address, refer to the tables in Chapter 3. Indirect access register indexes are also duplicated on the description page of the direct access register that they refer to.

- To look up a particular field within a register, look in the Alphabetical List of Register Fields near the back of the manual.

Information on how to program the MGA-1064SG registers is found in Chapter 5, while information relating to hardware design is located in Chapter 6.

At the beginning of this manual you'll find a complete table of Contents, followed by a List of (major) Figures, and a List of (major) Tables.

# Chapter 2: MGA-1064SG Overview

| Introduction                  | 2-2 |

|-------------------------------|-----|

| PCI Bus interface             | 2-2 |

| VGA Graphics Controller       | 2-2 |

| VGA Attributes Controller     | 2-2 |

| CRTC                          | 2-2 |

| Video Interface               | 2-2 |

| Address Processing Unit (APU) | 2-4 |

| Data Processing Unit (DPU)    | 2-4 |

| Texture Mapper                | 2-4 |

| Memory Controller             | 2-4 |

|                               |     |

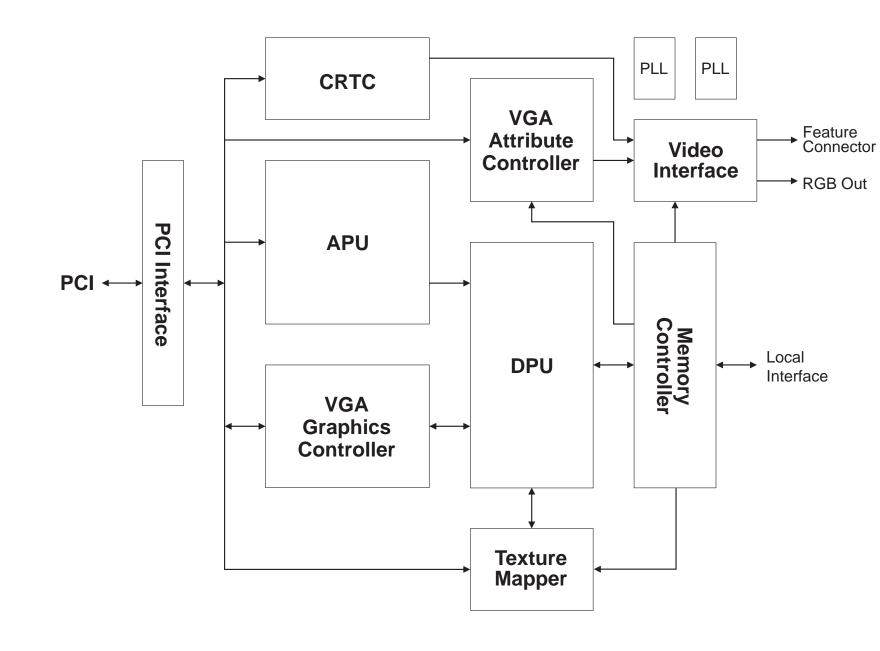

### 2.1 Introduction

The MGA-1064SG chip is a stand-alone graphics controller which is composed of several sections that work together to accomplish the tasks that are required of them. The individual sections of the MGA-1064SG chip are listed below and described in detail in the remainder of this chapter.

- PCI bus interface

- VGA graphics controller

- VGA attributes controller

- CRTC

- Video Interface

- Address Processing Unit (APU)

- Data Processing Unit (DPU)

- Texture Mapper

- Memory Controller

## 2.2 PCI Bus interface

This section of the MGA-1064SG chip implements the interface with the host processor. It includes:

- All of the decoding circuitry for the PCI interface

- Decoding of all resources

- Configuration registers

- Bus mastering circuitry

# 2.3 VGA Graphics Controller

This section of the MGA-1064SG implements the VGA-compatible access to the frame buffer. This section includes:

- Graphics controller registers

- Data path between the host and the frame buffer

# 2.4 VGA Attributes Controller

This section implements the display refresh for standard VGA modes as well as for all character modes.

# 2.5 CRTC

This section generates the horizontal and vertical timing for driving display data and addresses from the frame buffer. The CRTC is VGA-compatible, with some extensions for the Power Graphic modes.

# 2.6 Video Interface

The video interface converts display pixels from the frame buffer into analog signals that are sent to the CRT monitor. It includes the color LUT, cursor generation, keying logic, the MAFC port, the DAC registers, the DAC, the system clock PLL, and the pixel clock PLL.

Figure 2-1: MGA-1064SG Block Diagram

MGI Confidential

# 2.7 Address Processing Unit (APU)

This section of the MGA-1064SG chip generates the sequencing for drawing operations. Each drawing operation is broken down into a series of read and write commands which are forwarded to the DPU. The APU section includes:

- Generation of the sequences for each drawing operation

- Generation of the addresses

- Processing of the slope for vectors and trapezoid edges

- Rectangle clipping

# 2.8 Data Processing Unit (DPU)

This section manipulates the data according to the currently-selected operation. The DPU also converts read and write commands from the APU into commands to the memory controller. The DPU includes the:

- Generation of the sequences for every drawing operation

- Funnel shifter for data alignment

- Boolean ALU

- Patterning circuitry

- Color space converter

- Dithering circuitry

- Data FIFO for blit operations

- Color expansion circuitry for character drawing

- Gouraud shading generator

- Depth generation circuitry

# 2.9 Texture Mapper

This section implements the perspective-correct texture mapping feature of the MGA-1064SG. It includes:

- Texture parameter interpolation (STQ)

- Perspective correction circuitry

- Texel address FIFO

- Transparency circuitry

- Texture LUT

- Lighting module

# 2.10 Memory Controller

This section converts the read and write commands issued by internal modules into memory cycles that are sent to the frame buffer. Its functions include:

- Generation of memory cycles

- Interface to the SDRAM/SGRAM

- Arbitration of internal requests to the frame buffer

- Depth comparison circuitry

- All control circuitry for external devices

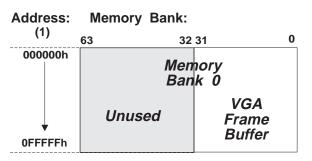

The MGA-1064SG chip can interface directly with the SDRAM/SGRAM chips. A frame buffer of up to 8 MBytes is supported.

# **Chapter 3: Resource Mapping** This chapter includes:

| Register Ma | apping |  | 3-5 |

|-------------|--------|--|-----|

|-------------|--------|--|-----|

# 3.1 Memory Mapping

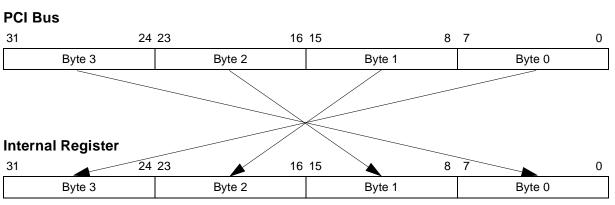

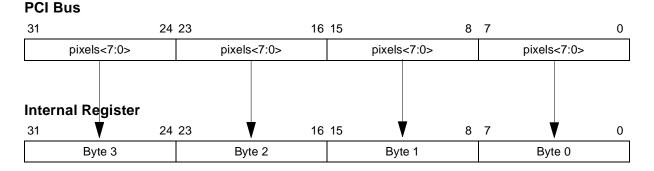

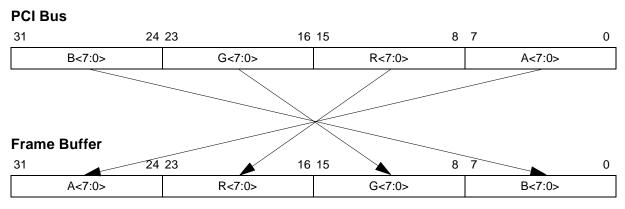

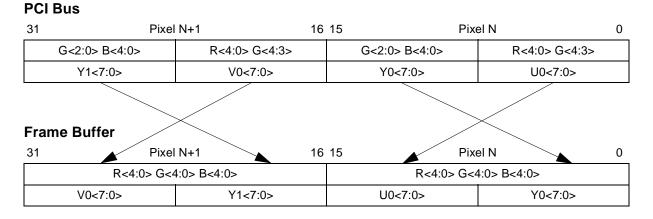

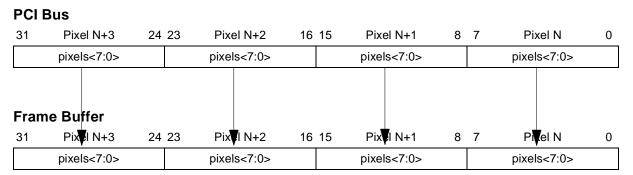

Note that all addresses and bits within dwords are labelled for a little endian processor (X86 series, for example).

# 3.1.1 Configuration Space Mapping

Table 3-1: MGA-1064SG Configuration Space Mapping

| Address | Name/Note | Description                          |

|---------|-----------|--------------------------------------|

| 00h-03h | DEVID     | Device Identification                |

| 04h-07h | DEVCTRL   | Device Control                       |

| 08h-0Bh | CLASS     | Class Code                           |

| 0Ch-0Fh | HEADER    | Header                               |

| 10h-13h | MGABASE1  | MGA Control Aperture Base            |

| 14h-17h | MGABASE2  | MGA Frame Buffer Aperture Address    |

| 18h-1Bh | MGABASE3  | MGA ILOAD Aperture Base Address      |

| 1Ch-2Bh | Reserved  |                                      |

| 2Ch-2Fh | SUBSYSID  | Subsystem ID. Writing has no effect. |

| 30h-33h | ROMBASE   | ROM Base Address                     |

| 34h-3Bh | Reserved  |                                      |

| 3Ch-3Fh | INTCTRL   | Interrupt Control                    |

| 40h-43h | OPTION    | Option                               |

| 44h-47h | MGA_INDEX | MGA Indirect Access Index            |

| 48h-4Bh | MGA_DATA  | MGA Indirect Access Data             |

| 4Ch-4Fh | SUBSYSID  | Subsystem ID. Reading will give 0's. |

| 50h-FFh | Reserved  |                                      |

Writing to a reserved location has no effect. Reading from a reserved location will give 0's. Access to any location (including a reserved one) will be decoded.

#### 3.1.2 MGA General Map

| Address               | Condition                                        | Name/Notes                          |

|-----------------------|--------------------------------------------------|-------------------------------------|

| 000A0000h-000BFFFFh   | <b>GCTL6</b> <3:2> = '00', <b>MISC</b> <1> = '1' | VGA frame buffer <sup>(1) (2)</sup> |

| 000A0000h-000AFFFFh   | GCTL6<3:2> = '01', MISC<1> = '1'                 |                                     |

| 000B0000h-000B7FFFh   | GCTL6<3:2> = '10', MISC<1> = '1'                 |                                     |

| 000B8000h-000BFFFFh   | <b>GCTL6</b> <3:2> = '11', <b>MISC</b> <1> = '1' |                                     |

| ROMBASE + 0000h to    | biosen = 1 (see OPTION)                          | BIOS EPROM <sup>(1)</sup>           |

| ROMBASE + FFFFh       | romen = 1 (see ROMBASE)                          |                                     |

| MGABASE1 + 0000h to   | MGA control aperture                             | (1)                                 |

| MGABASE1 + 3FFFh      | (see Table 3-3)                                  |                                     |

| MGABASE2 + 000000h to | Direct frame buffer access aperture              | (1)(2)(3)                           |

| MGABASE2 + 7FFFFFh    |                                                  |                                     |

| MGABASE3 + 000000h to | 8 MByte Pseudo-DMA window                        | (1)(4)                              |

| MGABASE3 + 7FFFFFh    |                                                  |                                     |

Table 3-2: MGA General Map

<sup>(1)</sup> Memory space accesses are decoded only if **memspace** = 1 (see the **DEVCTRL** configuration register).

<sup>(2)</sup> Hardware swapping for big endian support is performed in accordance with the settings of the **OPMODE** register's **dirDataSiz** bits.

<sup>(3)</sup> The usable range depends on the frame buffer configuration. Reading or writing outside the usable range will yield unpredictable results.

<sup>(4)</sup> Hardware swapping for big endian support is performed in accordance with the settings of the OPMODE register's dmaDataSiz bits.

#### 3.1.3 MGA Control Aperture

Table 3-3: MGA Control Aperture (extension of Table 3-2)

| MGABASE1 +  | Attr. | Mnemonic       | Device name                                   |

|-------------|-------|----------------|-----------------------------------------------|

| 0000h-1BFFh | W     | DMAWIN (ILOAD) | 7KByte Pseudo-DMA window <sup>(1)</sup>       |

|             | R     | DMAWIN (IDUMP) | 7KByte Pseudo-DMA window <sup>(1)</sup>       |

| 1C00h-1DFFh | W     | DWGREG0        | First drawing registers <sup>(2)(3)(4)</sup>  |

| 1E00h-1EFFh | R/W   | HSTREG         | Host registers <sup>(2)(3)</sup>              |

| 1F00h-1FFFh | R/W   | VGAREG         | VGA registers <sup>(5)(3)</sup>               |

| 2000h-2BFFh |       |                | Reserved <sup>(6)</sup>                       |

| 2C00h-2DFFh | W     | DWGREG1        | Second drawing registers <sup>(2)(3)(4)</sup> |

| 2E00h-3BFFh |       |                | Reserved <sup>(6)</sup>                       |

| 3C00h-3C0Fh | R/W   | DAC            | DAC <sup>(3)</sup>                            |

| 3C10h-3DFFh |       |                | Reserved <sup>(6)</sup>                       |

| 3E00h-3FFFh | R/W   | EXPDEV         | Expansion <sup>(7)</sup>                      |

<sup>(1)</sup> Hardware swapping for big endian support is performed in accordance with the settings of the **OPMODE** register's **dmaDataSiz** bits.

<sup>(2)</sup> Hardware swapping for big endian support is performed when the **OPTION** configuration register's **powerpc** bit is '1'.

<sup>(3)</sup> See the register map in Table 3-4 for a more detailed view of this memory space

<sup>(4)</sup> Reads of these locations are not decoded.

<sup>(5)</sup> VGA registers have been memory mapped to provide access to the **CRTC** registers in order to program MGA video modes when the VGA I/O space is not enabled.

<sup>(6)</sup> Reserved locations are decoded. The returned values are unknown.

<sup>(7)</sup> The exact mapping within this range depends on the external connections and on the external devices used.

# 3.2 Register Mapping

Note: For the values in Table 3-4, reserved locations should not be accessed. Writing to reserved locations may affect other registers. Reading from reserved locations will return unknown data.

| Register Mnemonic Name    | Access | Memory<br>Address <sup>(1)</sup> | <i>I/O</i><br>Address <sup>(2)</sup> | Index | Description/Comments               | Page              |

|---------------------------|--------|----------------------------------|--------------------------------------|-------|------------------------------------|-------------------|

| DWGCTL <sup>(3)</sup>     | WO     | 1C00h <sup>(4)</sup>             | -                                    | -     | Drawing Control                    | 4-49              |

| MACCESS <sup>(3)</sup>    | WO     | 1C04h <sup>(4)</sup>             | -                                    | -     | Memory Access                      | 4-64              |

| MCTLWTST                  | WO     | 1C08h <sup>(4)</sup>             | -                                    | -     | Memory Control Wait State          | 4-65              |

| ZORG                      | WO     | 1C0Ch <sup>(4)</sup>             | -                                    | -     | Z-Depth Origin                     | 4-84              |

| PAT0                      | WO     | 1C10h <sup>(4)</sup>             | -                                    | -     | Pattern                            | 4- <del>6</del> 7 |

| PAT1                      | WO     | 1C14h <sup>(4)</sup>             | -                                    | -     | Pattern                            | 4-67              |

| -                         | WO     | 1C18h <sup>(4)</sup>             | -                                    | -     | Reserved                           | -                 |

| PLNWT <sup>(3)</sup>      | WO     | 1C1Ch <sup>(4)</sup>             | -                                    | -     | Plane Write Mask                   | 4-69              |

| BCOL                      | WO     | 1C20h <sup>(4)</sup>             | -                                    | -     | Background Color / Blit Color Mask | 4-27              |

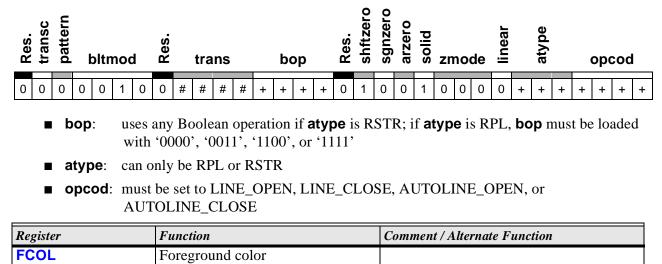

| FCOL                      | WO     | 1C24h <sup>(4)</sup>             | -                                    | -     | Foreground Color / Blit Color Key  | 4-56              |

| -                         | WO     | 1C28h <sup>(4)</sup>             | -                                    | -     | Reserved                           | -                 |

| -                         | WO     | 1C2Ch <sup>(4)</sup>             | -                                    | -     | Reserved (SRCBLT)                  | -                 |

| SRC0                      | WO     | 1C30h <sup>(4)</sup>             | -                                    | -     | Source                             | 4-73              |

| SRC1                      | WO     | 1C34h <sup>(4)</sup>             | -                                    | -     | Source                             | 4-73              |

| SRC2                      | WO     | 1C38h <sup>(4)</sup>             | -                                    | -     | Source                             | 4-73              |

| SRC3                      | WO     | 1C3Ch <sup>(4)</sup>             | -                                    | -     | Source                             | 4-73              |

| XYSTRT <sup>(5)</sup>     | WO     | 1C40h <sup>(4)</sup>             | -                                    | -     | XY Start Address                   | 4-78              |

| XYEND <sup>(5)</sup>      | WO     | 1C44h <sup>(4)</sup>             | -                                    | -     | XY End Address                     | 4-77              |

| -                         | 1C48h  | n-1C4Ch <sup>(4)</sup>           | -                                    | -     | Reserved                           | -                 |

| SHIFT <sup>(5)</sup>      | WO     | 1C50h <sup>(4)</sup>             | -                                    | -     | Funnel Shifter Control             | 4-72              |

| DMAPAD <sup>(5)</sup>     | WO     | 1C54h <sup>(4)</sup>             | -                                    | -     | DMA Padding                        | 4-35              |

| SGN <sup>(5)</sup>        | WO     | 1C58h <sup>(4)</sup>             | -                                    | -     | Sign                               | 4-71              |

| LEN <sup>(5)</sup>        | WO     | 1C5Ch <sup>(4)</sup>             | -                                    | -     | Length                             | 4-63              |

| <b>AR0</b> <sup>(5)</sup> | WO     | 1C60h <sup>(4)</sup>             | _                                    | -     | Multi-Purpose Address 0            | 4-20              |

| <b>AR1</b> <sup>(5)</sup> | WO     | 1C64h <sup>(4)</sup>             | _                                    | -     | Multi-Purpose Address 1            | 4-21              |

| <b>AR2</b> <sup>(5)</sup> | WO     | 1C68h <sup>(4)</sup>             | -                                    | -     | Multi-Purpose Address 2            | 4-22              |

| <b>AR3</b> <sup>(5)</sup> | WO     | 1C6Ch <sup>(4)</sup>             | -                                    | -     | Multi-Purpose Address 3            | 4-23              |

| <b>AR4</b> <sup>(5)</sup> | WO     | 1C70h <sup>(4)</sup>             | -                                    | -     | Multi-Purpose Address 4            | 4-24              |

| Register Mnemonic Name     | Access | Memory<br>Address <sup>(1)</sup> | I/O<br>Address <sup>(2)</sup> | Index | Description/Comments       | Page |

|----------------------------|--------|----------------------------------|-------------------------------|-------|----------------------------|------|

| AR5 <sup>(5)</sup>         | WO     | 1C74h <sup>(4)</sup>             | -                             | -     | Multi-Purpose Address 5    | 4-25 |

| <b>AR6</b> <sup>(5)</sup>  | WO     | 1C78h <sup>(4)</sup>             | -                             | -     | Multi-Purpose Address 6    | 4-26 |

| -                          | WO     | 1C7Ch <sup>(4)</sup>             | -                             | -     | Reserved                   | -    |

| CXBNDRY <sup>(5)</sup>     | WO     | 1C80h <sup>(4)</sup>             | -                             | -     | Clipper X Boundary         | 4-28 |

| FXBNDRY <sup>(5)</sup>     | WO     | 1C84h <sup>(4)</sup>             | -                             | -     | X Address (Boundary)       | 4-58 |

| YDSTLEN <sup>(5)</sup>     | WO     | 1C88h <sup>(4)</sup>             | -                             | -     | Y Destination and Length   | 4-81 |

| PITCH <sup>(5)</sup>       | WO     | 1C8Ch <sup>(4)</sup>             | -                             | -     | Memory Pitch               | 4-68 |

| YDST <sup>(5)</sup>        | WO     | 1C90h <sup>(4)</sup>             | -                             | -     | Y Address                  | 4-80 |

| YDSTORG <sup>(5)</sup>     | WO     | 1C94h <sup>(4)</sup>             | -                             | -     | Memory Origin              | 4-82 |

| <b>YTOP</b> <sup>(5)</sup> | WO     | 1C98h <sup>(4)</sup>             | -                             | -     | Clipper Y Top Boundary     | 4-83 |

| <b>YBOT</b> <sup>(5)</sup> | WO     | 1C9Ch <sup>(4)</sup>             | -                             | -     | Clipper Y Bottom Boundary  | 4-79 |

| CXLEFT <sup>(5)</sup>      | WO     | 1CA0h <sup>(4)</sup>             | -                             | -     | Clipper X Minimum Boundary | 4-29 |

| CXRIGHT <sup>(5)</sup>     | WO     | 1CA4h <sup>(4)</sup>             | -                             | -     | Clipper X Maximum Boundary | 4-30 |

| FXLEFT <sup>(5)</sup>      | WO     | 1CA8h <sup>(4)</sup>             | -                             | -     | X Address (Left)           | 4-59 |

| FXRIGHT <sup>(5)</sup>     | WO     | 1CACh <sup>(4)</sup>             | -                             | -     | X Address (Right)          | 4-60 |

| XDST <sup>(5)</sup>        | WO     | 1CB0h <sup>(4)</sup>             | -                             | -     | X Destination Address      | 4-76 |

| -                          | 1CB4ł  | n-1CBCh <sup>(4)</sup>           | -                             | -     | Reserved                   | -    |

| DR0                        | WO     | 1CC0h <sup>(4)</sup>             | -                             | -     | Data ALU 0                 | 4-36 |

| -                          | WO     | 1CC4h <sup>(4)</sup>             | -                             | -     | Reserved (DR1)             | -    |

| DR2                        | WO     | 1CC8h <sup>(4)</sup>             | -                             | -     | Data ALU 2                 | 4-37 |

| DR3                        | WO     | 1CCCh <sup>(4)</sup>             | -                             | -     | Data ALU 3                 | 4-38 |

| DR4                        | WO     | 1CD0h <sup>(4)</sup>             | -                             | -     | Data ALU 4                 | 4-39 |

| -                          | WO     | 1CD4h <sup>(4)</sup>             | -                             | -     | Reserved (DR5)             | -    |

| DR6                        | WO     | 1CD8h <sup>(4)</sup>             | -                             | -     | Data ALU 6                 | 4-40 |

| DR7                        | WO     | 1CDCh <sup>(4)</sup>             | -                             | -     | Data ALU 7                 | 4-41 |

| DR8                        | WO     | 1CE0h <sup>(4)</sup>             | -                             | -     | Data ALU 8                 | 4-42 |

|                            | WO     | 1CE4h <sup>(4)</sup>             | -                             | -     | Reserved (DR9)             | _    |

| DR10                       | WO     | 1CE8h <sup>(4)</sup>             | -                             | -     | Data ALU 10                | 4-43 |

| DR11                       | WO     | 1CECh <sup>(4)</sup>             | -                             | -     | Data ALU 11                | 4-44 |

| DR12                       | WO     | 1CF0h <sup>(4)</sup>             | -                             | -     | Data ALU 12                | 4-45 |

| -                          | WO     | 1CF4h <sup>(4)</sup>             | -                             | -     | Reserved (DR13)            | -    |

Table 3-4: Register Map (Part 2 of 9)

| Register Mnemonic Name | Access | Memory<br>Address <sup>(1)</sup> | I/O<br>Address <sup>(2)</sup> | Index | Description/Comments                       | Page                |

|------------------------|--------|----------------------------------|-------------------------------|-------|--------------------------------------------|---------------------|

| DR14                   | WO     | 1CF8h <sup>(4)</sup>             | -                             | -     | Data ALU 14                                | 4-46                |

| DR15                   | WO     | 1CFCh <sup>(4)</sup>             | -                             | -     | Data ALU 15                                | 4-47                |

| -                      | 1D00ł  | n-1DFFh <sup>(4)</sup>           | -                             | -     | Same mapping as 1C00h-1CFCh <sup>(6)</sup> | -                   |

| -                      | 1E00   | h - 1E0Fh                        | -                             | _     | Reserved                                   | -                   |

| FIFOSTATUS             | RO     | 1E10h                            | -                             | -     | Bus FIFO Status                            | 4-57                |

| STATUS                 | RO     | 1E14h                            | -                             | -     | Status                                     | 4-74                |

| ICLEAR                 | WO     | 1E18h                            | -                             | -     | Interrupt Clear                            | 4- <mark>6</mark> 1 |

| IEN                    | R/W    | 1E1Ch                            | -                             | -     | Interrupt Enable                           | 4-62                |

| VCOUNT                 | RO     | 1E20h                            | -                             | -     | Vertical Count                             | 4-75                |

| -                      | 1E24   | h - 1E2Fh                        | -                             | -     | Reserved                                   | -                   |

| DMAMAP30               | R/W    | 1E30h                            | -                             | -     | DMA Map 3h to 0h                           | 4-31                |

| DMAMAP74               | R/W    | 1E34h                            | -                             | -     | DMA Map 7h to 4h                           | 4-32                |

| DMAMAPB8               | R/W    | 1E38h                            | -                             | -     | DMA Map Bh to 8h                           | 4-33                |

| DMAMAPFC               | R/W    | 1E3Ch                            | -                             | -     | DMA Map Fh to Ch                           | 4-34                |

| RST                    | R/W    | 1E40h                            | -                             | -     | Reset                                      | 4-70                |

| -                      | 1E44   | h - 1E53h                        | -                             | -     | Reserved                                   | -                   |

| OPMODE                 | R/W    | 1E54h                            | -                             | -     | Operating Mode                             | 4- <mark>66</mark>  |

| -                      | 1E60   | h - 1E7Fh                        | -                             | -     | Reserved                                   | -                   |

| DWG_INDIR_WT<0>        | WO     | 1E80h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 0          | 4-48                |

| DWG_INDIR_WT<1>        | WO     | 1E84h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 1          | 4-48                |

| DWG_INDIR_WT<2>        | WO     | 1E88h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 2          | 4-48                |

| DWG_INDIR_WT<3>        | WO     | 1E8Ch <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 3          | 4-48                |

| DWG_INDIR_WT<4>        | WO     | 1E90h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 4          | 4-48                |

| DWG_INDIR_WT<5>        | WO     | 1E94h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 5          | 4-48                |

| DWG_INDIR_WT<6>        | WO     | 1E98h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 6          | 4-48                |

| DWG_INDIR_WT<7>        | WO     | 1E9Ch <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 7          | 4-48                |

| DWG_INDIR_WT<8>        | WO     | 1EA0h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 8          | 4-48                |

| DWG_INDIR_WT<9>        | WO     | 1EA4h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 9          | 4-48                |

| DWG_INDIR_WT<10>       | WO     | 1EA8h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 10         | 4-48                |

| DWG_INDIR_WT<11>       | WO     | 1EACh <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 11         | 4-48                |

| DWG_INDIR_WT<12>       | WO     | 1EB0h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 12         | 4-48                |

| DWG_INDIR_WT<13>       | WO     | 1EB4h <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 13         | 4-48                |

| DWG_INDIR_WT<14>       | WO     | 1EB8h <sup>(4)</sup>             | _                             | -     | Drawing Register Indirect Write 14         | 4-48                |

Table 3-4: Register Map (Part 3 of 9)

| Register Mnemonic Name | Access | Memory<br>Address <sup>(1)</sup> | I/O<br>Address <sup>(2)</sup> | Index | Description/Comments               | Page          |

|------------------------|--------|----------------------------------|-------------------------------|-------|------------------------------------|---------------|

| DWG_INDIR_WT<15>       | WO     | 1EBCh <sup>(4)</sup>             | -                             | -     | Drawing Register Indirect Write 15 | 4 <b>-4</b> 8 |

| -                      | 1EC0   | h - 1FBFh                        | -                             | -     | Reserved                           | -             |

| ATTR (Index)           | R/W    | 1FC0h                            | 3C0h                          | -     | Attribute Controller               | 4-86          |

| ATTR (Data)            | WO     | 1FC0h                            | 3C0h                          | -     | Attribute Controller               |               |

| ATTR (Data)            | RO     | 1FC1h                            | 3C1h                          | -     | Attribute Controller               | -             |

| -                      | WO     | 1FC1h                            | 3C1h                          | -     | Reserved                           | -             |

| ATTR0                  | R/W    | -                                | -                             | 00h   | Palette entry 0                    | 4-88          |

| ATTR1                  | R/W    | -                                | -                             | 01h   | Palette entry 1                    | 4-88          |

| ATTR2                  | R/W    | -                                | -                             | 02h   | Palette entry 2                    | 4-88          |

| ATTR3                  | R/W    | -                                | -                             | 03h   | Palette entry 3                    | 4-88          |

| ATTR4                  | R/W    | -                                | -                             | 04h   | Palette entry 4                    | 4-88          |

| ATTR5                  | R/W    | -                                | -                             | 05h   | Palette entry 5                    | 4-88          |

| ATTR6                  | R/W    | -                                | _                             | 06h   | Palette entry 6                    | 4-88          |

| ATTR7                  | R/W    | -                                | -                             | 07h   | Palette entry 7                    | 4-88          |

| ATTR8                  | R/W    | -                                | -                             | 08h   | Palette entry 8                    | 4-88          |

| ATTR9                  | R/W    | -                                | _                             | 09h   | Palette entry 9                    | 4-88          |

| ATTRA                  | R/W    | -                                | -                             | 0Ah   | Palette entry A                    | 4-88          |

| ATTRB                  | R/W    | -                                | -                             | 0Bh   | Palette entry B                    | 4-88          |

| ATTRC                  | R/W    | -                                | _                             | 0Ch   | Palette entry C                    | 4-88          |

| ATTRD                  | R/W    | -                                | _                             | 0Dh   | Palette entry D                    | 4-88          |

| ATTRE                  | R/W    | -                                | -                             | 0Eh   | Palette entry E                    | 4-88          |

| ATTRF                  | R/W    | -                                | -                             | 0Fh   | Palette entry F                    | 4-88          |

| ATTR10                 | R/W    | -                                | -                             | 10h   | Attribute Mode Control             | 4-89          |

| ATTR11                 | R/W    | -                                | -                             | 11h   | Overscan Color                     | 4-91          |

| ATTR12                 | R/W    | -                                | -                             | 12h   | Color Plane Enable                 | 4-92          |

| ATTR13                 | R/W    | -                                | -                             | 13h   | Horizontal Pel Panning             | 4-93          |

| ATTR14                 | R/W    | -                                | -                             | 14h   | Color Select                       | 4-94          |

| -                      | -      | -                                | _                             | 15h - | 1Fh: Reserved                      | -             |

| INSTS0                 | RO     | 1FC2h                            | 3C2h                          | -     | Input Status 0                     | 4-149         |

| MISC                   | WO     | 1FC2h                            | 3C2h                          | -     | Miscellaneous Output               | 4-151         |

| -                      | R/W    | 1FC3h                            | 3C3h <sup>(7)</sup>           | -     | Reserved, not decoded for I/O      |               |

| SEQ (Index)            | R/W    | 1FC4h                            | 3C4h                          | -     | Sequencer                          | 4-153         |

| SEQ (Data)             | R/W    | 1FC5h                            | 3C5h                          | -     | Sequencer                          | -             |

| SEQ0                   | R/W    | -                                | -                             | 00h   | Reset                              | 4-154         |

| SEQ1                   | R/W    | _                                | _                             | 01h   | Clocking Mode                      | 4-155         |

| SEQ2                   | R/W    | -                                | -                             | 02h   | Map Mask                           | 4-156         |

Table 3-4: Register Map (Part 4 of 9)

| Register Mnemonic Name | Access | Memory<br>Address <sup>(1)</sup> | I/O<br>Address <sup>(2)</sup> | Index | Description/Comments                     | Page  |

|------------------------|--------|----------------------------------|-------------------------------|-------|------------------------------------------|-------|

| SEQ3                   | R/W    | -                                | -                             | 03h   | Character Map Select                     | 4-157 |

| SEQ4                   | R/W    | -                                | -                             | 04h   | Memory Mode                              | 4-158 |

| -                      | R/W    | -                                | -                             | 05h - | 07h: Reserved                            | -     |

| -                      | -      | 1FC6h                            | -                             | -     | Reserved                                 | -     |

| DACSTAT                | RO     | 1FC7h                            | 3C7h                          | -     | DAC Status (requires a byte access)      | 4-136 |

| -                      | WO     | 1FC7h                            | -                             | -     | Reserved                                 | -     |

| -                      | 1FC8   | 3h-1FC9h                         | -                             | -     | Reserved                                 | -     |

| FEAT                   | RO     | 1FCAh                            | 3CAh                          | -     | Feature Control                          | 4-137 |

|                        | WO     | 1FCAh                            | 3CAh                          | -     | Reserved                                 | -     |

| -                      | -      | 1FCBh                            | 3CBh <sup>(7)</sup>           | -     | Reserved, not decoded for I/O            | -     |

| MISC                   | RO     | 1FCCh                            | 3CCh                          | -     | Miscellaneous Output                     | 4-151 |

| -                      | WO     | 1FCCh                            | 3CCh                          | -     | Reserved                                 | -     |

| -                      | -      | 1FCDh                            | 3CDh <sup>(7)</sup>           | -     | Reserved, not decoded for I/O            | -     |

| GCTL (Index)           | R/W    | 1FCEh                            | 3CEh                          | -     | Graphic Controller                       | 4-138 |

| GCTL (Data)            | R/W    | 1FCFh                            | 3CFh                          | -     | Graphic Controller                       | -     |

| GCTL0                  | R/W    | -                                | -                             | 00h   | Set/Reset                                | 4-139 |

| GCTL1                  | R/W    | -                                | -                             | 01h   | Enable Set/Reset                         | 4-140 |

| GCTL2                  | R/W    | -                                | -                             | 02h   | Color Compare                            | 4-141 |

| GCTL3                  | R/W    | -                                | -                             | 03h   | Data Rotate                              | 4-142 |

| GCTL4                  | R/W    | -                                | -                             | 04h   | Read Map Select                          | 4-143 |

| GCTL5                  | R/W    | -                                | -                             | 05h   | Graphics Mode                            | 4-144 |

| GCTL6                  | R/W    | _                                | -                             | 06h   | Miscellaneous                            | 4-146 |

| GCTL7                  | R/W    | _                                | -                             | 07h   | Color Don't Care                         | 4-147 |

| GCTL8                  | R/W    | -                                | -                             | 08h   | Bit Mask                                 | 4-148 |

| -                      | -      | -                                | -                             | 09h - | 0Fh: Reserved                            | -     |

| -                      | 1FD(   | )h-1FD3h                         | -                             | -     | Reserved                                 | -     |

| CRTC (Index)           | R/W    | 1FD4h                            | 3D4h                          | -     | CRTC Registers (or 3B4h <sup>(8)</sup> ) | 4-96  |

| CRTC (Data)            | R/W    | 1FD5h                            | 3D5h                          | -     | CRTC Registers (or 3B5h <sup>(8)</sup> ) | -     |

| CRTC0                  | R/W    | -                                | -                             | 00h   | Horizontal Total                         | 4-98  |

| CRTC1                  | R/W    | -                                | _                             | 01h   | Horizontal Display Enable End            | 4-99  |

| CRTC2                  | R/W    | -                                | -                             | 02h   | Start Horizontal Blanking                | 4-100 |

| CRTC3                  | R/W    | -                                | _                             | 03h   | End Horizontal Blanking                  | 4-101 |

| CRTC4                  | R/W    | -                                | -                             | 04h   | Start Horizontal Retrace Pulse           | 4-102 |

| CRTC5                  | R/W    | -                                | _                             | 05h   | End Horizontal Retrace                   | 4-103 |

| CRTC6                  | R/W    | -                                | _                             | 06h   | Vertical Total                           | 4-104 |

| CRTC7                  | R/W    | _                                | _                             | 07h   | Overflow                                 | 4-105 |

Table 3-4: Register Map (Part 5 of 9)

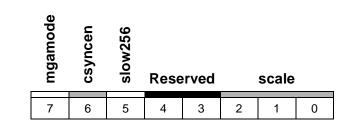

| Register Mnemonic Name | Access | Memory<br>Address <sup>(1)</sup> | I/O<br>Address <sup>(2)</sup> | Index | Description/Comments                                    | Page  |