# **Trademark Acknowledgements**

$MGA, ^{TM}$   $MGA-G200, ^{TM}$   $MGA-1164SG, ^{TM}$   $MGA-2064W, ^{TM}$   $MGA-2164W, ^{TM}$   $MGA-VC064SFB, ^{TM}$  $MGA-VC164SFB, ^{TM}$  MGA  $Marvel, ^{TM}$  MGA  $Millennium, ^{TM}$  MGA  $Mystique, ^{TM}$  MGA Rainbow $Runner, ^{TM}$  MGA  $DynaView, ^{TM}$   $PixelTOUCH, ^{TM}$  MGA Control  $Panel, ^{TM}$  and Instant  $ModeSWITCH, ^{TM}$ are trademarks of Matrox Graphics Inc.

Matrox<sup>®</sup> is a registered trademark of Matrox Electronic Systems Ltd.

VGA,<sup>®</sup> is a registered trademark of International Business Machines Corporation; Micro Channel<sup>TM</sup> is a trademark of International Business Machines Corporation.

Intel<sup>®</sup> is a registered trademark, and  $386, ^{TM}$  486,  $^{TM}$  Pentium,  $^{TM}$  and  $80387^{TM}$  are trademarks of Intel Corporation.

Windows<sup>TM</sup> is a trademark of Microsoft Corporation; Microsoft,<sup>®</sup> and MS-DOS<sup>®</sup> are registered trademarks of Microsoft Corporation.

AutoCAD<sup>®</sup> is a registered trademark of Autodesk Inc.

Unix<sup>TM</sup> is a trademark of AT&T Bell Laboratories.

X-Windows<sup>TM</sup> is a trademark of the Massachusetts Institute of Technology.

AMD<sup>TM</sup> is a trademark of Advanced Micro Devices. Atmel<sup>®</sup> is a registered trademark of Atmel Corporation. Catalyst<sup>TM</sup> is a trademark of Catalyst Semiconductor Inc. SGS<sup>TM</sup> is a trademark of SGS-Thompson. Toshiba<sup>TM</sup> is a trademark of Toshiba Corporation. Texas Instruments<sup>TM</sup> is a trademark of Texas Instruments. National<sup>TM</sup> is a trademark of National Semiconductor Corporation. Microchip<sup>TM</sup> is a trademark of Microchip Technology Inc.

All other nationally and internationally recognized trademarks and tradenames are hereby acknowledged.

# This document contains confidential proprietary information that may not be disclosed without written permission from Matrox Graphics Inc.

© Copyright Matrox Graphics Inc., 1997. All rights reserved.

Disclaimer: Matrox Graphics Inc. reserves the right to make changes to specifications at any time and without notice. The information provided by this document is believed to be accurate and reliable. However, no responsibility is assumed by Matrox Graphics Inc. for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Matrox Graphics Inc. or Matrox Electronic Systems Ltd.

# **Chapter 1: MGA Overview**

| 1.1    | Introduction                        |

|--------|-------------------------------------|

| 1.2    | System Block Diagram                |

| 1.3    | Application Areas                   |

| 1.4    | Target Markets                      |

| 1.5    | Block Diagram                       |

| 1.6    | Features                            |

|        | 1.6.1 PCI / AGP Bus Controller 1-7  |

|        | 1.6.2 Triangle Setup Engine         |

|        | 1.6.3 3D and Texture Mapping Engine |

|        | 1.6.4 2D Engine                     |

|        | 1.6.5 VGA Engine                    |

|        | 1.6.6 Video Engine                  |

|        | 1.6.7 Display Engine                |

|        | 1.6.8 Memory Controller             |

|        | 1.6.9 Other Features                |

| 1.7    | Typographical Conventions Used      |

| 1.8    | Locating Information                |

| Chapte | er 2: Resource Mapping              |

| 2.1    | Memory Mapping                      |

|        | 2.1.1 Configuration Space Mapping   |

|        | 2.1.2 MGA General Map               |

|        | 2.1.3 MGA Control Aperture          |

| 2.2    | Register Mapping                    |

# **Chapter 3: Register Descriptions**

| 3.1 | Power Graphic Mode Register Descriptions               | 3-2 |

|-----|--------------------------------------------------------|-----|

|     | 3.1.1 Power Graphic Mode Configuration Space Registers | 3-2 |

|     | 3.1.2 Power Graphic Mode Memory Space Registers        | -28 |

| 3.2 | VGA Mode Register Descriptions                         | 225 |

|     | 3.2.1 VGA Mode Register Descriptions                   | 225 |

| 3.3 | DAC Registers                                          | 303 |

|     | 3.3.1 DAC Register Descriptions                        | 303 |

# **Chapter 4: Programmer's Specification**

| 4.1 | HOST  | Interface          | -2 |

|-----|-------|--------------------|----|

|     | 4.1.1 | Introduction       | -2 |

|     | 4.1.2 | PCI Retry Handling | -3 |

|     | 4.1.3 | PCI Burst Support  | -3 |

| 4.1.4 PCI Target-Abort Generation                                |            |

|------------------------------------------------------------------|------------|

| 4.1.5 Transaction Ordering                                       |            |

| 4.1.6 Direct Access Read Cache                                   | 4-5        |

| 4.1.7 Big-Endian Support                                         |            |

| 4.1.8 Host Pixel Format                                          |            |

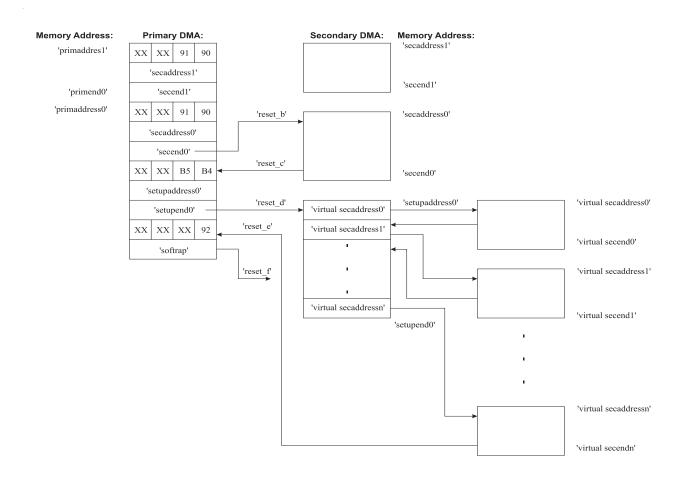

| 4.1.9 Programming Bus Mastering for DMA Transfers                |            |

| 4.2 Memory Interface                                             | 4-18       |

| 4.2.1 Frame Buffer Organization                                  |            |

| 4.2.2 Pixel Format                                               |            |

| 4.3 Chip Configuration and Initialization                        | 4-23       |

| 4.3.1 Reset                                                      |            |

| 4.3.2 Operations After Hard Reset                                |            |

| 4.3.3 Power Up Sequence                                          |            |

| 4.4 Direct Frame Buffer Access                                   | 4-28       |

| 4.5 Drawing in Power Graphic Mode                                | 4-29       |

| 4.5.1 Drawing Register Initialization Using General Purpose Pseu | do-DMA4-29 |

| 4.5.2 Overview                                                   |            |

| 4.5.3 Global Initialization (All Operations)                     |            |

| 4.5.4 Line Programming                                           |            |

| 4.5.5 Trapezoid / Rectangle Fill Programming                     |            |

| 4.5.6 Bitblt Programming                                         |            |

| 4.5.7 ILOAD Programming                                          |            |

| 4.5.8 Loading the Texture Color Palette                          |            |

| 4.6 CRTC Programming                                             | 4-61       |

| 4.6.1 Horizontal Timing                                          |            |

| 4.6.2 Vertical Timing                                            |            |

| 4.6.3 Memory Address Counter                                     |            |

| 4.6.4 Programming in VGA Mode                                    |            |

| 4.6.5 Programming in Power Graphic Mode                          | 4-65       |

| 4.7 Video Interface                                              | 4-70       |

| 4.7.1 Operation Modes                                            |            |

| 4.7.2 Palette RAM (LUT)                                          |            |

| 4.7.3 Hardware Cursor                                            |            |

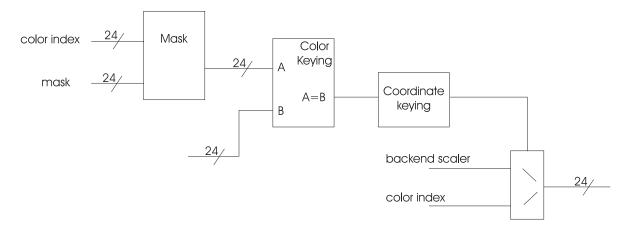

| 4.7.4 Keying Functions                                           |            |

| 4.7.5 Zooming                                                    |            |

| 4.7.6 Feature Connector                                          |            |

| 4.7.7 Test Functions                                             |            |

| 4.7.8 PLL Clock Generators                                       |            |

| 4.8 Video Input Interface                                        | 4-81       |

| 4.8.1 Overview of the Video-Grabber                              |            |

| 4.8.2 MAFC Mode Selection.                                       |            |

| 4.8.3 Programming sequence 4-81              |

|----------------------------------------------|

| 4.9 CODEC Interface                          |

| 4.9.1 Memory Organization 4-83               |

| 4.9.2 Command Execution                      |

| 4.9.3 Output mode                            |

| 4.9.4 Codec Interface IDLE State 4-89        |

| 4.9.5 Recovery Width Programming 4-89        |

| 4.9.6 Miscellaneous Control Programming 4-89 |

| 4.9.7 Compressing data 4-90                  |

| 4.9.8 Decompressing data 4-93                |

| 4.9.9 Error Recovery 4-95                    |

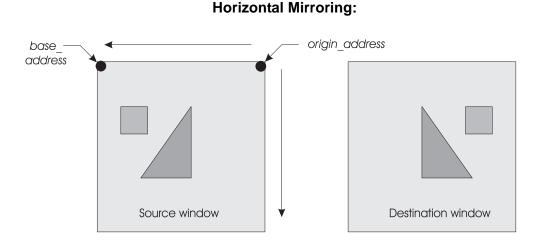

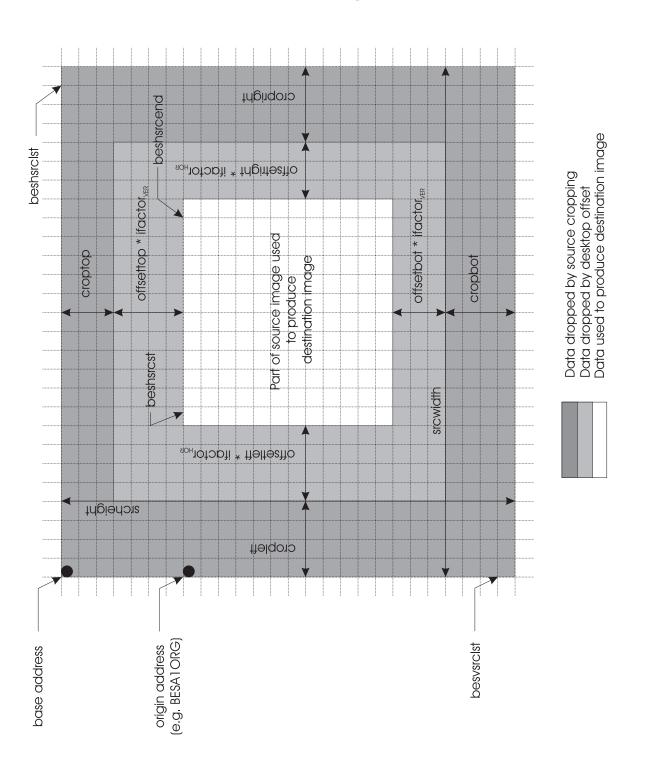

| 4.10 Backend Scaler                          |

| 4.10.1 Introduction                          |

| 4.10.2 Horizontal Scaling 4-99               |

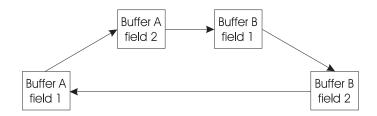

| 4.10.3 Vertical Scaling 4-102                |

| 4.10.4 Keying                                |

| 4.10.5 Miscellaneous Functions 4-110         |

| 4.10.6 BES Parameter Example: 4-112          |

| 4.11 Interrupt Programming 4-113             |

| 4.12 Power Saving Features 4-116             |

| 4.12.1 Entering Power Saving Mode 4-116      |

| 4.12.2 Coming Out of Power Saving Mode 4-117 |

| 4.13 Accessing the Serial EEPROM 4-118       |

|                                              |

# **Chapter 5: Hardware Designer's Notes**

| 5.1 Introduction                           |

|--------------------------------------------|

| 5.2 Host Interface                         |

| 5.2.1 PCI Interface                        |

| 5.2.2 AGP Interface                        |

| 5.3 Snooping                               |

| 5.4 EEPROM Devices                         |

| 5.5 Memory Interface                       |

| 5.5.1 SGRAM Configurations                 |

| 5.6 Video interface                        |

| 5.6.1 Slaving the MGA-G200 5-12            |

| 5.6.2 Genlock Mode 5-12                    |

| 5.6.3 Crystal Resonator Specification 5-13 |

|                                            |

# **Appendix A: Technical Information**

| A.1 | Pin List                 | <u>\-2</u> |

|-----|--------------------------|------------|

|     | A.1.1 Host (PCI / AGP) A | ۰-3        |

| A.1.2 Host (Local Mode)                       | A-4  |

|-----------------------------------------------|------|

| A.1.3 Memory Interface                        | A-4  |

| A.1.4 Video Display Interface                 | A-4  |

| A.1.5 Video In Interface                      | A-4  |

| A.1.6 Video Out Interface                     | A-4  |

| A.1.7 CODEC Interface                         | A-5  |

| A.1.8 SEEPROM                                 | A-5  |

| A.1.9 Analog Signals                          | A-5  |

| A.1.10 Miscellaneous Functions                | A-6  |

| A.1.11 TEST                                   | A-6  |

| A.1.12 AGP VDD/GND                            |      |

| A.1.13 PCI VDD/GND                            |      |

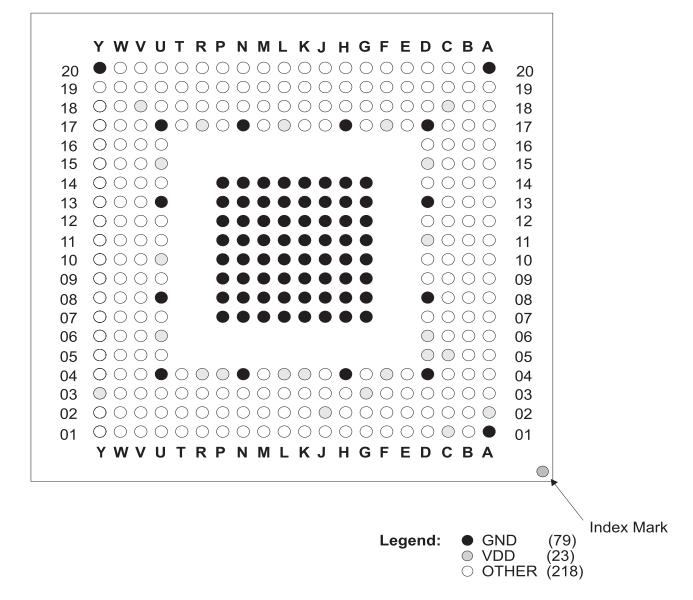

| A.2 PCI Pinout Illustration and Table         |      |

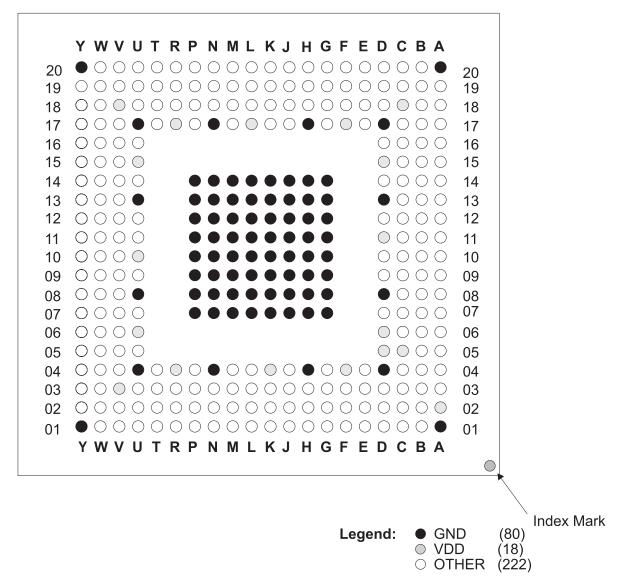

| A.3 AGP Pinout Illustration and Table.        | A-9  |

| A.4 Electrical Specification                  | A-11 |

| A.4.1 DC Specifications                       | A-11 |

| A.4.2 AC Specifications                       | A-20 |

| A.5 Mechanical Specification                  |      |

| A.6 Test Feature                              | A-43 |

| A.6.1 Nand Tree Order (for MGA-G200-AGP only) | A-44 |

| A.6.2 Nand Tree Order (for MGA-G200-PCI only) | A-46 |

| A.7 Ordering Information                      | A-48 |

| Appendix B: Changes                           |      |

# B.1 Changes in the Document Since Revision 0300 B-2 A.1.1 Chip Revision Notes and Changes B-2 B.2 Changes in the Document B-2 A.2.1 Chip revision Notes and Changes B-2 B.2 Changes in the Document B-2 A.2.1 Chip revision Notes and Changes B-2

#### **Chapter 1: MGA Overview**

| Figure 1-1: System Block Diagram   | . 1-3 |

|------------------------------------|-------|

| Figure 1-2: MGA-G200 Block Diagram | . 1-6 |

#### **Chapter 2: Resource Mapping**

Not Applicable

#### **Chapter 3: Register Descriptions**

Not Applicable

#### **Chapter 4: Programmer's Specification**

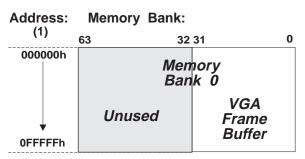

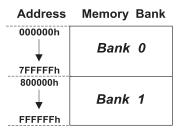

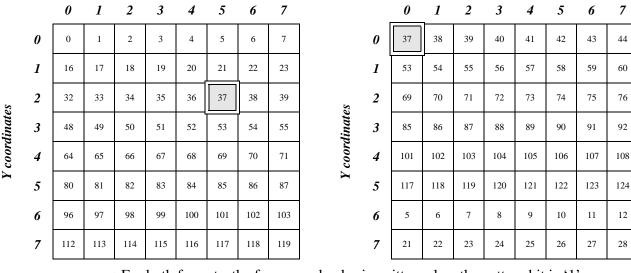

| Figure 4-1: OPTION<12:10> memconfig [2:0] = '000'          | 4-19         |

|------------------------------------------------------------|--------------|

| Figure 4-2: OPTION<2:0> memconfig [2:0] = '001'            | 4-19         |

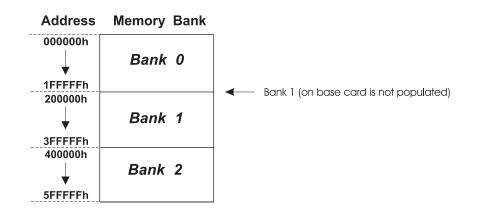

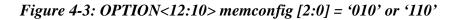

| Figure 4-3: OPTION<12:10> memconfig [2:0] = '010' or '110' | 4-20         |

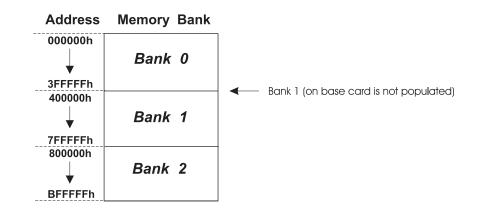

| Figure 4-4: OPTION<2:0> memconfig [2:0] = '011' or '111'   | 4-20         |

| Figure 4-5: OPTION<2:0> memconfig [2:0] = '100' or '101'   | 4-20         |

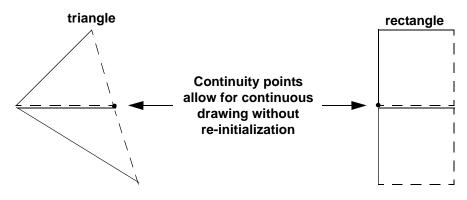

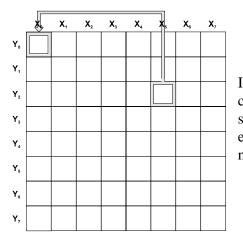

| Figure 4-6: Drawing Multiple Primitives                    | 4-38         |

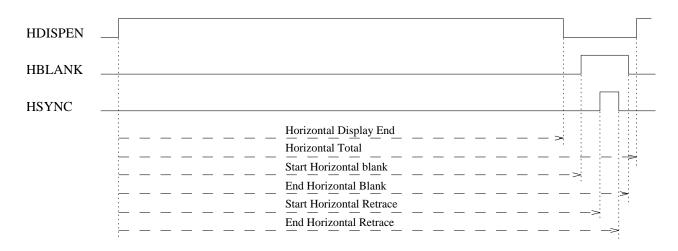

| Figure 4-7: CRTC Horizontal Timing                         | 4-61         |

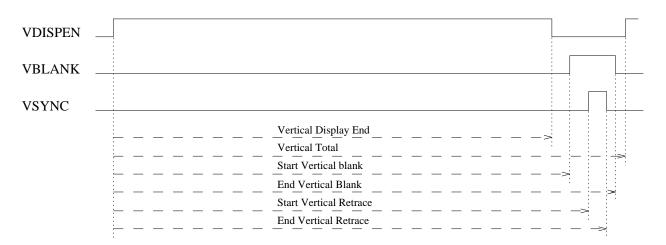

| Figure 4-8: CRTC Vertical Timing                           | 4-62         |

| Figure 4-9: Video Timing in Interlace Mode                 | <b>4-6</b> 9 |

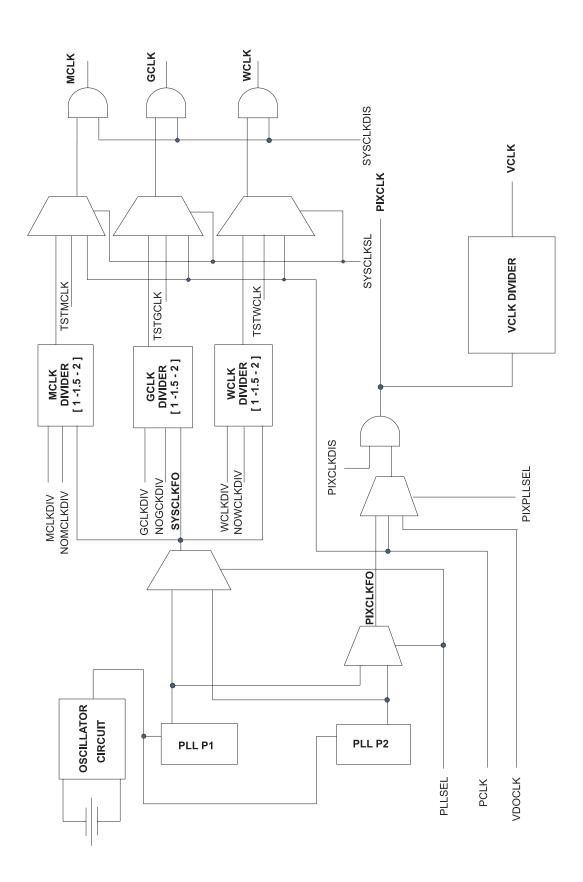

| Figure 4-10: Clock Division Scheme                         | 4-76         |

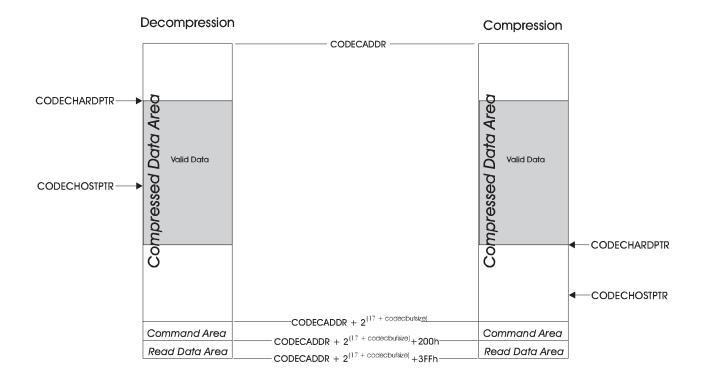

| Figure 4-11: CODEC Interface Organization                  | <b>4-84</b>  |

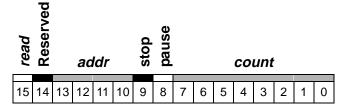

| Figure 4-12: CODEC Command Format                          | 4-85         |

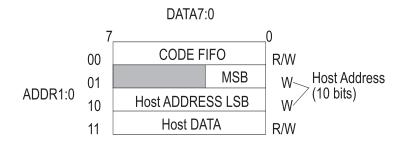

| Figure 4-13: Address Space of I33 CODEC in Code Slave Mode | 4-86         |

| Figure 4-14: Compression of a Live Video Source            | 4-90         |

| Figure 4-15: Decompressing Data from the Memory            | 4-93         |

#### **Chapter 5: Hardware Designer's Notes**

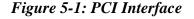

| Figure 5-1: PCI Interface                                               | 5-2         |

|-------------------------------------------------------------------------|-------------|

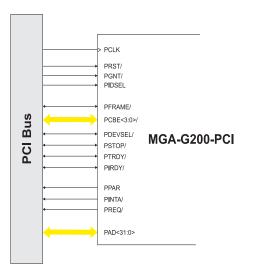

| Figure 5-2: AGP Interface                                               | 5-3         |

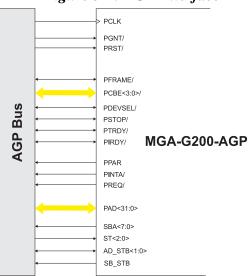

| Figure 5-3: External Device Configuration 5                             | 5-4         |

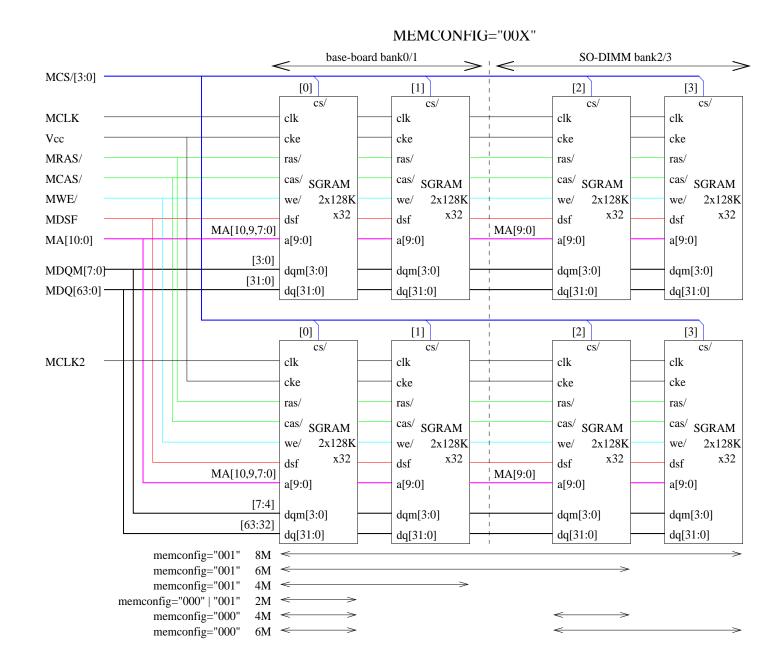

| Figure 5-4: Memory Interface Connection (memconfig = '00X')             | 5 <b>-8</b> |

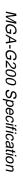

| Figure 5-5: Memory Interface Connection (memconfig = '01X')             | 5-9         |

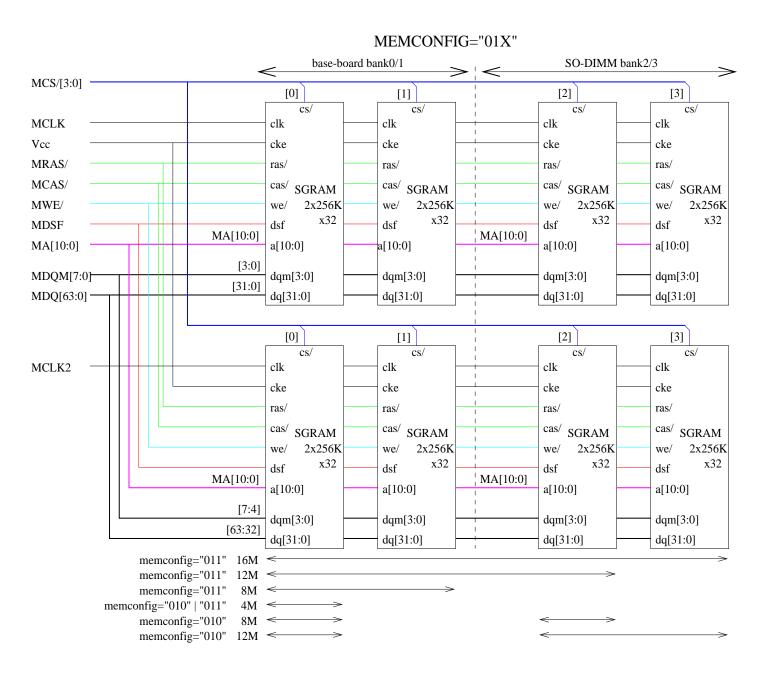

| Figure 5-6: Memory Interface Connection (memconfig = '10X')             | -10         |

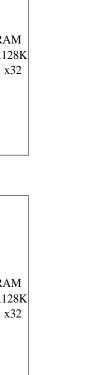

| Figure 5-7: Memory Interface Connection (memconfig = '11X')             | -11         |

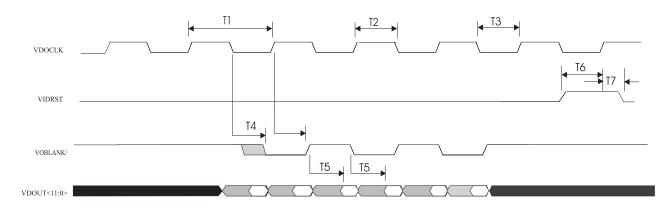

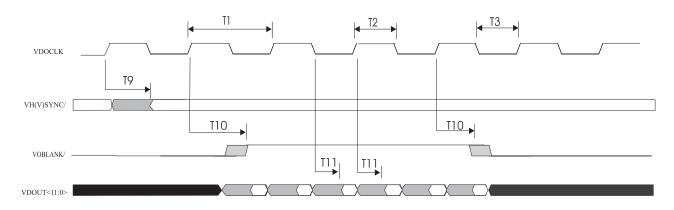

| Figure 5-8: VIDRST, Internal Horizontal/Vertical Active, and VOBLANKN5- | ·12         |

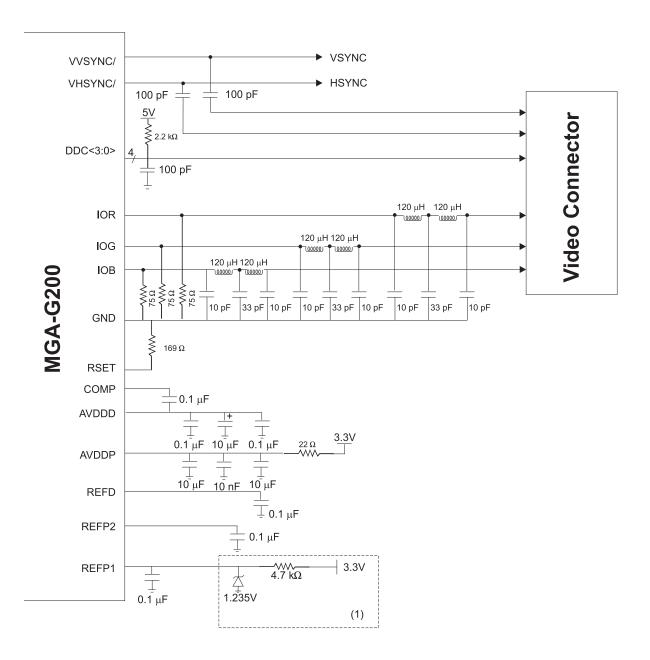

| Figure 5-9: Video Interface                                             | -14         |

| Figure 5-10: Video Connector                                            | ·15         |

# Chapter A: Technical Information

| Figure A-1: PCI Pinout Illustration                           | A-7  |

|---------------------------------------------------------------|------|

| Figure A-2: AGP Pinout Illustration                           | A-9  |

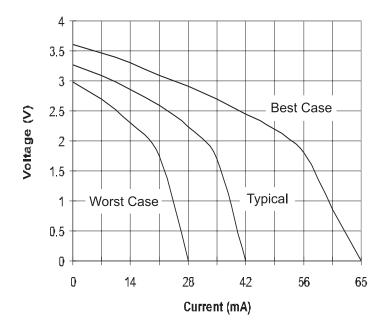

| Figure A-3: SSTL Buffer I/V Curve Pull-Up (Class 1)           | A-14 |

| Figure A-4: SSTL Buffer I/V Curve Pull-Up (Class 2)           | A-14 |

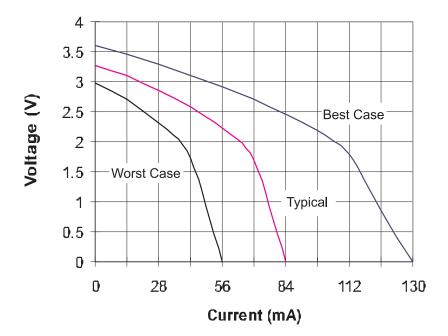

| Figure A-5: SSTL Buffer I/V Curve Pull-Down (Class 1)         | A-15 |

| Figure A-6: SSTL Buffer I/V Curve Pull-Down (Class 2)         | A-15 |

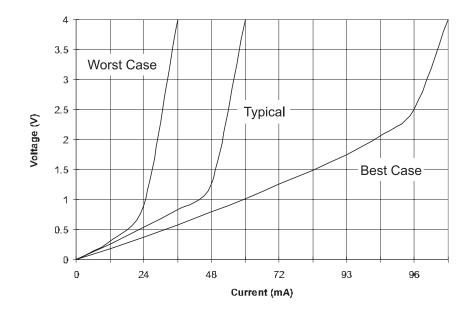

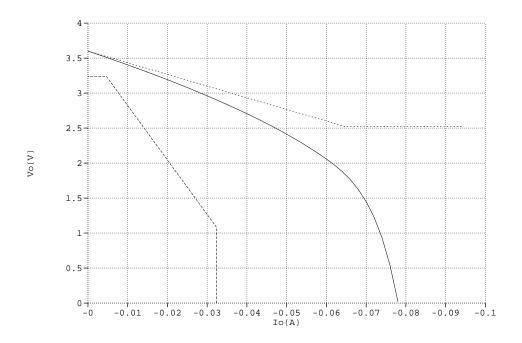

| Figure A-7: V/I Curves for AGP Buffers (Best Case)            | A-16 |

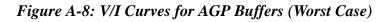

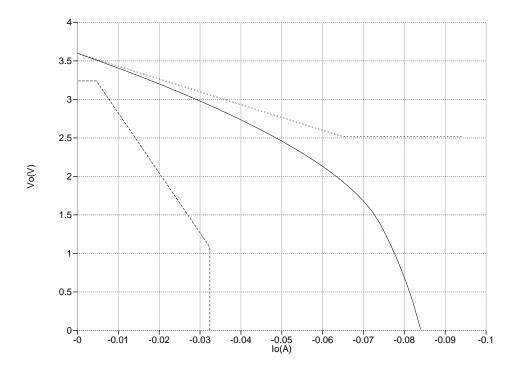

| Figure A-8: V/I Curves for AGP Buffers (Worst Case)           | A-16 |

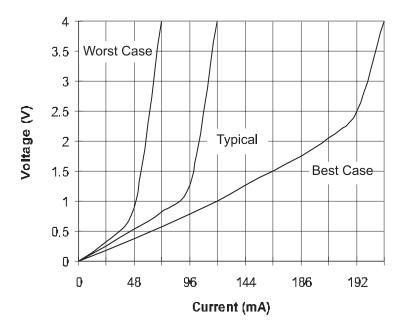

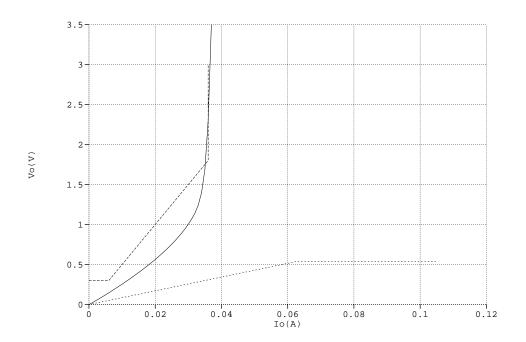

| Figure A-9: VV/I Curves for AGP Buffers (Typical Case)        | A-17 |

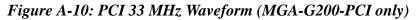

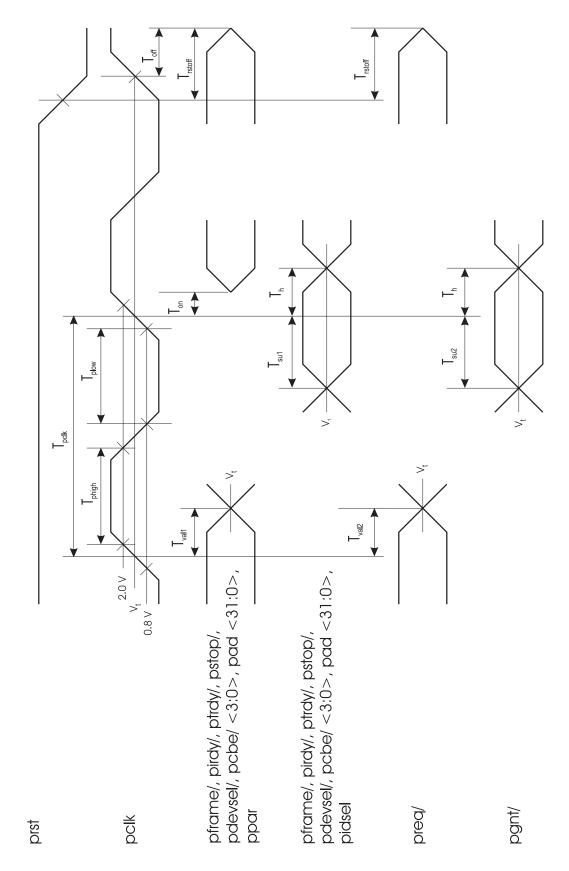

| Figure A-10: PCI 33 MHz Waveform (MGA-G200-PCI only)          | A-21 |

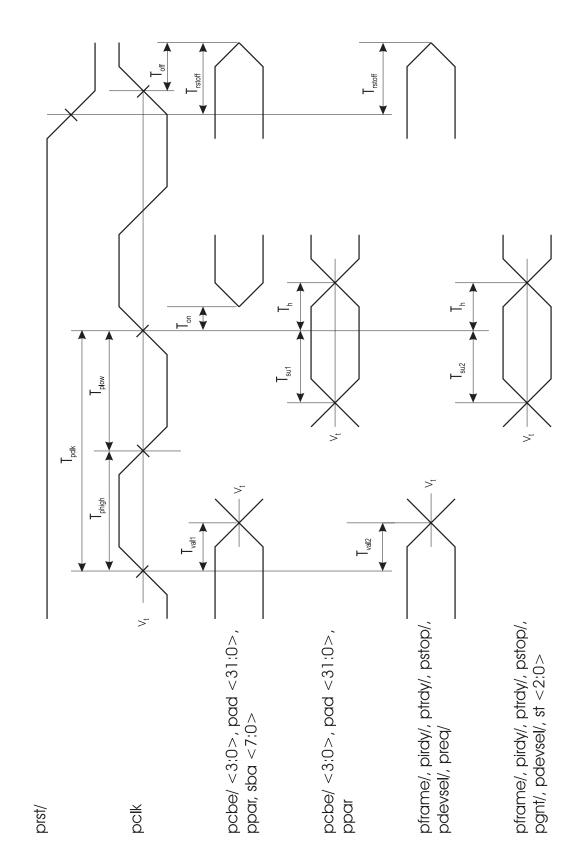

| Figure A-11: AGP 1X Timing (MGA-G200-AGP only)                | A-23 |

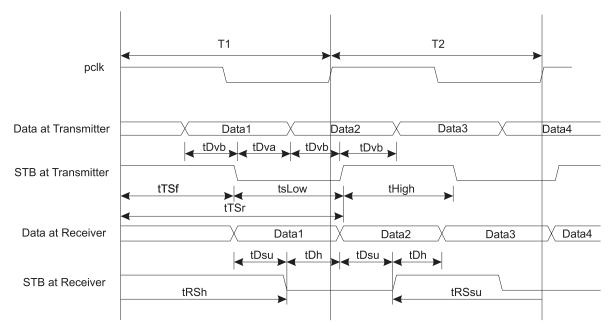

| Figure A-12: AGP 2X Timing Diagram                            | A-24 |

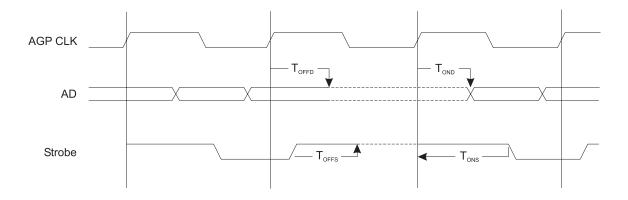

| Figure A-13: AGP 2X Strobe/Data Turnaround Timing Diagram     | A-25 |

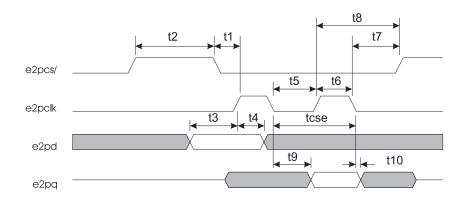

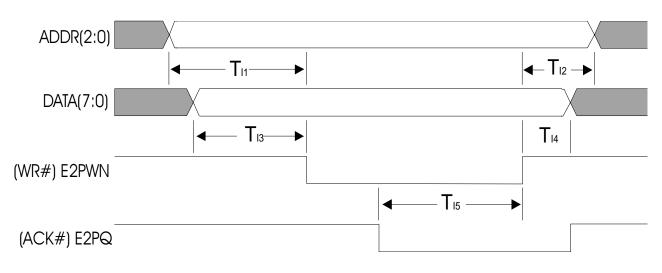

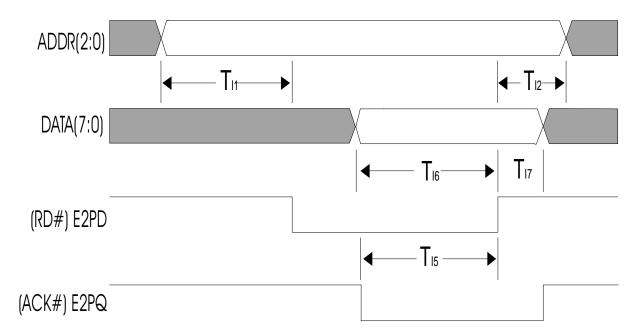

| Figure A-14: Serial EEPROM Waveform                           | A-26 |

| Figure A-15: MAFC Waveform                                    | A-27 |

| Figure A-16: Panel Link Mode                                  | A-27 |

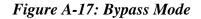

| Figure A-17: Bypass Mode                                      | A-28 |

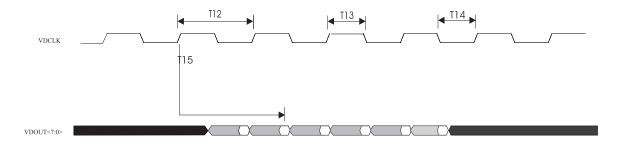

| Figure A-18: Memory Interface Waveform                        | A-28 |

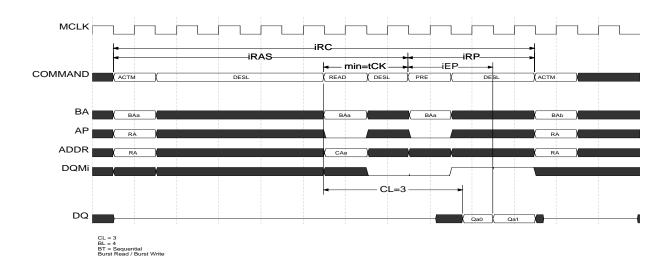

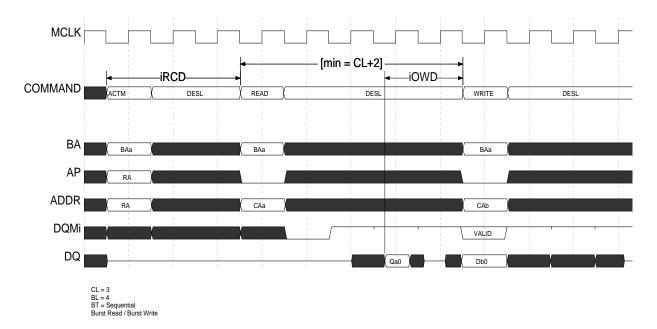

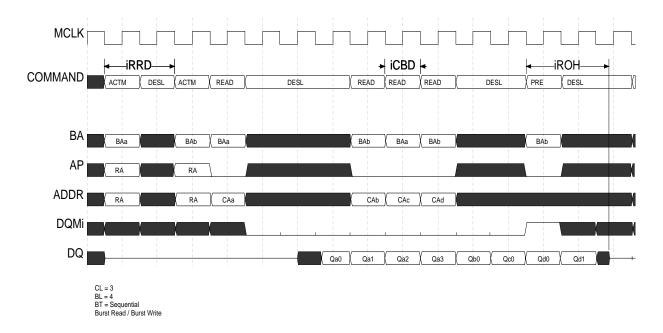

| Figure A-19: Read Followed by Precharge (Tcl=3)               | A-29 |

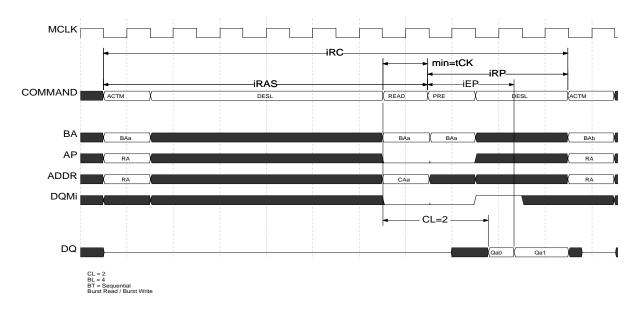

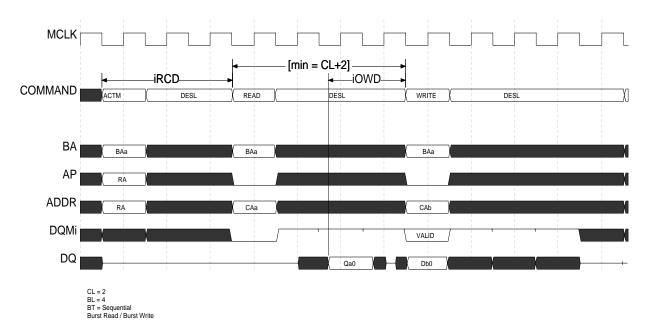

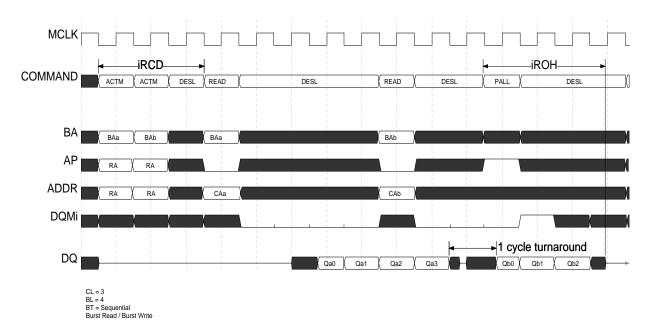

| Figure A-20: Read Followed by a Precharge (Tcl = 2)           | A-30 |

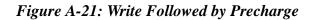

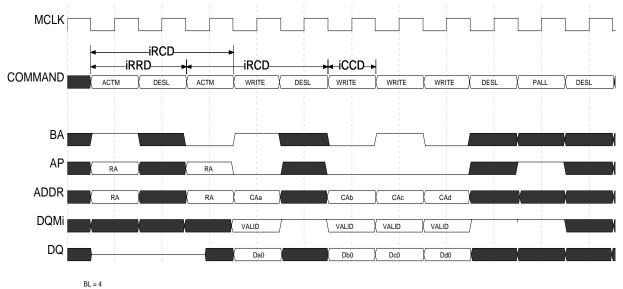

| Figure A-21: Write Followed by Precharge                      | A-30 |

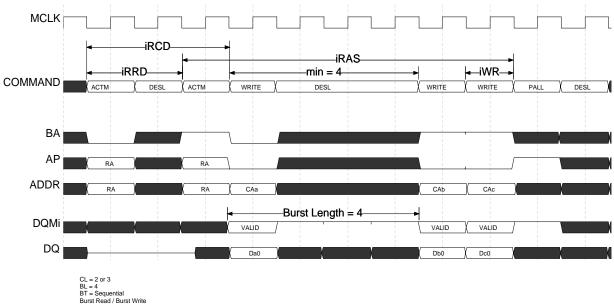

| Figure A-22: Read Followed by Write (Tcl =3)                  | A-31 |

| Figure A-23: Read Followed by Write (Tcl =2)                  | A-31 |

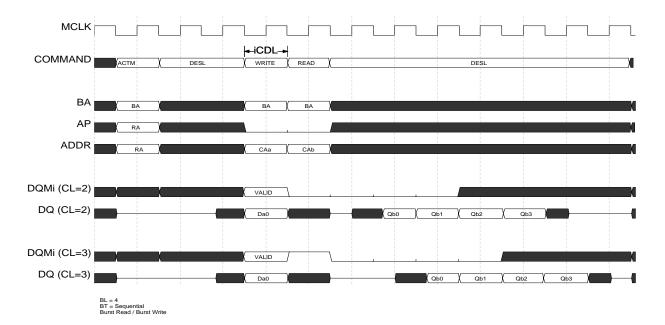

| Figure A-24: Write Followed by Read (same chip select)        | A-32 |

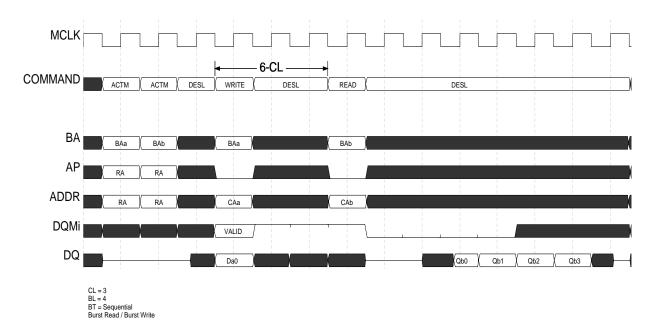

| Figure A-25: Write Followed by Read (different chip select)   | A-32 |

| Figure A-26: Read to Both Banks(same chip select)             | A-33 |

| Figure A-27: Read to Different Banks (different chip select)  | A-33 |

| Figure A-28: Write to Both Banks(same chip select)            | A-34 |

| Figure A-29: Write to Different Banks (different chip select) | A-34 |

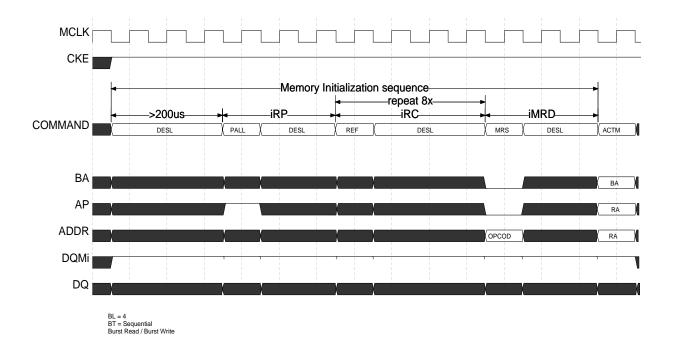

| Figure A-30: Power-On Sequence                                | A-35 |

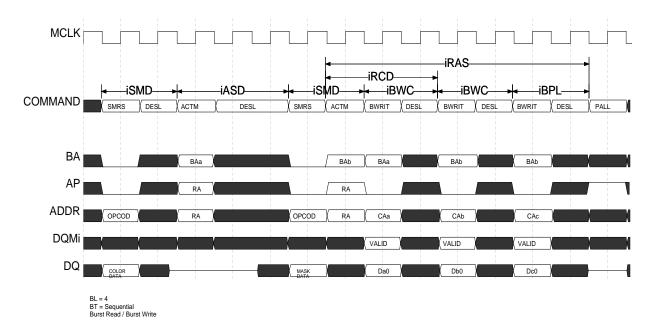

| Figure A-31: Block Write and Special Mode Register command    | A-35 |

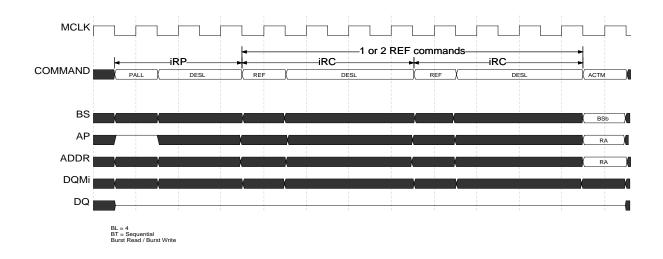

| Figure A-32: Memory Refresh Sequence                          | A-36 |

| Figure A-33: I33 Mode, Writes                                 | A-37 |

| Figure A-34: I33 Mode, Reads                                  | A-37 |

| Figure A-35: VMI Mode A Writes                                | A-38 |

| Figure A-36: VMI Mode A, Reads.                               | A-38 |

| Figure A-37: VMI Mode B, Writes          | A-39 |

|------------------------------------------|------|

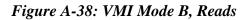

| Figure A-38: VMI Mode B, Reads           | A-39 |

| Figure A-39: Video In Timings            | A-41 |

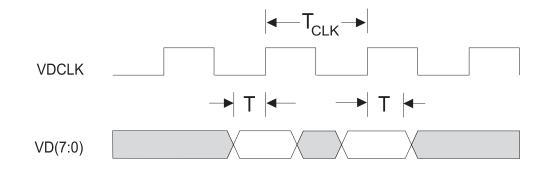

| Figure A-40: MGA-G200 Mechanical Drawing | A-42 |

# Chapter B: Changes

Not Applicable

#### **Chapter 1: MGA Overview**

#### Chapter 2: Resource Mapping

| Table 2-1: MGA-G200 Configuration Space Mapping          | . 2-2 |

|----------------------------------------------------------|-------|

| Table 2-2: MGA General Map                               | . 2-3 |

| Table 2-3: MGA Control Aperture (extension of Table 3-2) | . 2-4 |

| Table 2-4: Register Map.                                 | . 2-5 |

#### **Chapter 3: Register Descriptions**

Not Applicable

#### **Chapter 4: Programmer's Specification**

| Table 4-1: Display Modes.         4-25                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4-2: ILOAD Source Size         4-56                                                                                                                                         |

| Table 4-3: ILOAD Supported Formats    4-58                                                                                                                                        |

| Table 4-4: Bitblt with Expansion Supported Formats    4-59                                                                                                                        |

| Table 4-5: MAFC Video Output Port Pins    4-73                                                                                                                                    |

| Table 4-6: Contents of the Command Area    4-88                                                                                                                                   |

| Table 4-7: Contents of the Read Data Area                                                                                                                                         |

| Table 4-8: Supported Functionality for each Interrupt Source         4-115                                                                                                        |

|                                                                                                                                                                                   |

| Chapter 5: Hardware Designer's Notes                                                                                                                                              |

| Chapter 5: Hardware Designer's Notes Table 5-1: Supported SGRAM/SDRAM Commands                                                                                                    |

|                                                                                                                                                                                   |

| Table 5-1: Supported SGRAM/SDRAM Commands5-5Table 5-2: 10-Bit Address Configuration                                                                                               |

| Table 5-1: Supported SGRAM/SDRAM Commands5-5Table 5-2: 10-Bit Address Configuration<br>(memconfig <2:0>= 00x for 2-bank 8Mb(x32) device5-6Table 5-3: 11-Bit Address Configuration |

| Table 5-5: 11-Bit Address Configuration           |  |

|---------------------------------------------------|--|

| (memconfig<2:0>=11x) for 4-bank, 16Mb(x32) device |  |

# **Chapter A: Technical Information**

| Table A-1: Pin Count Summary MGA-G200-PCI       A       | 4-2 |

|---------------------------------------------------------|-----|

| Table A-2: Pin Count Summary MGA-G200-AGP               | 4-2 |

| Table A-3: PCI Pinout Legend (Bottom View)              | 4-8 |

| Table A-4: AGP Pinout Legend (Bottom View)              | -10 |

| Table A-5: Absolute Maximum Rating A                    | -11 |

| Table A-6: Recommended Operating Conditions.         A- | -12 |

| Table A-7: DC Characteristics                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------|

| (VDD3 = 3.3 ±0.3V, VDD5 = 5.0 ±0.25V, TA = 0 to 55°)(PCI)<br>(VDD3 = 3.3 ±0.15V, VDD5 = 5.0 ±0.25V, TA = 0 to 55°)(AGP)A-13 |

| Table A-8: PCI Buffer Type and Pin Load         A-18                                                                        |

|                                                                                                                             |

| Table A-9: AGP Buffer Type and Pin Load    A-19                                                                             |

| Table A-10: DAC    Parameter List    A-20                                                                                   |

| Table A-11: PLL Parameter List    A-20                                                                                      |

| Table A-12: PCI 33 MHz 5V Signaling Environment Timing (MGA-G200-PCI only)A-22                                              |

| Table A-13: AGP 1X Timing (MGA-G200-AGP only)    A-24                                                                       |

| Table A-14: AGP 2X Timing (MGA-G200-AGP only)    A-25                                                                       |

| Table A-15: Serial EEPROM Clock Period Cycle    A-26                                                                        |

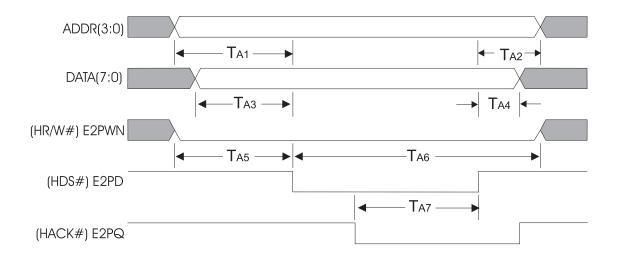

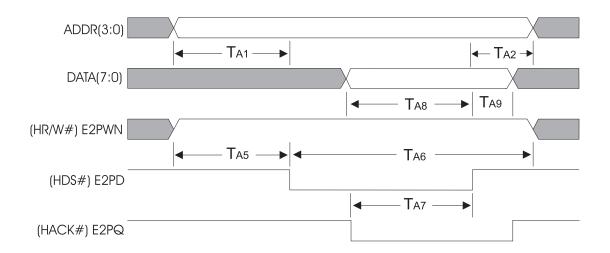

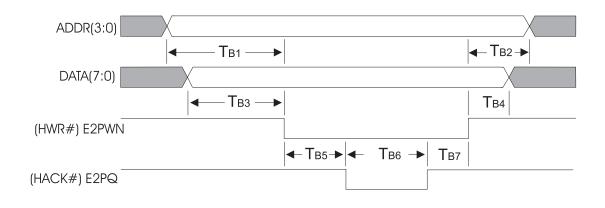

| Table A-16: Serial EEPROM Parameter List    A-27                                                                            |

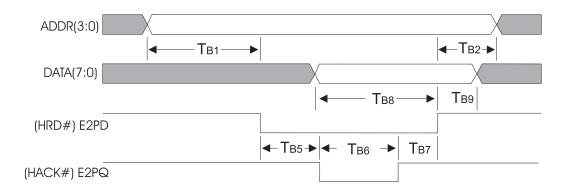

| Table A-17: MAFC Waveforms data information.    A-28                                                                        |

| Table A-18: Memory Interface Parameter List    A-29                                                                         |

| Table A-19: MGA-G200 Sync. RAM Clock-Based Parameter TableA-36                                                              |

| Table A-20: Codec Parameters.    A-40                                                                                       |

| Table A-21: Video In Parametrs    A-41                                                                                      |

| Table A-22: AGP Nand Tree Order    A-44                                                                                     |

| Table A-23: PCI Nand Tree Order.    A-46                                                                                    |

# Chapter B: Changes

Not Applicable

# Chapter 1: MGA Overview

| Introduction                   | 1-2  |

|--------------------------------|------|

| System Block Diagram           | 1-3  |

| Application Areas              | 1-4  |

| Target Markets                 | 1-4  |

| Block Diagram                  | 1-5  |

| Features                       | 1-7  |

| Typographical Conventions Used | 1-10 |

| Locating Information           | 1-10 |

#### 1.1 Introduction

The Matrox MGA-G200 which is compatible with the MGA-G100 product but with a significant improvement in performance:

- Supports full AGP features

- Includes high performance triangle setup engine

- Accelerates 3D texture mapped consumer applications such as PC games with the Enhanced Matrox Fast Texture Architecture

- Improves 2-D performance

- Provides superior Windows performance

- Is fully Microsoft DirectDraw, Direct 3D, and Open GL compliant

- Has fast VGA acceleration

- Accelerates digital video features

- Includes integrated frontend and backend scaler

- Includes digital video input port and video output port

- Includes hardware CODEC interface port

- Includes an integrated DAC

- Connects to SSTL or LVTTL SGRAM

The Matrox MGA-G200 has special features specifically designed to provide superior 3D performance in a 4 MByte frame buffer. The Matrox MGA-G200 is intended to provide a complete solution for home PC users who are interested in top performance Windows 95 and DOS 3D game and multimedia applications, but who are also interested in leveraging their home PC as a home office and education centre. It is also suitable for environments such as Windows NT, IBM OS/2 PM, Unix X-Windows, AutoCAD, and more.

The MGA-G200 series has an improved 3D acceleration core over the Matrox MGA-G100, key video capabilities of the MGA-VC064FB video engine and a significantly faster frame buffer interface fo applications requiring a high display bandwidth. It controls up to 16 megabytes of SGRAM.

The integrated DAC in the MGA-G200 eliminates the need for an external DAC. This substantially lowers the cost and space required for the graphics sub-system.

The MGA-G200A is optimized to exploit the AGP bus features and bandwidth. Alternatively, the PCI version or MGA-G200P also provides superior performance in a PCI-based system. In order to optimize performance, both DMA model and execute model are supported. The bus controller uses bus-mastering techniques to fetch command lists from PCI or AGP space, load textures into the texture cache or into the frame buffer, and to blit data between system memory and the frame buffer. The AGP transfers are performed in 2X mode, with sideband signalling and command pipelining to further parallelize and accelerate operations. The graphic engine has been designed to accept the longer latency periods that occur when accessing the system bus. This enables the application to store information, such as texture, in the system memory without any loss in performance.

A fully programmable setup engine increases 3D performance and off-loads the CPU for other tasks. Combined with a new bus controller, it can directly interpret triangle list information. Its instruction cache enables transparent transition between multiple micro-code programs. Multiple pipelined ALUs operate in parallel on floating point or integer data giving the MGA-G200 high performance and versatility.

A full-featured 3D rendering engine, the Enhanced Matrox Fast Texture Architecture, is the centerpiece of the MGA-G200. This 3D engine is an advanced renderer with full perspective correct texture mapping, lighting, Gouraud shading, specular lighting, fogging, stipple and true alpha blending, optional 16-bit or 32 bit Z-buffering, capable of bus mastering and keying on texture color or texel alpha key bit. Combined with the video engine, the 3D engine has the ability to use video as a source for texturing. The Matrox

texture compression model saves on memory usage, allowing low cost and high performance even within a frame buffer as small as 2MBytes.

The MGA-G200 core engine fully implements the Matrox Video Architecture with its integrated digital video scaling, filtering and color space conversion engine. This architecture supports both shared frame buffer and split frame buffer (overlay) modes of operation to provide maximum flexibility in combining video with graphics. This architecture supports video sprites, video texture maps, graphics overlay, and many other methods of combining video with graphics. The MGA-G200 can be upgraded with the Matrox Video Encoder (Maven) which provides high quality output to a TV or VCR.

This specification covers two chips: the MGA-G200P that connects to a PCI bus and MGA-G200A to an AGP bus. The specification applies the term MGA-G200 to both chips. For PCI specific information, the term MGA-G200P will apply, while the term MGA-G200A will apply to AGP specific information.

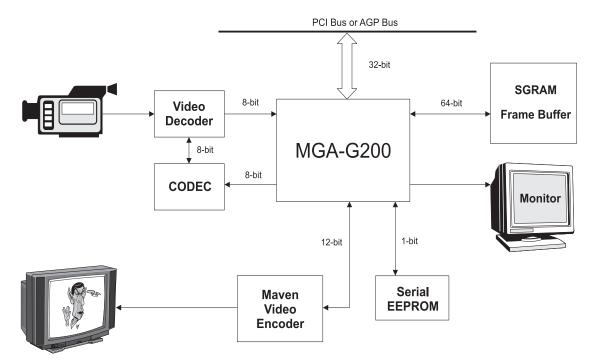

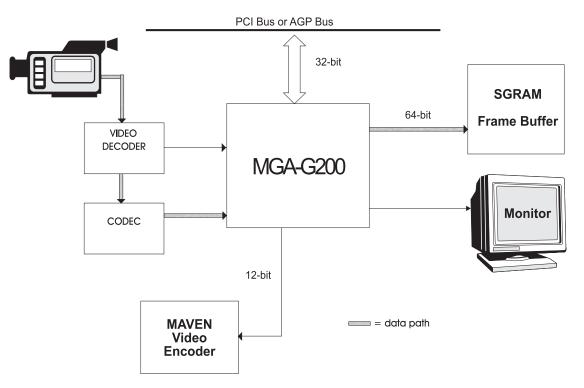

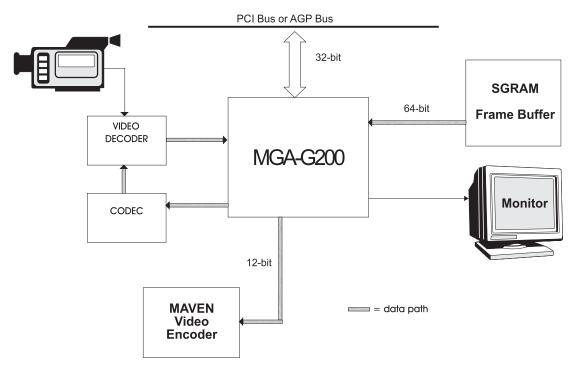

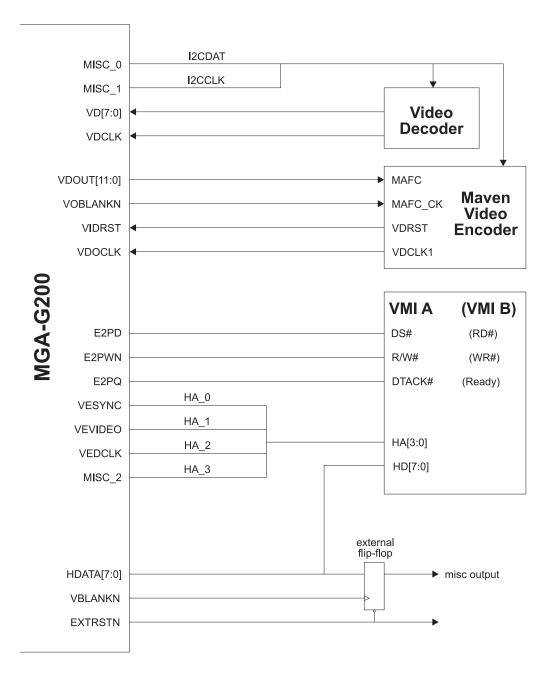

## 1.2 System Block Diagram

Figure 1-1: System Block Diagram

#### **1.3 Application Areas**

- A Windows accelerator with high performance levels. The MGA-G200 will complement the MGA family by delivering a strong price/performance point for users who need top performance at high resolution and color depths.

- Full acceleration of Windows multimedia and game applications. Specifically, 3D texture mapped games achieve a significant boost in performance and image quality with the MGA-G200 3D and triangle setup engine. In addition, all other types of games will be accelerated by a combination of the MGA-G200's DirectDraw, Direct 3D, and Direct Video engine.

- Digital video playback is accelerated to full screen, full motion, with high-quality scaling. The architecture supports all of today's popular CODECs.

- Full acceleration of all MS-DOS applications via MGA-G200's ultra-fast 32-bit VGA core.

- Video capture

- DVD and MPEG2 playback

- Video editing

- Video out to a TV with MAVEN

#### 1.4 Target Markets

- Home, SOHO, and multimedia PC markets

- Mainstream business markets

- Computer gaming

- Workstation market

- Professional multimedia PC markets

- Desktop publishing

- CAD

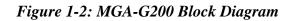

## 1.5 Block Diagram

The MGA-G200 is composed of 9 sections:

- Bus Controller

- Setup Engine

- Drawing Engine

- Video Device Interface

- VGA Graphics Controller

- Backend Video Engine

- Memory Controller

- Display Controller

- Display and Video Output Interface

#### 1.6 Features

#### 1.6.1 PCI / AGP Bus Controller

- PCI 2.1 compliant

- AGP 1.0 compliant

- Supports AGP 2X mode

- Supports AGP sideband signalling

- PCI and AGP bus mastering support for texture fetching, command list execution and system memory to frame buffer and frame buffer to system memory transfers

- Supports AGP command pipelining

- Big and Little Endian support

#### 1.6.2 Triangle Setup Engine

- Fully programmable setup engine with floating point and integer operations

- Instruction cache

- Off-loads the CPU

- Pipelined for increased performance

- Parallel execution of multiple instructions

- Fast access to the 3D rendering engine

#### 1.6.3 3D and Texture Mapping Engine

- 16-bit or 32-bit Z-buffer (optionally enabled or disabled)

- 3D polygons with Gouraud shading

- Double and triple buffering

- Sub-pixel positioning

- Hardware dithering including dithering of LUT textures

- Perspective correct texture mapping

- Storage of source textures in off-screen frame buffer and system memory

- Texture cache for increased performance

- Selectable high quality texture filtering modes, including on-the-fly minify-magnify filter selection

- True color lighting of textures

- Specular lighting

- Depth cuing and fogging

- Stipple and true Alpha blending

- Transparency

- Keying on textures is supported

- Source textures may be in the following formats:

- Color Look Up Table (compressed) 4 bpp (bit/pixel) or 8 bpp

- True Color: 5:6:5, 1:5:5:5, 4:4:4:4, 8:8:8:8

- Video: YCbCr 4:2:2 using hardware color space conversion

- Direct 3D support and acceleration

- Open GL support and acceleration

#### 1.6.4 2D Engine

- Line draw engine with patterning

- 2D polygons with patterning capabilities

- BITBLT engine

- Stretch BLT

- System memory to frame buffer BLT

- Frame buffer to system memory BLT

- Color expansion

- Clipping

- Transparency and color keying

- Dithering

- Direct Draw support

#### 1.6.5 VGA Engine

- Fully VGA compatible

- Accelerated performance

#### 1.6.6 Video Engine

- Video scaling is supported in both frontend and backend video engines

- Independent X and Y scaling with high quality filtering

- Support YCbCr 4:2:2 and YCbCr 4:2:0 formats

- Support for true graphics overlay in a rectangular window, and optionally with color keying

- Synchronized video/graphics updates (no tearing) are supported

- Supports any number of video windows/sprites simultaneously

- Sync reset input for video genlock and overlay

- Hardware color space conversion

- ITU-R 656 compatible video input port

- Parallel video device host port with DMA capability

- Video pass-through mode to video output port

- Proprietary 12-bit video output port

- Support and acceleration of DVD and MPEG2 playback

- Direct Video support and acceleration

#### 1.6.7 Display Engine

- Integrated DAC

- 250 MHz operation

- Supports shared memory and graphic overlay modes

- $\blacksquare$  3 x 256 x 8 look-up table

- Hardware color cursor

- VGA compatible

- Hardware pan and zoom

- DDC level 2B compliant

#### 1.6.8 Memory Controller

- Supports from 2 to 16 MBytes of memory

- up to 4 banks of 2bank x 128Kword x 32bit SGRAM

- up to 4 banks of 2bank x 256Kword x 32bit SGRAM

- up to 4 banks of 4bank x 128Kword x 32bit SGRAM

- up to 2 banks of 2bank x 512Kword x 16bit SDRAM

- Supports block write and write per bit for added performance

- Supports operating frequencies up to 143 MHz

- Configurable SSTL or LVTLL support

#### 1.6.9 Other Features

- PCI bus power management compliant

- PC98 compliant

- Serial EEPROM interface

- VESA 2.0-compliant

## 1.7 Typographical Conventions Used

Table 1-1: Typographical Conventions

| Description                                                                                                                                                                                         | Example                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Active low signals are indicated by a trailing forward slash. Signal names appear in upper-case characters.                                                                                         | VHSYNC/                       |

| Numbered signals appear within angle brackets, separated by a colon.                                                                                                                                | MA<8:0>                       |

| Register names are indicated by upper-case bold sans-serif letters.                                                                                                                                 | DEVID                         |

| Fields within registers are indicated by lower-case bold sans-serif letters.                                                                                                                        | vendor                        |

| Bits within a field appear within angle brackets, separated by a colon.                                                                                                                             | vendor<15:0>                  |

| Hexadecimal values are indicated by a trailing letter 'h'.                                                                                                                                          | CFFFh                         |

| Binary values are indicated by a trailing letter 'b' or are enclosed in single quotes, as: '00' or '1'. In a bulleted list within a register description field, 0: and 1: are assumed to be binary. | 0000 0010ь                    |

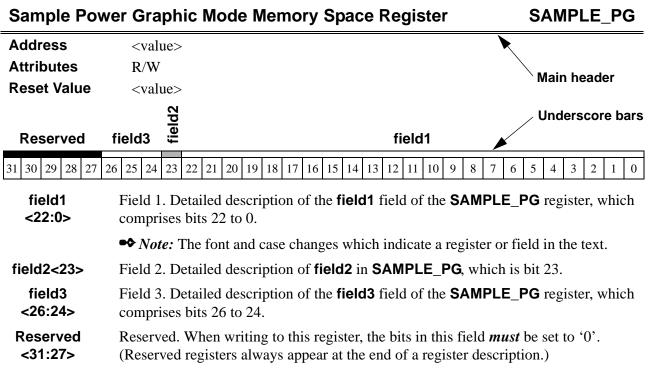

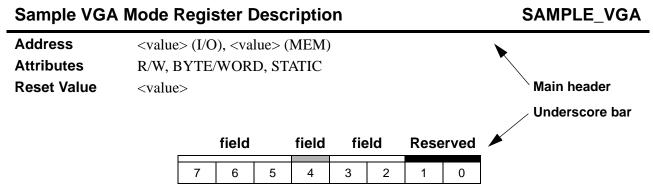

| Special conventions are used for the register descriptions. Refer to the sample re in Sections 3.1.1, 3.2.1, and 3.3.1.                                                                             | gister description pages      |

| In a table, X = "don't care" (the value doesn't matter)                                                                                                                                             | 1X = Register Set C           |

| Emphasized text and table column titles are set in bold italics.                                                                                                                                    | This bit <i>must be set</i> . |

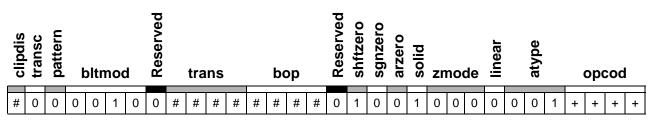

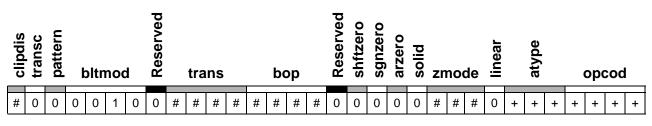

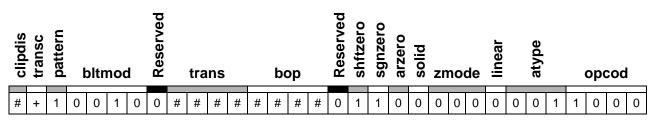

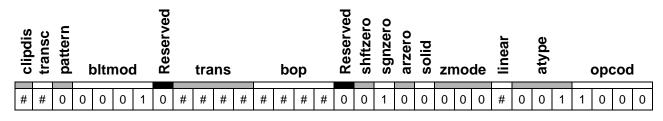

| In the <b>DWGCTL</b> illustrations (in Chapter 4), the '+' and '#' symbols have a spe-<br>cial meaning. This is explained in 'Programmer's Specification' on page 4-1.                              | trans<br># # # #              |

## 1.8 Locating Information

The MGA-G200 register descriptions are located in Chapter 3. These descriptions are divided into several sections, and arranged in alphabetical order within each section.

- To find a register by name (when you know which section it's in): go the section and search the names at the top of each page for the register you want.

- To find a register by its index or address, refer to the tables in Chapter 2. Indirect access register indexes are duplicated on the description page of the direct access register that they refer to.

- To find a particular field within a register, search in the Alphabetical List of Register Fields at the back of the manual.

Information on how to program the MGA-G200 registers is located in Chapter 4. Hardware design information is located in Chapter 5. Appendix A contains pinout, timing, and other general information.

At the beginning of this manual you will find a complete Table of Contents, a List of (major) Figures, and a List of (major) Tables.

# Chapter 2: Resource Mapping

| Memory Mapping              | <mark>2-2</mark> |

|-----------------------------|------------------|

| Configuration Space Mapping | 2-2              |

| MGA General Map             |                  |

| MGA Control Aperture        |                  |

| Register Mapping            | 2-5              |

#### 2.1 Memory Mapping

Note: All addresses and bits within dwords are labelled for a Little-Endian processor (X86 series, for example).

#### 2.1.1 Configuration Space Mapping

Table 2-1: MGA-G200 Configuration Space Mapping

| Address | Name/Note                | Description                                                      |  |

|---------|--------------------------|------------------------------------------------------------------|--|

| 00h-03h | DEVID                    | Device Identification                                            |  |

| 04h-07h | DEVCTRL                  | Device Control                                                   |  |

| 08h-0Bh | CLASS                    | Class Code                                                       |  |

| 0Ch-0Fh | HEADER                   | Header                                                           |  |

| 10h-13h | MGABASE2                 | MGA Frame Buffer Aperture Address                                |  |

| 14h-17h | MGABASE1                 | MGA Control Aperture Base                                        |  |

| 18h-1Bh | MGABASE3                 | MGA ILOAD Aperture Base Address                                  |  |

| 1Ch-2Bh | Reserved <sup>(1)</sup>  | —                                                                |  |

| 2Ch-2Fh | SUBSYSID                 | Location for reading the Subsystem ID.<br>Writing has no effect. |  |

| 30h-33h | ROMBASE                  | ROM Base Address                                                 |  |

| 34h-37h | CAP_PTR                  | Capabilities Pointer                                             |  |

| 38h-3Bh | Reserved <sup>(1)</sup>  | —                                                                |  |

| 3Ch-3Fh | INTCTRL                  | Interrupt Control                                                |  |

| 40h-43h | OPTION                   | Option register number 1                                         |  |

| 44h-47h | MGA_INDEX <sup>(2)</sup> | MGA Indirect Access Index                                        |  |

| 48h-4Bh | MGA_DATA <sup>(2)</sup>  | MGA Indirect Access Data                                         |  |

| 4Ch-4Fh | SUBSYSID                 | Location for writing the Subsystem ID.<br>Reading will give 0's. |  |

| 50h-53h | OPTION2                  | Option register number 2                                         |  |

| 54h-DBh | Reserved <sup>(1)</sup>  | —                                                                |  |

| DCh-DFh | PM_IDENT                 | Power Management Identifier                                      |  |

| E0h-E3h | PM_CSR                   | Power Management Control / Status                                |  |

| E4h-EFh | Reserved <sup>(1)</sup>  | —                                                                |  |

| F0h-F3h | AGP_IDENT <sup>(3)</sup> | AGP Capability Identifier                                        |  |

| F4h-F7h | AGP_STS <sup>(3)</sup>   | AGP Status                                                       |  |

| F8h-FBh | AGP_CMD <sup>(3)</sup>   | AGP Command                                                      |  |

| FCh-FFh | Reserved <sup>(1)</sup>  | —                                                                |  |

<sup>(1)</sup> Writing to a reserved location has no effect. Reading from a reserved location will give '0's. Access to any location (including a reserved one) will be decoded.

- <sup>(2)</sup> Not supported when powerpc is '1'. Reading to these locations will return unkown values; writing to these locations may modify any register described in the MGABASE1 range.

- <sup>(3)</sup> These locations exist only for the MGA-G200-AGP. For the MGA-G200-PCI, all these locations are reserved and '0' will be returned when read.

#### 2.1.2 MGA General Map

| Address               | Condition                                        | Name/Notes                                       |

|-----------------------|--------------------------------------------------|--------------------------------------------------|

| Aauress               |                                                  |                                                  |

| 000A0000h-000BFFFFh   | <b>GCTL6</b> <3:2> = '00', <b>MISC</b> <1> = '1' | VGA frame buffer $^{(1)(2)}$                     |

| 000A0000h-000AFFFFh   | <b>GCTL6</b> <3:2> = '01', <b>MISC</b> <1> = '1' | (Note 2 applies <b>only</b> if<br>MGAMODE = '1') |

| 000B0000h-000B7FFFh   | <b>GCTL6</b> <3:2> = '10', <b>MISC</b> <1> = '1' |                                                  |

| 000B8000h-000BFFFFh   | <b>GCTL6</b> <3:2> = '11', <b>MISC</b> <1> = '1' |                                                  |

| ROMBASE + 0000h to    | <b>biosen</b> = 1 (see <b>OPTION</b> ) and       | BIOS EPROM <sup>(1)</sup>                        |

| ROMBASE + FFFFh       | romen = 1 (see ROMBASE)                          |                                                  |

| MGABASE1 + 0000h to   | MGA control aperture                             | (1)                                              |

| MGABASE1 + 3FFFh      | (see Table 2-3)                                  |                                                  |

| MGABASE2 + 000000h to | Direct frame buffer access aperture              | (1)(2)(3)                                        |

| MGABASE2 + FFFFFFh    |                                                  |                                                  |

| MGABASE3 + 000000h to | 8 MByte Pseudo-DMA window                        | (1)(4)(5)                                        |

| MGABASE3 + 7FFFFFh    |                                                  |                                                  |

Table 2-2: MGA General Map

<sup>(1)</sup> Memory space accesses are decoded only if **memspace** = 1 (see the **DEVCTRL** configuration register).

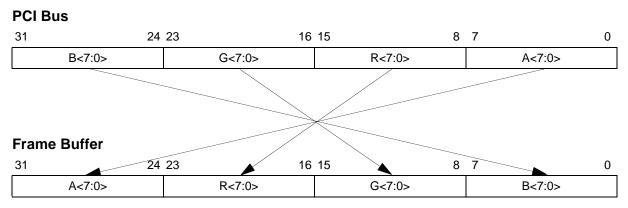

<sup>(2)</sup> Hardware swapping for Big-Endian support is performed in accordance with the settings of the **OPMODE** register's **dirDataSiz** bits.

<sup>(3)</sup> The usable range depends on how much memory has been installed. Reading or writing outside the usable range will yield unpredictable results.

<sup>(4)</sup> Hardware swapping for Big-Endian support is performed in accordance with the settings of the OPMODE register's dmaDataSiz bits.

<sup>(5)</sup> This memory space is Write Only. Reads will return *unknown* values.

#### 2.1.3 MGA Control Aperture

Table 2-3: MGA Control Aperture (extension of Table 3-2)

| MGABASE1 +  | Attr. | Mnemonic  | Device name                                             |

|-------------|-------|-----------|---------------------------------------------------------|

| 0000h-1BFFh | W     | DMAWIN    | 7KByte Pseudo-DMA window <sup>(1)(4)</sup>              |

| 1C00h-1DFFh | W     | DWGREG0   | First set of drawing registers <sup>(2)(3)(4)</sup>     |

| 1E00h-1EFFh | R/W   | HSTREG    | Host registers <sup>(2)(3)</sup>                        |

| 1F00h-1FFFh | R/W   | VGAREG    | VGA registers <sup>(3)(5)</sup>                         |

| 2000h-207Fh | R/W   | WIMEMDATA | WARP instruction memory <sup>(2)(3)</sup>               |

| 2080h-2BFFh |       |           | Reserved <sup>(6)</sup>                                 |

| 2C00h-2DFFh | W     | DWGREG1   | Second set of drawing<br>registers <sup>(2)(3)(4)</sup> |

| 2E00h-3BFFh |       | _         | Reserved <sup>(6)</sup>                                 |

| 3C00h-3C0Fh | R/W   | DAC       | RAMDAC registers <sup>(3)</sup>                         |

| 3C10h-3CFFh |       |           | Reserved <sup>(6)</sup>                                 |

| 3D00h-3DFFh | R/W   | BESREG    | Backend Scaler register <sup>(2)(3)</sup>               |

| 3E00h-3EFFh | R/W   | VINCODEC  | Video-in and codec interface $^{(2)(3)}$                |

| 3F00h-3FFFh |       | —         | Reserved <sup>(6)</sup>                                 |

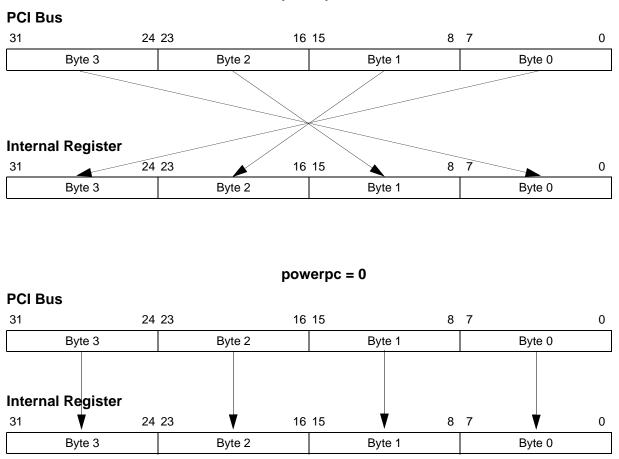

<sup>(1)</sup> Hardware swapping for Big-Endian support is performed in accordance with the settings of the **OPMODE** register's **dmaDataSiz** bits.

<sup>(2)</sup> Hardware swapping for Big-Endian support is performed when the **OPTION** configuration register's **powerpc** bit is '1'.

<sup>(3)</sup> See the register map in Table 2-4 for a more detailed view of this memory space.

<sup>(4)</sup> Reads of these locations return *unknown* values (*except* for range 2C40 to 2C4F and 2CD0 to 2CD7).

<sup>(5)</sup> VGA registers have been memory mapped to provide access to the CRTC registers in order to program MGA video modes when the VGA I/O space is not enabled.

<sup>(6)</sup> Reserved locations are decoded. The returned values are unknown.

# 2.2 Register Mapping

Note: For the values in Table 2-4, reserved locations should not be accessed. Writing to reserved locations may affect other registers. Reading from reserved locations will return unknown data. All footnote references can be found at the end of the table.

|                               |        | Memory          | I/O             |       |                                    |       |

|-------------------------------|--------|-----------------|-----------------|-------|------------------------------------|-------|

| <b>Register Mnemonic Name</b> | Access | $Address^{(1)}$ | $Address^{(2)}$ | Index | Description/Comments               | Page  |

| DWGCTL                        | WO     | 1C00h           |                 | 00h   | Drawing Control                    | 3-99  |

| MACCESS                       | WO     | 1C04h           | _               | 01h   | Memory Access                      | 3-119 |

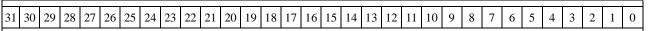

| MCTLWTST                      | WO     | 1C08h           | _               | 02h   | Memory Control Wait State          | 3-121 |

| ZORG                          | WO     | 1C0Ch           | _               | 03h   | Z-Depth Origin                     | 3-223 |

| PAT0                          | WO     | 1C10h           | _               | 04h   | Pattern                            | 3-128 |

| PAT1                          | WO     | 1C14h           |                 | 05h   | Pattern                            | "     |

|                               | WO     | 1C18h           |                 |       | Reserved                           |       |

| PLNWT                         | WO     | 1C1Ch           | _               | 07h   | Plane Write Mask                   | 3-130 |

| BCOL                          | WO     | 1C20h           | _               | 08h   | Background Color / Blit Color Mask | 3-43  |

| FCOL                          | WO     | 1C24h           |                 | 09h   | Foreground Color / Blit Color Key  | 3-107 |

|                               |        | 1C28h           | _               |       | Reserved                           |       |

|                               | WO     | 1C2Ch           | _               | 0Bh   | Reserved (SRCBLT)                  |       |

| SRC0                          | WO     | 1C30h           |                 | 0Ch   | Source                             | 3-153 |

| SRC1                          | WO     | 1C34h           | _               | 0Dh   | Source                             | "     |

| SRC2                          | WO     | 1C38h           | _               | 0Eh   | Source                             | "     |

| SRC3                          | WO     | 1C3Ch           | _               | 0Fh   | Source                             | "     |

| XYSTRT <sup>(3)</sup>         | WO     | 1C40h           |                 | 10h   | XY Start Address                   | 3-217 |

| XYEND <sup>(3)</sup>          | WO     | 1C44h           | _               | 11h   | XY End Address                     | 3-216 |

|                               | 1C48   | 3h-1C4Fh        |                 |       | Reserved                           |       |

| SHIFT <sup>(3)</sup>          | WO     | 1C50h           | _               | 14h   | Funnel Shifter Control             | 3-142 |

| DMAPAD <sup>(3)</sup>         | WO     | 1C54h           | _               | 15h   | DMA Padding                        | 3-81  |

| <b>SGN</b> <sup>(3)</sup>     | WO     | 1C58h           |                 | 16h   | Sign                               | 3-139 |

| LEN <sup>(3)</sup>            | WO     | 1C5Ch           |                 | 17h   | Length                             | 3-118 |

| <b>AR0</b> <sup>(3)</sup>     | WO     | 1C60h           |                 | 18h   | Multi-Purpose Address 0            | 3-36  |

| <b>AR1</b> <sup>(3)</sup>     | WO     | 1C64h           |                 | 19h   | Multi-Purpose Address 1            | 3-37  |

| <b>AR2</b> <sup>(3)</sup>     | WO     | 1C68h           |                 | 1Ah   | Multi-Purpose Address 2            | 3-38  |

| <b>AR3</b> <sup>(3)</sup>     | WO     | 1C6Ch           |                 | 1Bh   | Multi-Purpose Address 3            | 3-39  |

| <b>AR4</b> <sup>(3)</sup>     | WO     | 1C70h           |                 | 1Ch   | Multi-Purpose Address 4            | 3-40  |

| <b>AR5</b> <sup>(3)</sup>     | WO     | 1C74h           |                 | 1Dh   | Multi-Purpose Address 5            | 3-41  |

| <b>AR6</b> <sup>(3)</sup>     | WO     | 1C78h           |                 | 1Eh   | Multi-Purpose Address 6            | 3-42  |

|                               |        | 1C7Ch           |                 |       | Reserved                           |       |

| CXBNDRY <sup>(3)</sup>        | WO     | 1C80h           |                 | 20h   | Clipper X Boundary                 | 3-74  |

| <i>Table 2-4:</i> | Register Map | (Part 1 of 13) |

|-------------------|--------------|----------------|

|-------------------|--------------|----------------|

|                            |        | Memory          | <i>I/O</i>             |       |                                            |       |

|----------------------------|--------|-----------------|------------------------|-------|--------------------------------------------|-------|

| Register Mnemonic Name     | Access | $Address^{(1)}$ | Address <sup>(2)</sup> | Index | Description/Comments                       | Page  |

| FXBNDRY <sup>(3)</sup>     | WO     | 1C84h           | _                      | 21h   | X Address (Boundary)                       | 3-113 |

| YDSTLEN <sup>(3)</sup>     | WO     | 1C88h           | _                      | 22h   | Y Destination and Length                   | 3-220 |

| PITCH <sup>(3)</sup>       | WO     | 1C8Ch           | _                      | 23h   | Memory Pitch                               | 3-129 |

| YDST <sup>(3)</sup>        | WO     | 1C90h           |                        | 24h   | Y Address                                  | 3-219 |

| YDSTORG <sup>(3)</sup>     | WO     | 1C94h           |                        | 25h   | Memory Origin                              | 3-221 |

| <b>YTOP</b> <sup>(3)</sup> | WO     | 1C98h           |                        | 26h   | Clipper Y Top Boundary                     | 3-222 |

| <b>YBOT</b> <sup>(3)</sup> | WO     | 1C9Ch           |                        | 27h   | Clipper Y Bottom Boundary                  | 3-218 |

| CXLEFT <sup>(3)</sup>      | WO     | 1CA0h           |                        | 28h   | Clipper X Minimum Boundary                 | 3-75  |

| CXRIGHT <sup>(3)</sup>     | WO     | 1CA4h           |                        | 29h   | Clipper X Maximum Boundary                 | 3-76  |

| FXLEFT <sup>(3)</sup>      | WO     | 1CA8h           |                        | 2Ah   | X Address (Left)                           | 3-114 |

| FXRIGHT <sup>(3)</sup>     | WO     | 1CACh           |                        | 2Bh   | X Address (Right)                          | 3-115 |

| XDST <sup>(3)</sup>        | WO     | 1CB0h           |                        | 2Ch   | X Destination Address                      | 3-215 |

|                            | 1CB4   | h-1CBFh         |                        |       | Reserved                                   |       |

| DR0                        | WO     | 1CC0h           |                        | 30h   | Data ALU 0                                 | 3-85  |

| FOGSTART                   | WO     | 1CC4h           |                        | 31h   | Fog Start                                  | 3-110 |

| DR2                        | WO     | 1CC8h           |                        | 32h   | Data ALU 2                                 | 3-86  |

| DR3                        | WO     | 1CCCh           |                        | 33h   | Data ALU 3                                 | 3-87  |

| DR4                        | WO     | 1CD0h           |                        | 34h   | Data ALU 4                                 | 3-88  |

| FOGXINC                    | WO     | 1CD4h           |                        | 35h   | Fog X Inc                                  | 3-111 |

| DR6                        | WO     | 1CD8h           |                        | 36h   | Data ALU 6                                 | 3-89  |

| DR7                        | WO     | 1CDCh           |                        | 37h   | Data ALU 7                                 | 3-90  |

| DR8                        | WO     | 1CE0h           |                        | 38h   | Data ALU 8                                 | 3-91  |

| FOGYINC                    | WO     | 1CE4h           |                        | 39h   | Fog Y Inc                                  | 3-112 |

| DR10                       | WO     | 1CE8h           |                        | 3Ah   | Data ALU 10                                | 3-92  |

| DR11                       | WO     | 1CECh           | _                      | 3Bh   | Data ALU 11                                | 3-93  |

| DR12                       | WO     | 1CF0h           |                        | 3Ch   | Data ALU 12                                | 3-94  |

| FOGCOL                     | WO     | 1CF4h           |                        | 3Dh   | Fog Color                                  | 3-109 |

| DR14                       | WO     | 1CF8h           | _                      | 3Eh   | Data ALU 14                                | 3-95  |

| DR15                       | WO     | 1CFCh           | _                      | 3Fh   | Data ALU 15                                | 3-96  |

|                            | 1D00   | h-1DBFh         |                        | (6)   | Same mapping as 1C00h-1CBFh <sup>(4)</sup> |       |

| WIADDR                     | WO     | 1DC0h           |                        | 70h   | WARP Instruction Address                   | 3-203 |

| WFLAG                      | WO     | 1DC4h           |                        | 71h   | WARP Flags                                 | 3-200 |

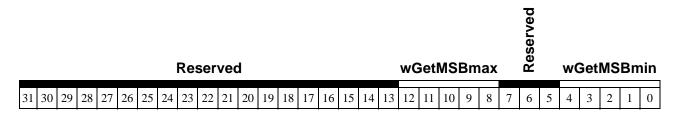

| WGETMSB                    | WO     | 1DC8h           | _                      | 72h   | WARP GetMSB Value                          | 3-202 |

| WVRTXSZ                    | WO     | 1DCCh           | _                      | 73h   | WARP Vertex Size                           | 3-210 |

| _                          | WO     | 1DD0h           |                        | 74h   | Reserved (WDBR)                            |       |

|                            | 1DD4   | h - 1E0Fh       |                        |       | Reserved                                   |       |

Table 2-4: Register Map (Part 2 of 13)

|                        |        | Memory          | I/O             |       |                                    |       |

|------------------------|--------|-----------------|-----------------|-------|------------------------------------|-------|

| Register Mnemonic Name | Access | $Address^{(1)}$ | $Address^{(2)}$ | Index | Description/Comments               | Page  |

| FIFOSTATUS             | RO     | 1E10h           |                 |       | Bus FIFO Status                    | 3-108 |

| STATUS                 | R/W    | 1E14h           |                 |       | Status                             | 3-155 |

| ICLEAR                 | WO     | 1E18h           | _               |       | Interrupt Clear                    | 3-116 |

| IEN                    | R/W    | 1E1Ch           |                 |       | Interrupt Enable                   | 3-117 |

| VCOUNT                 | RO     | 1E20h           |                 |       | Vertical Count                     | 3-188 |

| —                      | 1E24   | h - 1E2Fh       |                 |       | Reserved                           |       |

| DMAMAP30               | R/W    | 1E30h           |                 |       | DMA Map 3h to 0h                   | 3-77  |

| DMAMAP74               | R/W    | 1E34h           |                 |       | DMA Map 7h to 4h                   | 3-78  |

| DMAMAPB8               | R/W    | 1E38h           |                 |       | DMA Map Bh to 8h                   | 3-79  |

| DMAMAPFC               | R/W    | 1E3Ch           |                 |       | DMA Map Fh to Ch                   | 3-80  |

| RST                    | R/W    | 1E40h           |                 |       | Reset                              | 3-134 |

| MEMRDBK                | R/W    | 1E44h           |                 |       | Memory Read Back                   | 3-124 |

| TEST0                  | R/W    | 1E48h           |                 |       | Test0                              | 3-157 |

| AGP_PLL                | R/W    | 1E4Ch           | _               |       | AGP 2X PLL Control/Status          | 3-30  |

| PRIMPTR                | R/W    | 1E50h           |                 |       | Primary List Status Fetch Pointer  | 3-133 |

| OPMODE                 | R/W    | 1E54h           | _               |       | Operating Mode                     | 3-126 |

| PRIMADDRESS            | R/W    | 1E58h           |                 |       | Primary DMA Current Address        | 3-131 |

| PRIMEND                | R/W    | 1E5Ch           |                 |       | Primary DMA End Address            | 3-132 |

| WIADDRNB               | R/W    | 1E60h           |                 |       | WARP Instruct. Add. (Non-Blocking) | 3-205 |

| WFLAGNB                | R/W    | 1E64h           |                 |       | WARP Flags (Non-Blocking)          | 3-201 |

| WIMEMADDR              | WO     | 1E68h           |                 |       | WARP Instruction Memory Address    | 3-206 |

| WCODEADDR              | RO     | 1E6Ch           |                 |       | WARP Microcode Address             | 3-199 |

| WMISC                  | R/W    | 1E70h           |                 |       | WARP Miscellaneous                 | 3-208 |

|                        | 1E7C   | h - 1E7Fh       |                 |       | Reserved                           | _     |

| DWG_INDIR_WT<0>        | WO     | 1E80h           |                 |       | Drawing Register Indirect Write 0  | 3-98  |

|                        | WO     | 1E84h           | -1EB8h          |       |                                    |       |

| DWG_INDIR_WT<15>       | WO     | 1EBCh           |                 |       | Drawing Register Indirect Write 15 | 3-98  |

|                        | 1EC0   | h - 1FBFh       | _               |       | Reserved                           | _     |

| ATTR (Index)           | R/W    | 1FC0h           | 3C0h            |       | Attribute Controller               | 3-226 |

| ATTR (Data)            | WO     | 1FC0h           | 3C0h            |       | Attribute Controller               | "     |

| ATTR (Data)            | RO     | 1FC1h           | 3C1h            |       | Attribute Controller               | "     |

| —                      |        | 1FC1h           | 3C1h            |       | Reserved                           | _     |

| ATTR0                  | R/W    |                 |                 | 00h   | Palette entry 0                    | 3-226 |

| ATTR1                  | R/W    |                 |                 | 01h   | Palette entry 1                    | "     |

| ATTR2                  | R/W    |                 |                 | 02h   | Palette entry 2                    | "     |

| ATTR3                  | R/W    |                 |                 | 03h   | Palette entry 3                    | "     |

Table 2-4: Register Map (Part 3 of 13)

| Register Minemonic NameAccessAddress <sup>(2)</sup> IndexDescription/CommentsPageATTR4R/W0thPalette entry 4"ATTR5R/W0thPalette entry 5"ATTR6R/W0thPalette entry 5"ATTR6R/W0thPalette entry 6"ATTR7R/W0thPalette entry 7"ATTR9R/W0thPalette entry 9"ATTR9R/W0thPalette entry 9"ATTR4R/W0thPalette entry 10"ATTR5R/W0thPalette entry 10"ATTR5R/W0thPalette entry 10"ATTR6R/W0thPalette entry 10"ATTR5R/W0thPalette entry 10"ATTR1R/W0thPalette entry 10"ATTR5R/W0thPalette entry 10"ATTR5R/W0thPalette entry 10"ATTR6R/W0thPalette entry 10"ATTR5R/W0thPalette entry 103:231ATTR5R/W10thAttribute Mode Control3:231ATTR6R/W-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |        | Memory   | I/O                 |       |                                    |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------|----------|---------------------|-------|------------------------------------|-------|

| ATTR4       R/W         04h       Palette entry 4       "         ATTR5       R/W         05h       Palette entry 5       "         ATTR6       R/W         05h       Palette entry 6       "         ATTR6       R/W         07h       Palette entry 6       "         ATTR7       R/W         08h       Palette entry 7       "         ATTR9       R/W         08h       Palette entry 9       "         ATTRA       R/W         08h       Palette entry 9       "         ATTRA       R/W         08h       Palette entry 9       "         ATTRA       R/W         08h       Palette entry 16       "         ATTRD       R/W         08h       Palette entry 16       "         ATTR1       R/W         08h       Palette entry 16       "         ATTR1       R/W         10h       Attribute Mode Control       3-232         ATTR11       R/W        <                                                                                                                                                                                                                                                                                                                                                                                                                      | Register Mnemonic Name | Access | -        |                     | Index | Description/Comments               | Page  |

| ATTR5       R/W         05h       Palette entry 5       "         ATTR6       R/W         06h       Palette entry 6       "         ATTR7       R/W         07h       Palette entry 7       "         ATTR8       R/W         08h       Palette entry 8       "         ATTR9       R/W         08h       Palette entry 9       "         ATTR4       R/W         08h       Palette entry 9       "         ATTR5       R/W         08h       Palette entry 16       "         ATTR0       R/W         08h       Palette entry 16       "         ATTR0       R/W         00h       Palette entry 16       "         ATTR10       R/W         01h       Attribute Mode Control       3-239         ATTR11       R/W         11h       Overstan Color       3-231         ATTR12       R/W         13h       Horizontal Pel Panning       3-234         ATTR14       R/W <t< td=""><td>-</td><td></td><td></td><td></td><td></td><td>-</td><td></td></t<>                                                                                                                                                                                                                                                                                                                             | -                      |        |          |                     |       | -                                  |       |

| ATTR6R/W06hPalette entry 6"ATTR7R/W07hPalette entry 7"ATTR8R/W08hPalette entry 8"ATTR9R/W08hPalette entry 9"ATTR4R/W08hPalette entry 9"ATTR5R/W08hPalette entry A"ATTRCR/W08hPalette entry A"ATTRCR/W08hPalette entry D"ATTRDR/W08hPalette entry D"ATTR1R/W08hPalette entry F"ATTR5R/W07hPalette entry F"ATTR1R/W10hAttribute Mode Control3-229ATTR1R/W13hHorizontal Pel Panning3-233ATTR14R/W14hColor Select3-23414hColor Select3-239MISCW/OIFC2h3C2hInput Status Output3-299MISCR/WIFC2h3C2hInput Status Output3-296SEQ (Index)R/WIFC2h3C2hSequencer3-296SEQ (Index)R/WIFC2h3C3hSequencer3-296SEQR/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |        |          |                     |       | •                                  | "     |

| ATTR7       R/W         07h       Palette entry 7       *         ATTR8       R/W         08h       Palette entry 8       *'         ATTR9       R/W         09h       Palette entry 9       *'         ATTRA       R/W         09h       Palette entry 0       *'         ATTRB       R/W         00h       Palette entry 0       *'         ATTRD       R/W         00h       Palette entry 0       *'         ATTRE       R/W         00h       Attribute Mode Control       3-229         ATTR10       R/W         11h       Overscan Color       3-233         ATTR11       R/W         13h       Horizontal Pel Paning       3-233         ATTR12       R/W                                                                                                                                                                                                                                                                                                                                                                                                           |                        |        |          |                     |       | •                                  | "     |

| ATTR8       R/W         08h       Palette entry 8       "         ATTR9       R/W         09h       Palette entry 9       "         ATTRA       R/W         09h       Palette entry 9       "         ATTRB       R/W         08h       Palette entry B       "         ATTRD       R/W         08h       Palette entry C       "         ATTRD       R/W         08h       Palette entry D       "         ATTRD       R/W         08h       Palette entry F       "         ATTR1       R/W         08h       Palette entry F       "         ATTR1       R/W         08h       Palette entry F       "         ATTR1       R/W         10h       Attribute Mode Control       3-232         ATTR14       R/W         11h       Overscan Color       3-231         ATTR12       R/W         13h       Horizontal Pel Panning       3-233         ATTR14       R/W                                                                                                                                                                                                                                                                                                                                                                                                                  |                        |        |          |                     |       | •                                  | "     |

| ATTR9R/W09hPalette entry 9"ATTRAR/W0AhPalette entry A"ATTRBR/W0BhPalette entry B"ATTRCR/W0ChPalette entry C"ATTRDR/W0DhPalette entry D"ATTRDR/W0DhPalette entry D"ATTRER/W0DhPalette entry E"ATTR1R/W10hAttribute Mode Control3-229ATTR10R/W11hOverscan Color3-231ATTR11R/W13hHorizontal Pel Panning3-233ATTR13R/W14hColor Plane Enable3-232ATTR14R/W14hColor Select3-23414hColor Select3-239MISCWOIFC2h3C2hInput Status 03-292MISCWOIFC2h3C2hMiscellaneous Output3-294R/WIFC3h3C3hReserved, not decoded for I/OSEQ (Index)R/WIFC3h3C3hSequencer3-299SEQ(Inda)R/W00hSEQO3-299SEQ1R/W00hCharacter Map Select3-300<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |        |          |                     |       | •                                  | "     |

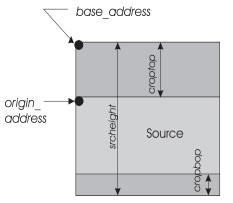

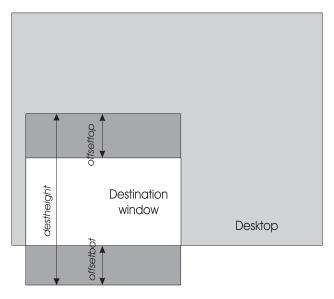

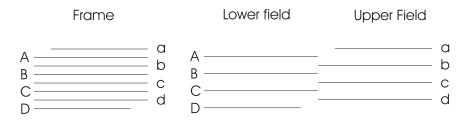

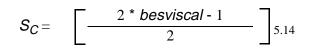

| ATTRAR/W0AhPalette entry A"ATTRBR/W0BhPalette entry B"ATTRCR/W0ChPalette entry C"ATTRDR/W0DhPalette entry D"ATTRER/W0EhPalette entry D"ATTRFR/W0EhPalette entry F"ATTR10R/W10hAttribute Mode Control3-229ATTR11R/W12hColor Plane Enable3-231ATTR12R/W13hHorizontal Pel Panning3-233ATTR13R/W14hColor Select3-234ATTR14R/W14hColor Select3-23414hColor Select3-234INSTS0RO1FC2h3C2hInput Status 03-292MISCWO1FC2h3C2hMiscellaneous Output3-294R/W1FC3h3C3h <sup>(5)</sup> Reserved, not decoded for I/OSEQ (Index)R/W1FC4h3C4hSequencerSEQR/W00hSEQ03-298SEQ2R/W02hMap Mask3-299SEQ3R/W03hCharacter Map Select3-300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |        |          |                     |       |                                    | "     |