MGA (Matrox Graphics Architecture)

# **MGA ATLAS Specification**

Revision 1 April I, 1994 Manual No. 10348-MS

#### Trademarks

Matrox<sup>®</sup> is a registered trademark of Matrox Electronic Systems Ltd.

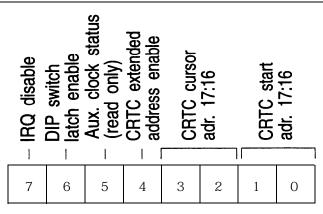

MGA,™ ATLAS,™ TITAN,™ ATHENA,™, STORM,™ DUBIC,™ MGA Marvel,™ MGA VideoPro,™ QCDP,™ MGA DynaView,™ PixelTOUCH,™ MGA Control Panel,™ ModeSWITCH,™ ConsistentColor,™ and WinSqueeze!™ are trademarks of Matrox Electronic Systems Ltd.

*IBM*,<sup>®</sup> VGA, @ CGA, @ 8514/A, @ and MDA @ are registered trademarks of International Business Machines Corporation; Micro Channel (*MCA*)™ is a trademark of International Business Machines Corporation

Hercules<sup>®</sup> is a registered trademark of Hercules Computer Technology, Inc.

Intel<sup>®</sup> is a registered trademark, and 386,™ 486,™ Pentium,™ and 80387 ™ are trademarks of Intel Corporation

Windows™ is a trademark of Microsoft Corporation; Microsoft,<sup>®</sup> MS-DOS, @ and OS/2<sup>®</sup> are registered trademarks of Microsoft Corporation

AutoCAD<sup>®</sup> is a registered trademarkof Autodesk Inc.

RAMDAC<sup>™</sup> is a trademark of Brooktree

All other nationally and internationally recognized trademarks and tradenames used in this manual are hereby acknowledged.

This document contains confidential proprietary information that may not be disclosed without written permission from Matrox Electronic Systems Ltd.

#### Copyright Matrox Electronic Systems Ltd., 1993, 1994. All rights reserved.

Disclaimer: Matrox Electronic Systems Ltd. reserves the **right** to make changes in **specifications** at any time and without notice. The information provided by this document is believed to be accurate and reliable. However; no responsibility is assumed by Matrox Electronic Systems Ltd. for its use; nor for any **infringements** of patents or other **rights** of third parties **resulting** from its use. No license is granted under any patents or **patent** rights of Matrox Electronic Systems Ltd.

#### Matrox Confidential

## **Chapter 1: MGA Product Overview**

| 1.1       | Introduction                                                            | 1-2   |

|-----------|-------------------------------------------------------------------------|-------|

|           | 1.1.1 MGA Chipset                                                       | 1-2   |

|           | 1.1.2 Features                                                          | 1-3   |

|           | 1.1.3 Driver Support                                                    | 1-3   |

|           |                                                                         |       |

|           | 1.1.5 Video Support                                                     | 1-4   |

|           | 1.1.6 Documentation                                                     | 1-4   |

| Chapter 2 | : ATLAS Overview                                                        |       |

| 2.1       | Introduction                                                            | 2-2   |

|           | 2.1.1 Bus Interface                                                     | 2-2   |

|           | 2.1.2 VGA                                                               | 2-2   |

|           | 2.1.3 Bus Interface FIFO (BFIFO)                                        | .2-4  |

|           | 2.1.4 Address Processing Unit (APU)                                     | 2-4   |

|           | 2.1.5 Data Processing Unit (DPU)                                        | .2-4  |

| 2.2       | Frame Buffer                                                            | 2-4   |

| Chapter 3 | : Operation Modes                                                       |       |

| 3.1       | VGA Mode                                                                | 3-2   |

|           | 3.1.1 FlexFont                                                          | 3-2   |

|           | 3.1.2 Enhanced Modes                                                    | 3-2   |

|           | 3.1.3 Display Adapter Support                                           | 3-3   |

|           | 3.1.4 Differences Between ATLAS Ports and IBM VGA Display Adapter Ports | . 3-3 |

|           | 3.1.4.1 Hercules Mode Port Differences                                  | 3-3   |

|           | 3.1.4.2 CGA Mode Port Differences                                       | 3-3   |

|           | 3.1.4.3 EGA Mode Port Differences                                       | 3-3   |

|           | 3.1.4.4 VGA Mode Port Differences                                       | 3-3   |

| 3.2       | Power Graphic Mode                                                      | 3-4   |

|           | 3.2.1 Memory Configurations                                             | .3-4  |

|           | 3.2.2 Pixel Format                                                      | 3-8   |

|           | 3.2.3 Overview of Drawing Operations                                    | 3-11  |

|           | 3.2.4 DMA and Pseudo DMA                                                | 3-12  |

|           | 3.2.4.1 DMA                                                             | 3-16  |

|           | 3.2.4.2 Pseudo DMA                                                      | 3-18  |

|       |       | 3.2.5 Programming the <b>CRTC</b> for Power Graphic Mode | 3-20  |

|-------|-------|----------------------------------------------------------|-------|

|       |       | 3.2.5.1 Registers                                        | 3-20  |

|       |       | 3.2.5.2 Interlace Modes                                  | 3-20  |

|       |       | 3.2.5.3 Hardware Panning                                 | 3-20  |

|       |       | 3.2.5.4 Hardware Zooming                                 | 3-20  |

|       |       | 3.2.5.5 Programming Constraints                          | 3-21  |

|       |       | 3.2.5.6 Frame Buffer Alignment                           | 3-22  |

|       |       | 3.2.5.7 Overscan                                         | 3-23  |

|       |       | 3.2.6 Interrupts                                         | 3-23  |

|       | 3.3   | Access Restrictions to Some Resources                    | 3-24  |

|       | 3.4   | Initialization and Configuration                         | 3-25  |

|       |       | 3.4.1 Configuration Elements                             | 3-25  |

|       |       | 3.4.2 Booting in VGA Mode                                | 3-25  |

|       |       | 3.4.3 Booting in Power Graphic Mode                      | 3-25  |

|       | 3.5   | Mode Switching                                           | 3-26  |

|       |       | 3.5.1 Switching From VGA Mode to Power Graphic Mode      | 3-26  |

|       |       | 3.5.2 Switching From Power Graphic Mode to VGA Mode      | 3-26  |

|       | 3.6   | Power up and Reset                                       | 3-28  |

|       |       | 3.6.1 Hard Reset                                         | 3-28  |

|       |       | 3.6.2 Soft Reset                                         | 3-28  |

|       |       | 3.6.3 Configuring ATLAS in a Board-level Design          | 3-29  |

|       |       | 3.6.3.1 Special Considerations for PCI                   | 3-31  |

|       |       | 3.6.4 Reset Field Definitions                            | 3-31  |

| Chapt | ter 4 | : Memory Mapping                                         |       |

|       | 4.1   | ISA and PCI Configurations                               | 4-2   |

|       |       | 4.1.1 Configuration Space Mapping                        | 4-2   |

|       | 4.2   | Memory Space Mapping                                     | 4-2   |

|       |       | 4.2.1 ISA Interface                                      | 4-2   |

|       |       | 4.2.2 PCI Interface                                      | 4-3   |

|       |       | 4.2.3 Power Graphic Mode Mapping (ISA and PCI)           | . 4-3 |

|       | 4.3   | I/O Mapping                                              | 4-7   |

| Chan  | ter 5 | 5: Register Descriptions                                 |       |

| Chup  |       | Register Descriptions                                    | 5-2   |

|       |       | 5.1.1 Power Graphics Mode Registers                      |       |

|       |       | 5.1.2 VGA Mode Registers                                 |       |

|       | 5.2   | Power Graphic Mode Register Descriptions                 | 5-4   |

|       | 5.2   | VGA Mode Register Descriptions                           | 5-55  |

|       | 5.5   | . S. Lasse Report Descriptions                           | -     |

## **Chapter 6: Hardware Interface**

| 6.1      | Introduction                                        | 6-2  |

|----------|-----------------------------------------------------|------|

| 6.2      | Host Interface                                      | 6-2  |

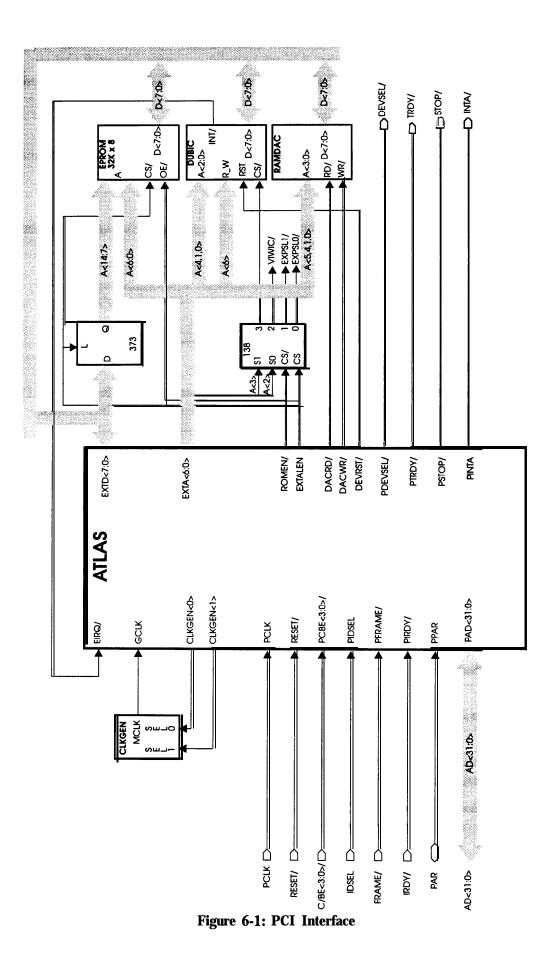

|          | 6.2.1 PCI Interface                                 | 6-2  |

|          | 6.2.1.1 PCI Bus Operation                           | 6-2  |

|          | 6.2.1.2 PCI Cycles                                  | 6-5  |

|          | 6.2.1.3 Bus Sizing                                  | 6-6  |

|          | 6.2.1.4 External Devices                            | 6-6  |

|          | 6.2.2 ISA Interface                                 | 6-7  |

|          | 6.2.2.1 Bus Sizing                                  | 6-7  |

|          | 6.2.2.2 External Devices                            | 6-9  |

| 6.3      | VRAM Interface                                      | 6-10 |

|          | 6.3.1 Memory Interleave                             | 6-12 |

|          | 6.3.2 Patch <b>RAM</b>                              | 6-13 |

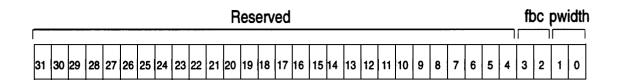

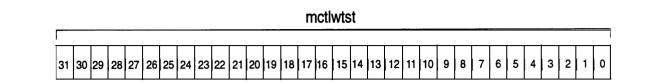

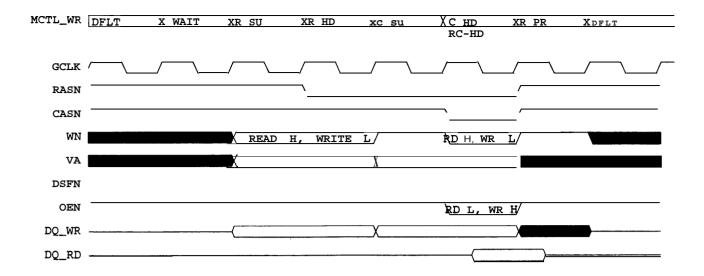

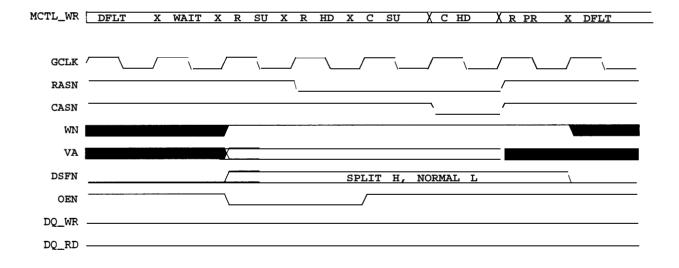

|          | 6.3.3 MCTLWTST Register Timings                     | 6-13 |

|          | 6.3.4 VRAM Interconnect                             | 6-16 |

|          | 6.3.5 Coprocessor Requests                          | 6-19 |

| 6.4      | VIDEO Interface                                     | 6-21 |

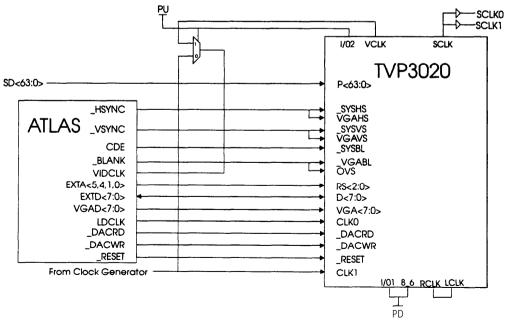

|          | 6.4.1 Power Graphic Mode (No DUBIC Mode)            | 6-21 |

|          | 6.4.2 Power Graphic Mode (DUBIC Mode)               | 6-22 |

|          | 6.4.3 VGA Mode                                      | 6-22 |

|          | 6.4.4 Slaving ATLAS                                 | 6-23 |

| Appendix | A: Technical Data                                   |      |

| A.1      | Pin List                                            | A-2  |

|          | A.1.1 Host Interface (ISA Configuration)            | A-2  |

|          | A.1.2 Host Interface (PCI Configuration)            | A-4  |

|          | A.1.3 External Device Interface (ISA Configuration) | A-5  |

|          | A.I.4 External Device Interface (PCI Configuration) | A-6  |

|          | A.1.5 Drawing Engine (No DUBIC Mode)                | A-7  |

|          | A.1.6 Drawing Engine (DUBIC Mode)                   | A-8  |

|          | A.1.7 Video Interface (No DUBIC Mode)               | A-9  |

|          | A.1.8 Video Interface (DUBIC Mode)                  | A-10 |

|          | A. 1.9 Miscellaneous                                | A-10 |

|          | A.1.9.1 Fixed                                       | A-10 |

|          | A.1.9.2 Test                                        | A-10 |

|          | A.1.9.3 VCC/GND                                     | A-11 |

| A.2 Electrical Specification                             | A-12 |

|----------------------------------------------------------|------|

| A.2.1 Maximum Ratings                                    | A-12 |

| A.2.2 DC Specifications                                  | A-12 |

| A.2.3 AC Specifications                                  | A-16 |

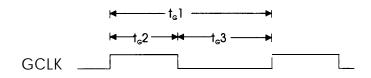

| A.2.3.1 GCLK                                             | A-16 |

| A.2.3.2 Host Interface Timing                            | A-16 |

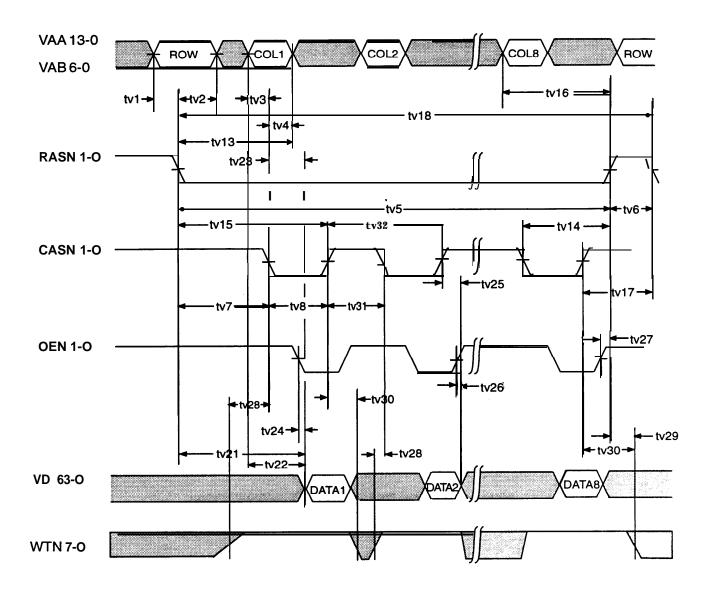

| A.2.3.3 Power Graphic Mode <b>VRAM</b> Interface 'liming | A-25 |

| A.2.3.4 VGA Mode VRAM Interface Timing                   | A-38 |

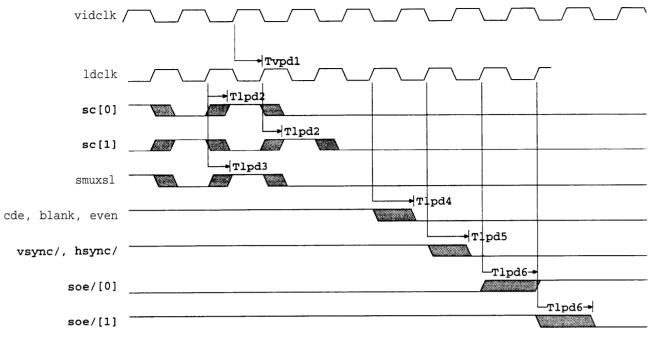

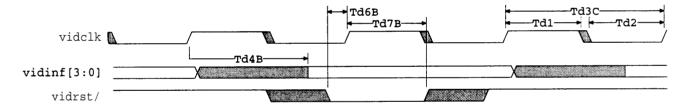

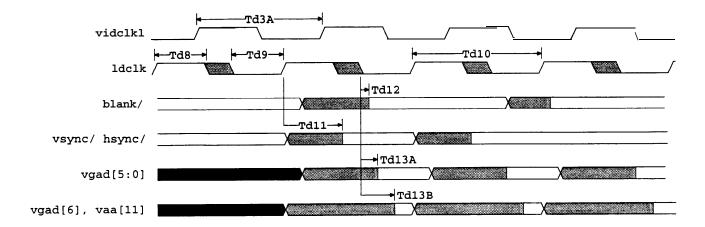

| A.2.3.5 Video Interface Timing                           | A-45 |

| A.3 Mechanical Specification                             | A-48 |

| Appendix B: Customer Support                             |      |

| B.1 Customer Support                                     | B-2  |

| Power Graphic Mode Registers                             |      |

| Power Graphic Mode Register Fields                       |      |

| VGA Mode Registers                                       |      |

| Index                                                    |      |

## **Chapter 3: Operation Modes**

| Table 3-1: Initialization of Drawing Registers       | 3-11 |

|------------------------------------------------------|------|

| Table 3-2: DMA Access Types                          | 3-17 |

| Table 3-3: Power Graphic Mode Video Registers        | 3-21 |

| Table 3-4: Interrupt Sources                         | 3-24 |

| Table 3-5: Strapping Definition: ATLAS-based Design  | 3-30 |

| Chapter 4: Memory Mapping                            |      |

| Table 4-1 : ATLAS Memory Mapping                     | 4-2  |

| Table 4-2: ATLAS PCI Mode Memory Mapping             | 4-3  |

| Table 4-3: ATLAS Power Graphic Mode Memory Mapping   | 4-3  |

| Table 4-4: ATLAS Register Mapping                    | 4-5  |

| Table 4-5: I/O Mapping                               | 4-8  |

| Chapter 6: Hardware Interface                        |      |

| Table 6-1: Frame Buffer Config. (No DUBIC Mode)      | 6-10 |

| Table 6-2: Frame Buffer Config. (DUBIC Mode)         | 6-11 |

| Table 6-3: ATLAS/VRAM Address Connection             | 6-18 |

| Table 6-4: RAS Assignment                            | 6-18 |

| Table 6-5: CAS and OE Assignment                     | 6-19 |

| Table 6-6: DSF Assignment                            | 6-19 |

| Table 6-7: Power Graphic Mode Video Generation       | 6-22 |

| Table 6-8: VGA Signal Assignment                     | 6-22 |

| Appendix A: Technical Data                           |      |

| Table A- 1: DC Specification                         | A-12 |

| Table A-2: Host Interface (ISA) Signal Buffers       | A-13 |

| Table A-3: Host Interface (PCI) Signal Buffers       | A-13 |

| Table A-4: External Device Signal Buffers (ISA)      | A-14 |

| Table A-5: External Device Signal Buffers (PCI)      | A-14 |

| Table A-6: Drawing Engine Signal Buffers (No DUBIC)  | A-14 |

| Table A-7: Drawing Engine Signal Buffers (DUBIC)     | A-15 |

| Table A-8: Video Interface Signal Buffers (No DUBIC) | A-15 |

| Table A-9: Video Interface Signal Buffers (DUBIC)    | A-15 |

| Table A-10: Miscellaneous Signal Buffers             | A-16 |

| Table A-11: Host Interface Parameter List            | A-19 |

| Table A-12: Host PCI 5 V liming Parameters              | A-21 |

|---------------------------------------------------------|------|

| Table A- 13: External Device Parameter List             | A-24 |

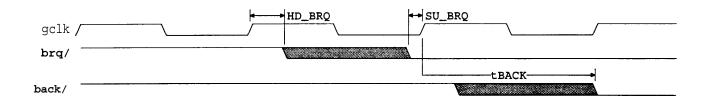

| Table A- 14: BRQ Back Timing Parameter List             | A-25 |

| Table A- 15: Data Transfer Cycle Parameter List         | A-27 |

| Table A- 16: Hyper Page Read Cycle Parameter List       | A-29 |

| Table A- 17: Page Read Cycle Parameter List             | A-31 |

| Table A-l 8: Page Write Cycle Parameter List            | A-33 |

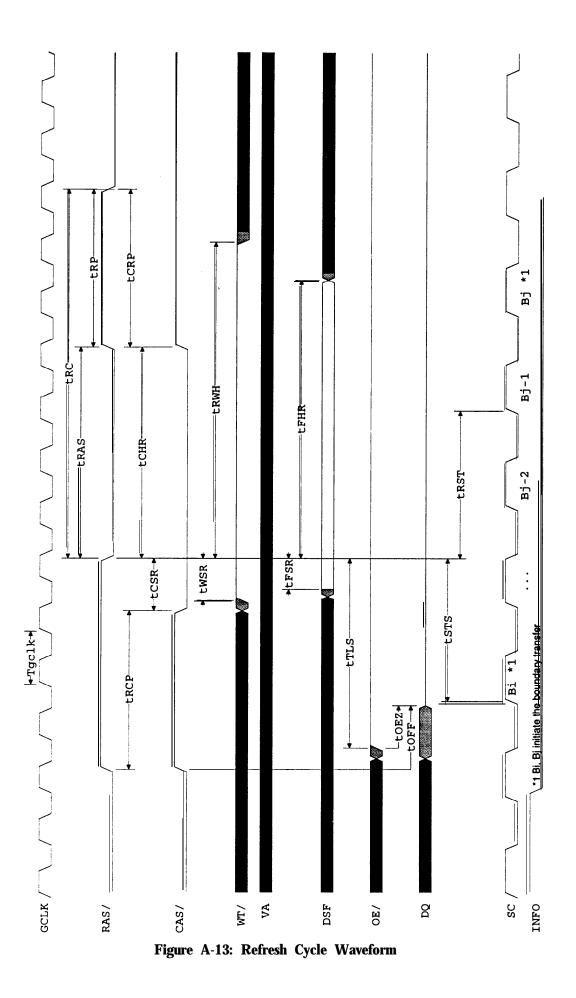

| Table A- 19: Refresh Cycle Parameter List               | A-35 |

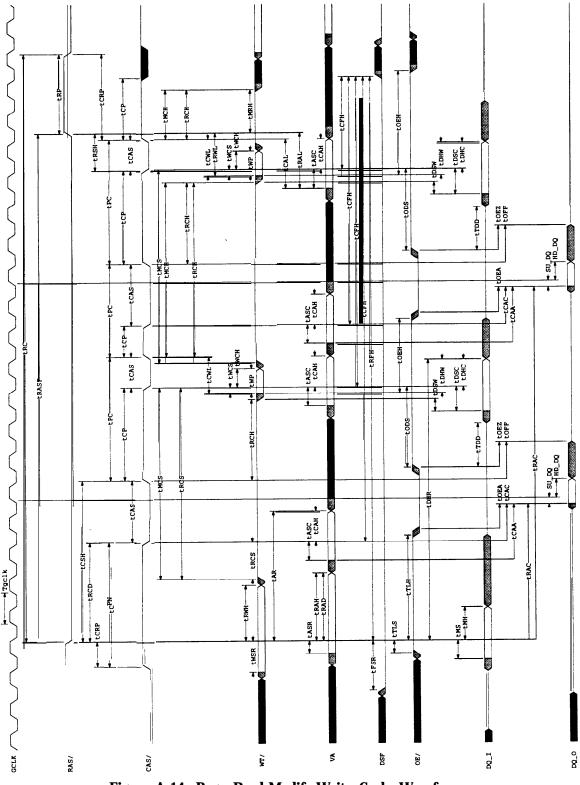

| Table A-20: Page Read-Modify-Write Cycle Parameter List | A-37 |

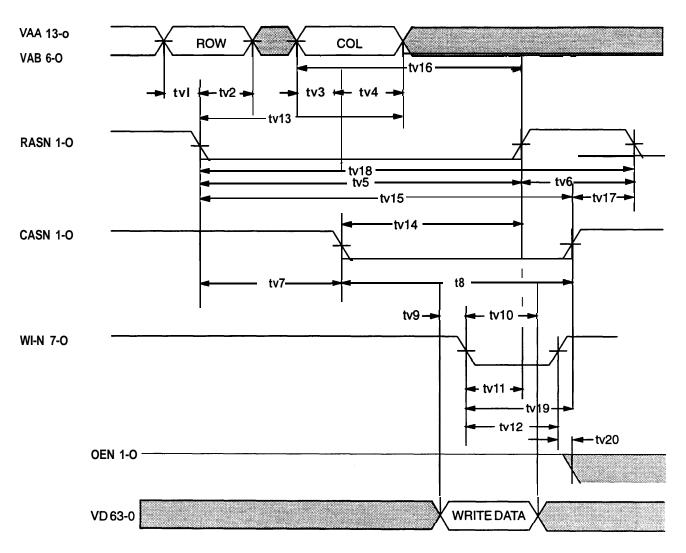

| Table A-21 : Video Dynamic RAM Write Cycles             | A-40 |

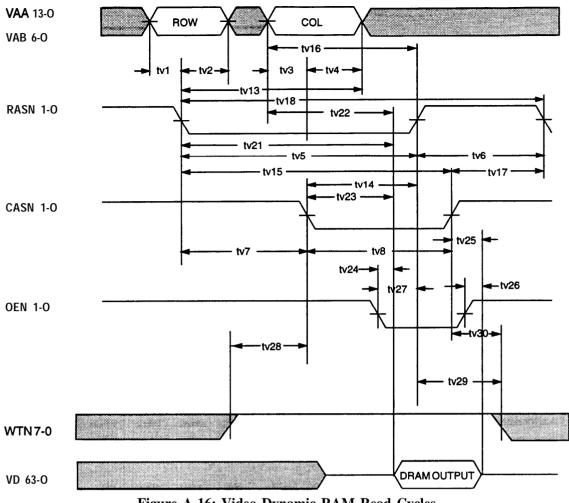

| Table A-22: Video Dynamic RAM Read Cycles               | A-42 |

| Table A-23: Video Dynamic RAM Page Read Cycles          | A-44 |

| Table A-24: Video Interface liming Parameter List       | A-47 |

| Chapter 1: MGA Product Overview                         |      |

|---------------------------------------------------------|------|

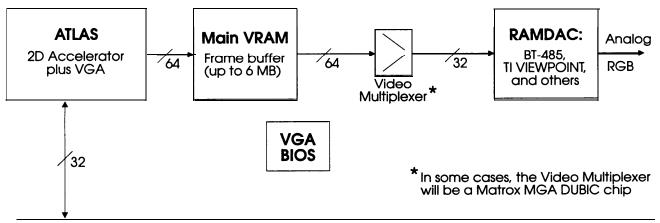

| Figure 1- 1: Typical Implementation Block Diagram       | 1-2  |

| Chapter 2: ATLAS Overview                               |      |

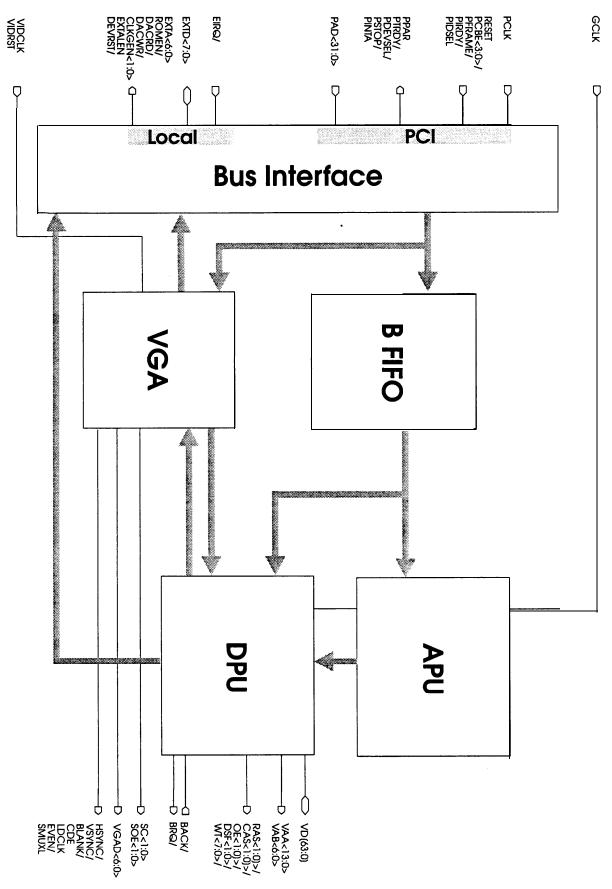

| Figure 2-1: ATLAS Block Diagram                         | 2-3  |

| Chapter 3: Operation Modes                              |      |

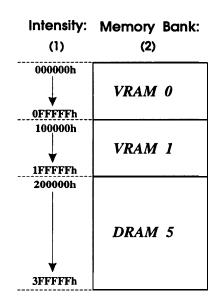

| Figure 3-1: fbm = 0                                     | 3-4  |

| Figure 3-2: fbm = 1                                     | 3-4  |

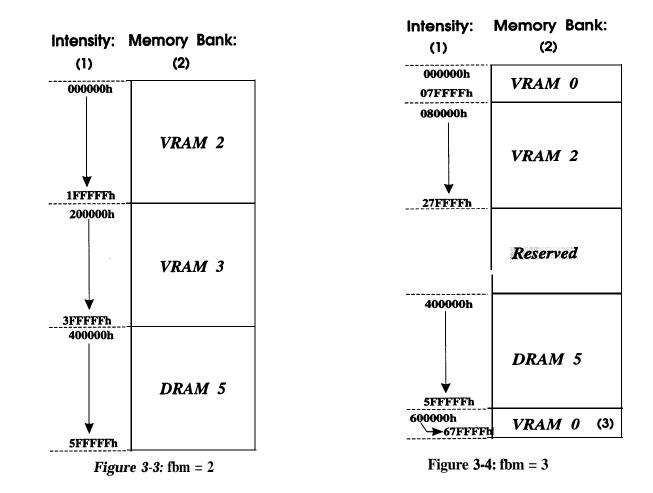

| Figure 3-3: fbm = 2                                     | 3-5  |

| Figure 3-4: fbm = 3                                     | 3-5  |

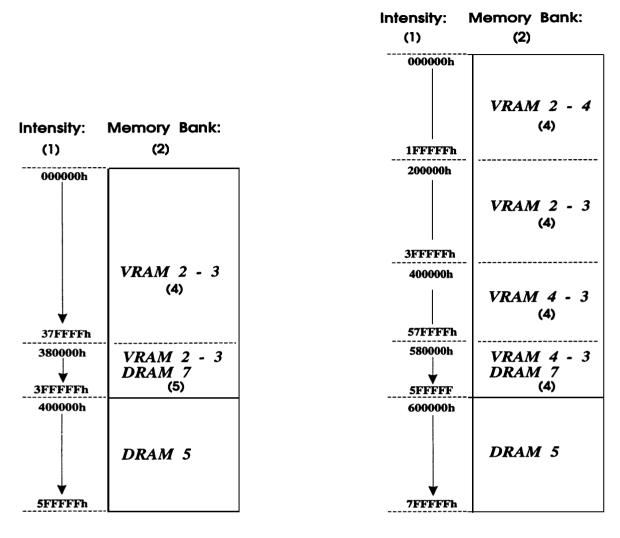

| Figure 3-5: fbm = 4                                     | 3-6  |

| Figure 3-6: fbm = 5                                     | 3-6  |

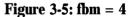

| Figure 3-7: fbm = 6                                     | 3-7  |

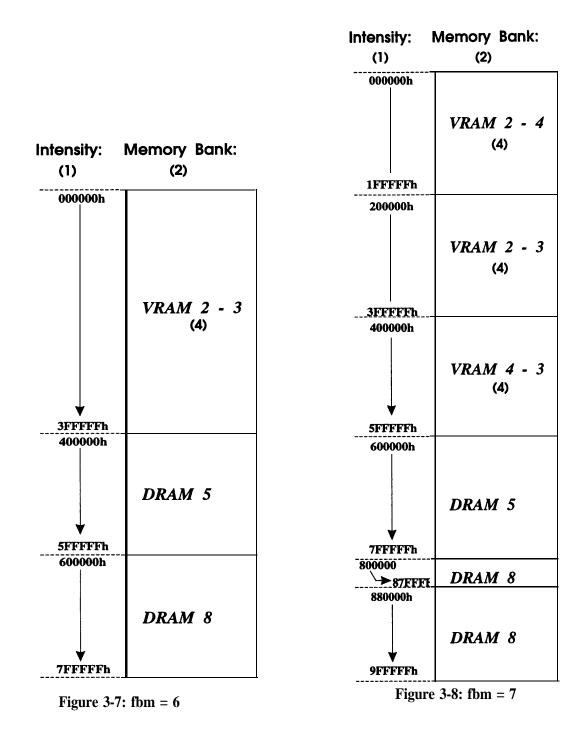

| Figure 3-8: fbm = 7                                     | 3-7  |

| Figure 3-9: Pixel Slice                                 | 3-8  |

| Figure 3-10: Pixel Data                                 | 3-9  |

| Figure 3-1 1: 32-bit Access                             | 3-9  |

| Figure 3-12: ILOAD/IDUMP Formats / 1, 24, 32 bpp        | 3-10 |

| Figure 3-13: DMA General Purpose Write Sequence         | 3-12 |

| Figure 3-14: DMA Gen. Purpose Transfer Buffer Structure | 3-13 |

| Figure 3-15: DMA Vector Sequence                        | 3-14 |

| Figure 3-16: DMA Vector Transfer Buffer Structure       | 3-14 |

| Figure 3-17: DMA BLIT Write Sequence                    | 3-15 |

| Figure 3-18: DMA BLIT Write Transfer Buffer Structure   | 3-15 |

| Figure 3-19: Memory Org. (1280x1024x8 - two 1M Banks)   | 3-23 |

| Figure 3-20: Configuration Bus                          | 3-29 |

| Chapter 6: Hardware Interface                           |      |

| Figure 6-1: PCI Interface                               | 6-3  |

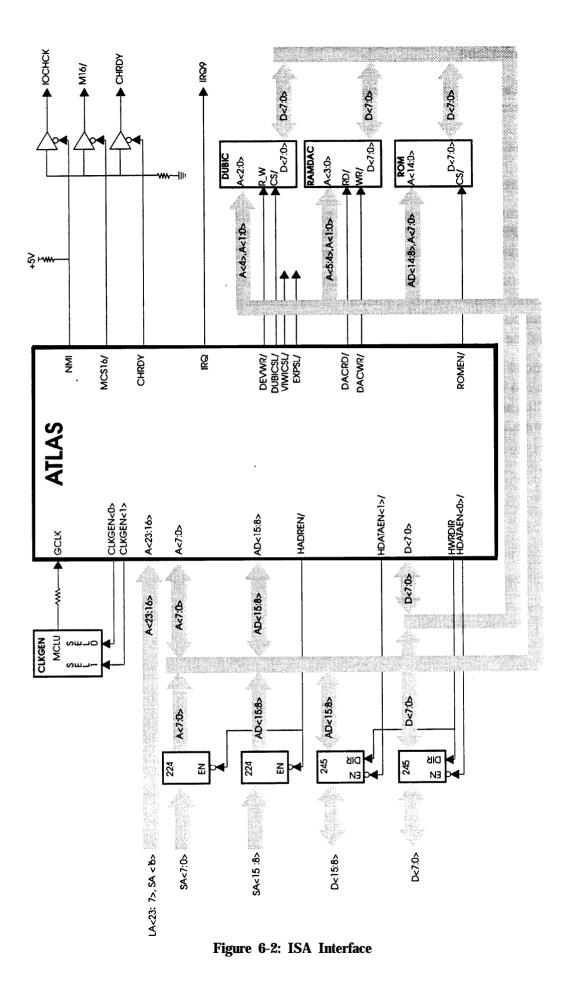

| Figure 6-2: ISA Interface                               | 6-8  |

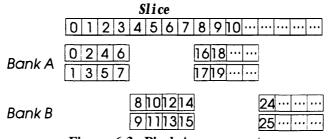

| Figure 6-3: Pixel Arrangement                           | 6-12 |

| Figure 6-4: MCTLWTST for Data Transfer Cycle            | 6-14 |

| Figure 6-5: MCTLWTST for Direct Access Cycle            | 6-14 |

| Figure 6-6: MCTLWTST for Page Write and Page Read Cycle | 6-15 |

| Figure 6-7: MCTLWTST for Refresh Cycle                  | 6-15 |

| Figure 6-8: Page Read-Modify-Write/Anti-aliasing Cycle | 6-16 |

|--------------------------------------------------------|------|

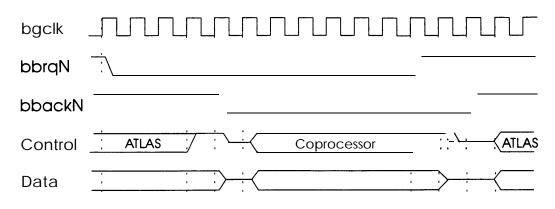

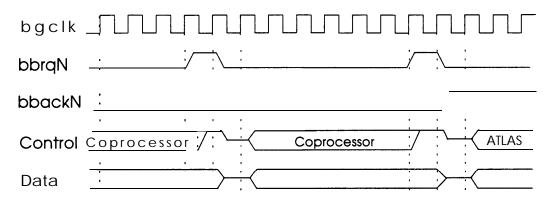

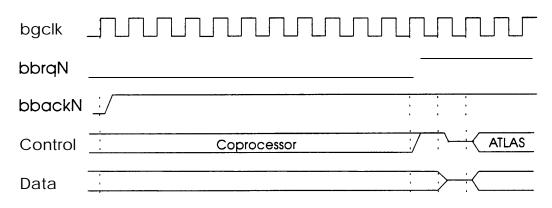

| Figure 6-9: Normal Request and Release of the Bus      | 6-20 |

| Figure 6-10: 1 gclk Release for Refresh                | 6-20 |

| Figure 6-11: ATLAS Request for Data Transfer           | 6-20 |

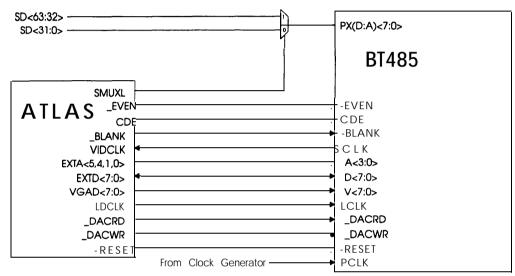

| Figure 6-12: ATLAS/Memory Connection to 32 Bit RAMDAC  | 6-21 |

| Figure 6-13: ATLAS/Memory Connection to 64 Bit RAMDAC  | 6-21 |

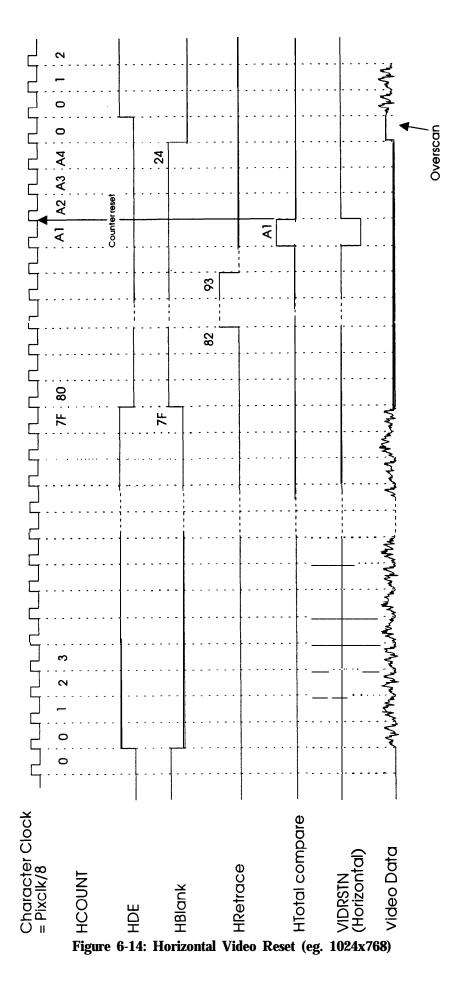

| Figure 6-14: Horizontal Video Reset (eg. 1024x768)     | 6-24 |

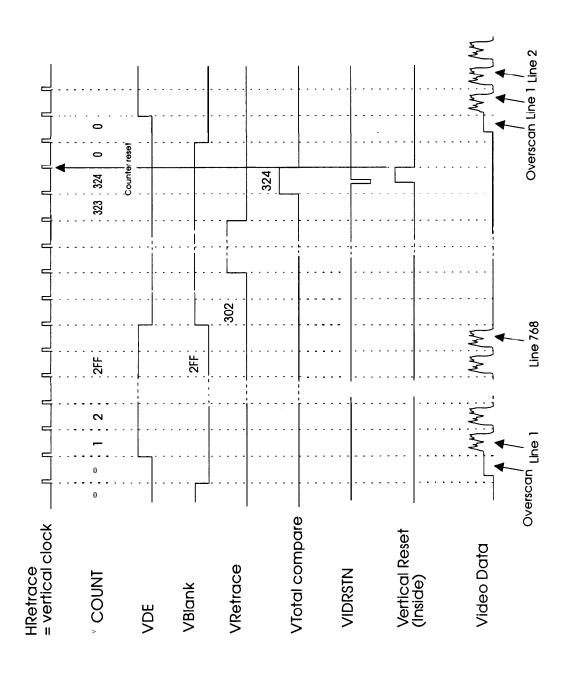

| Figure 6-15: Vertical Video Reset (eg. 1024x768)       | 6-25 |

# Appendix A: Technical Data

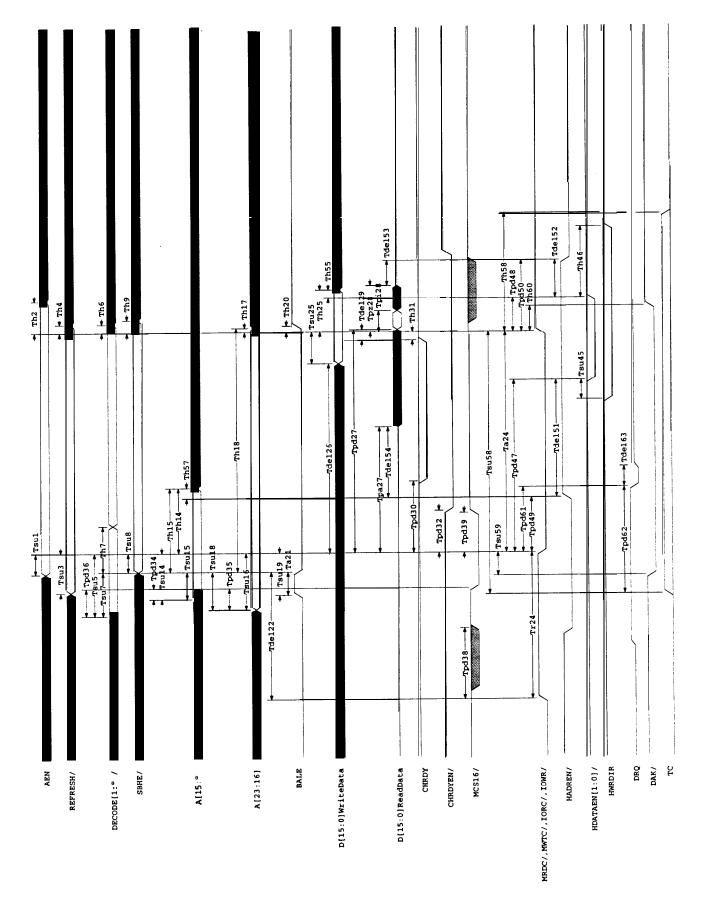

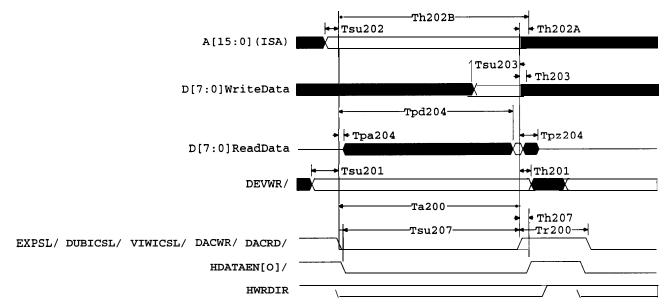

| Figure A- 1: ISA Host Interface Waveform              | A-17  |

|-------------------------------------------------------|-------|

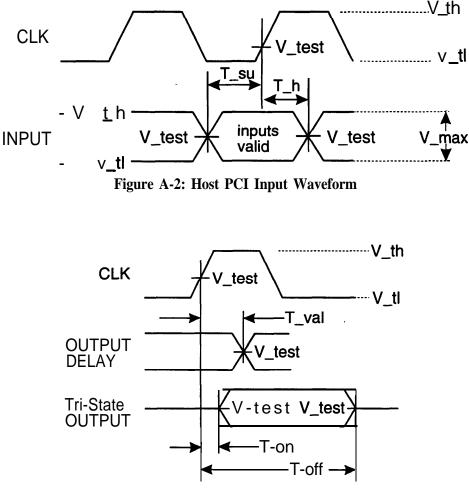

| Figure A-2: Host PCI Input Waveform                   | A-20  |

| Figure A-3: Host PCI Output Waveform                  | A-20  |

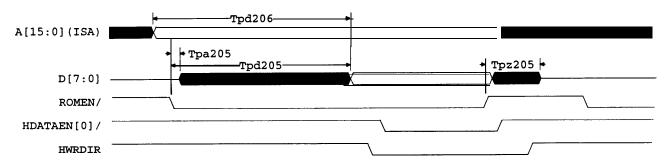

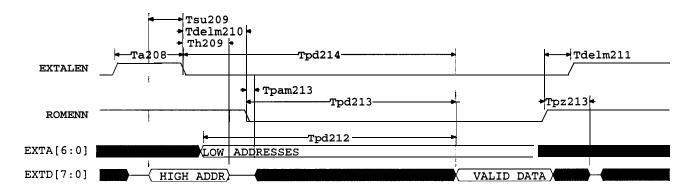

| Figure A-4: ROM Host Interface Waveform               | A-21  |

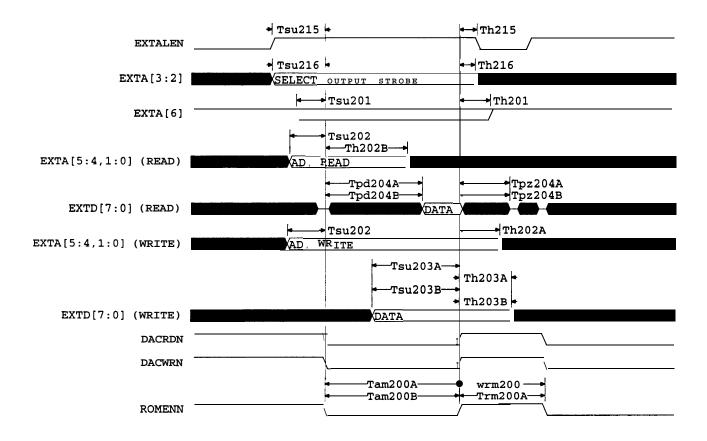

| Figure A-5: External Device Interface Waveform (ISA)  | A-2 1 |

| Figure A-6: External Device Interface Waveform (PCI)  | A-22  |

| Figure A-8: BRQ Back Timing                           | A-25  |

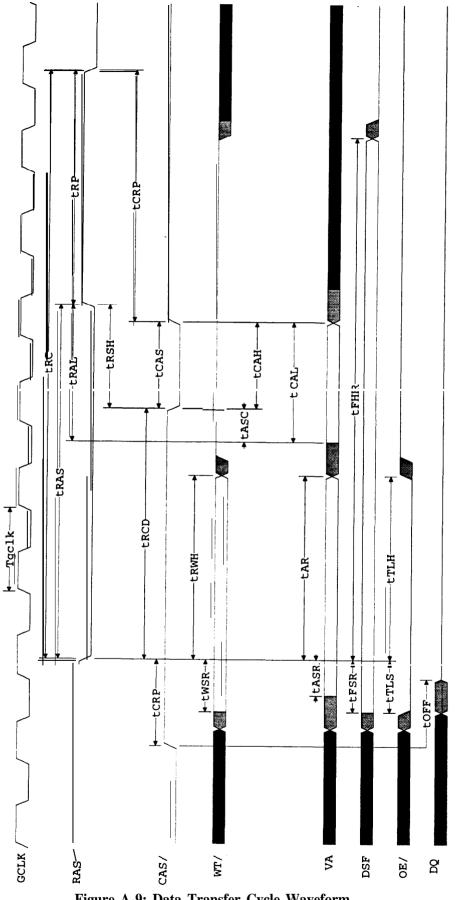

| Figure A-9: Data Transfer Cycle Waveform              | A-26  |

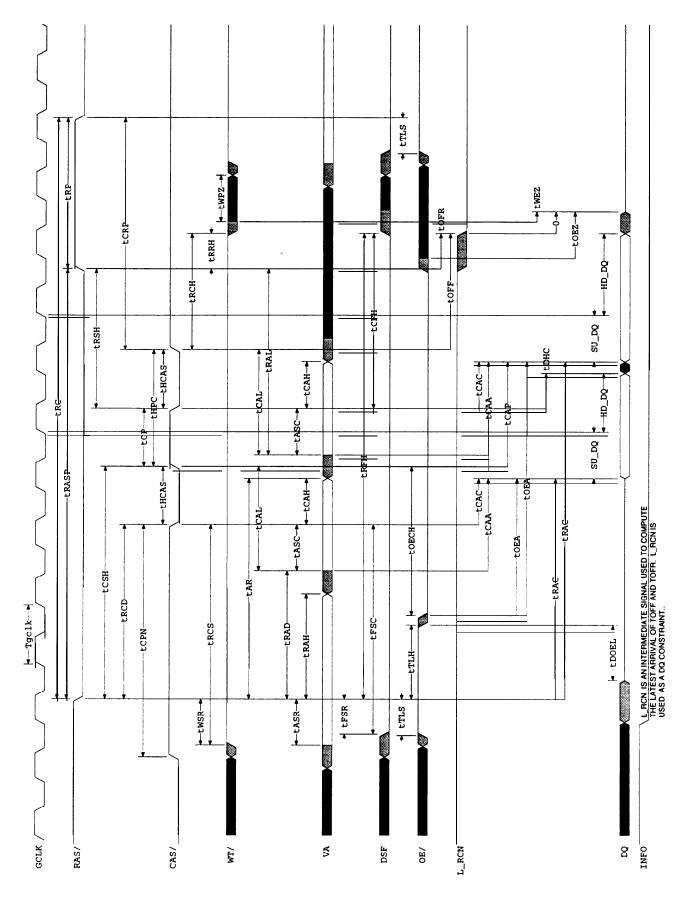

| Figure A-10: Hyper Page Read Cycle Waveform           | A-28  |

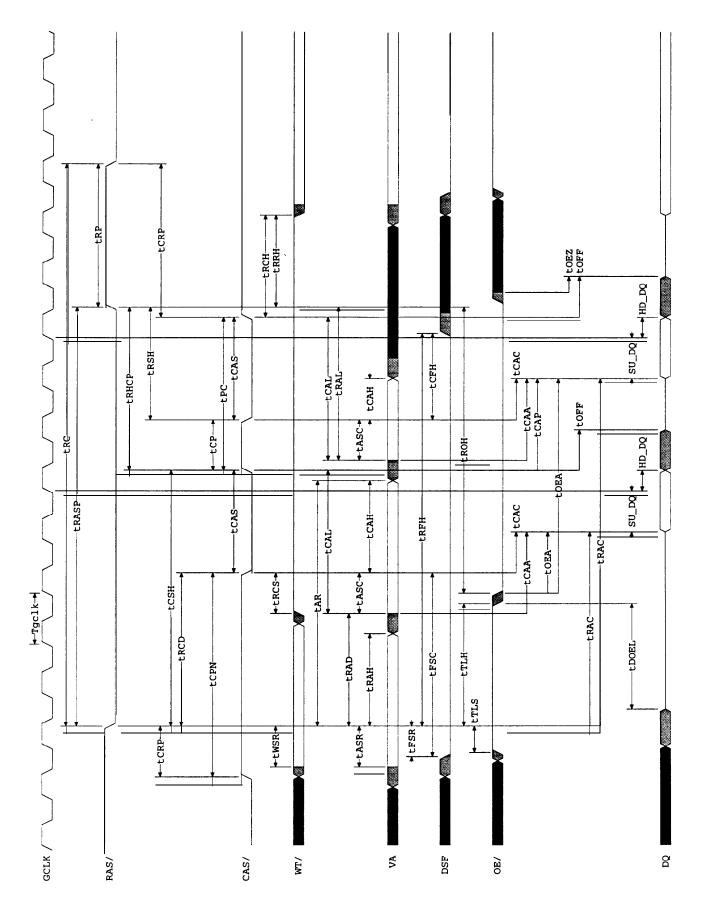

| Figure A-l 1: Page Read Cycle waveform                | A-30  |

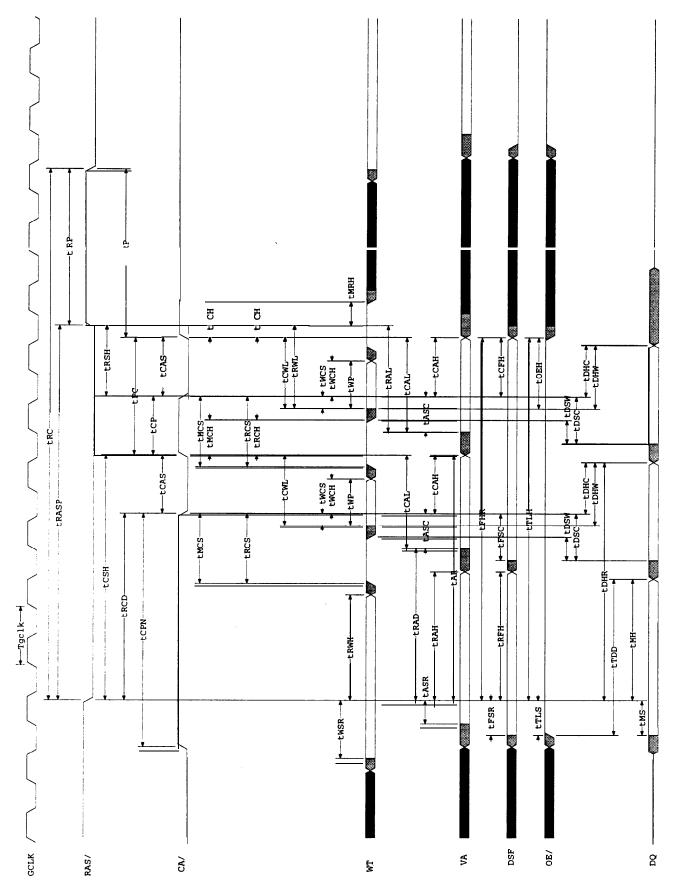

| Figure A-l 2: Page Write Cycle Waveform               | A-32  |

| Figure A- 13: Refresh Cycle Waveform                  | A-34  |

| Figure A- 14: Page Read-Modify-Write Cycle Waveform   | A-36  |

| Figure A- 15: Video Dynamic RAM Write Cycles          | A-39  |

| Figure A-l 6: Video Dynamic RAM Read Cycles           | A-41  |

| Figure A-l 7: Video Dynamic RAM Page Read Cycles      | A-43  |

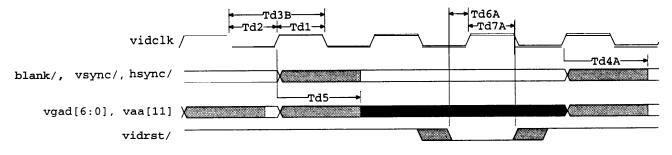

| Figure A-l 8: Video liming (No DUBIC Mode)            | A-45  |

| Figure A- 19: Power Graphic Video Timing (DUBIC Mode) | A-45  |

| Figure A-20: VGA Mode (Normal) Video liming           | A-46  |

| Figure A-2 1: VGA Mode (Slave) Video Timing           | A-46  |

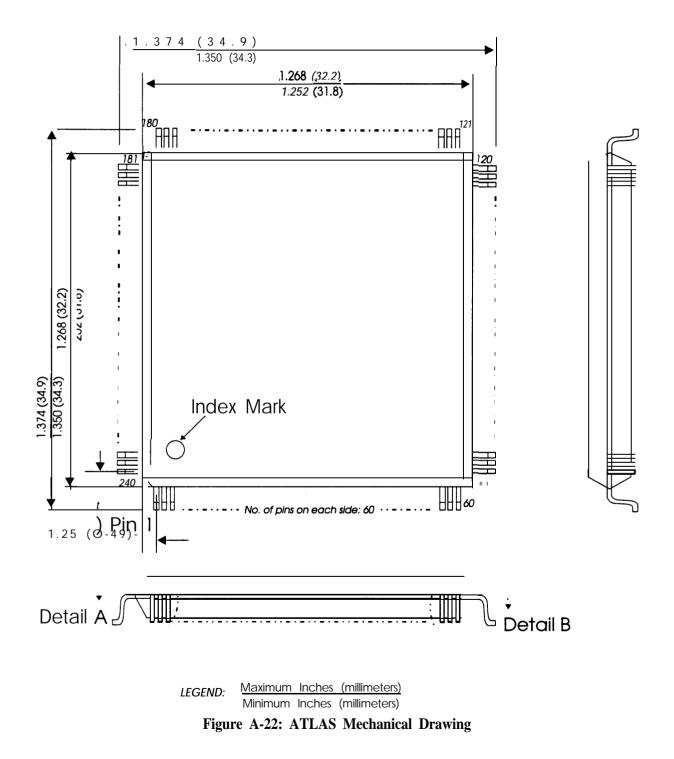

| Figure A-22: ATLAS Mechanical Drawing                 | A-48  |

| Figure A-23: ATLAS Mechanical Drawing (Details)       | A-49  |

# Chapter 1: MGA Product Overview

This chapter contains an overview of the Matrox MGA chipset features and software products.

## **1.1 Introduction**

Matrox MGA is a high-speed, high-resolution graphics accelerator series of products designed for the power user. MGA is very suitable for GUI environments such as Microsoft Windows 3.1 and Windows NT, IBM OS/2 PM, and AutoCAD. It offers ultra high resolution displays with true color and many other innovative hardware and software enhancements.

MGA's 64-bit graphics power, in combination with a 486 or Pentium-class PC is in our opinion the best graphics solution if you require true workstation-level performance at a reasonable price.

## 1.1.1 MGA Chipset

The Matrox ATLAS chip lies at the heart of MGA's powerful graphics capabilities. It offers an ISA interface for ISA bus products, and a PCI interface for PCI systems. Several possible memory configurations permit design of 8, 16, 24, and 32 bits/pixel displays at resolutions up to 1600 x 1200 pixels. Figure 1.1 shows a block diagram of a typical graphics display adapter which uses the MGA ATLAS chip.

Host Processor Interface (ISA, PCI, EISA, MicroChannel, VESA-VL, or proprietary)

## Figure I-I: Typical Implementation Block Diagram

The chipset functions as a stand-alone graphics controller that features an integrated VGA to offer both VGA Mode and high-resolution Power Graphic mode operation. It contains a 32-location Command FIFO and address and data processing units (APU, DPU). In addition, LINE, Trapezoid, and BITBLT drawing operations are available, supported by DMA and Pseudo DMA transfers. These enhancements make screen operations such as redrawing and scrolling appear instantaneous.

## 1.1.2 Features

- From 1 to 6 MB of frame buffer VRAM in configurations up to 32 bits/pixel

- VRAM block write operations for maximum speed

- Photo-realistic true color display, and QCDP (Quality Color Dithering Process) for displays of less than 24 bits/pixel

- Ultra-high resolution of 1600 x 1200, with 256 colors

- Workstation performance with speeds from 2 to 12 times faster than competitors' boards

- 64-bit frame buffer data bus width

- Integrated VGA, for full support of all DOS applications, eliminating the need for a separate VGA card

- Integrated PCI interface

- Direct RAMDAC interface

- Fast, flicker-free refresh rates up to 120 Hz

- Support for ISA, VESA VL, Micro Channel, EISA, PCI, and other architectures

- Installation of up to four boards in a system

## 1.1.3 Driver Support

MGA Power Drivers are available for Windows 3.1 and AutoCAD Rel. 11/12. The 'MGA Supplementary Drivers' package contains drivers for Windows NT, OS/2, and MicroStation (with dual display). We provide:

- Support for popular Windows and DOS design and presentation applications

- DynaView driver for AutoCAD Release 11 and 12 that includes real-time scroll bars, spy glass, and bird's eye view, etc.

- Support for AutoCAD 12 for Windows, and MicroStation PC

## 1.1.4 Windows Support

- Control Panel for Windows controls the **PixelTouch** hardware pan and zoom, Virtual Desktop, and 'on the fly' resolution switching (without rebooting Windows) through the use of **hotkeys**

- Font anti-aliasing in hardware

- In addition to the drivers listed above, the 'MGA Supplementary Drivers' package also contains the ConsistentColor monitor calibration utility to ensure accuracy between your screen display and the printed output, and the WinSqueeze! on-the-fly JPEG file compression utility, which can achieve compression ratios of up to 28: 1

## 1.1.5 Video Support

- MGA interfaces with the Matrox Marvel video capture/video windowing board

- The MGA VideoPro NTSC/PAL encoder provides output capability for recording presentations, animations, and AutoCAD walk-throughs to tape

- Hardware-assisted Video for Windows (VfW) and Indeo are supported

## 1.1.6 Documentation

Other documentation available for Matrox MGA products includes:

- MGA TITAN Specification (10318-MS)\* A description of the Matrox MGA TITAN chip.

- MGA DUBIC Specification (10232-MS)\* A description of the Matrox MGA DUBIC chip.

| • MGA SDK Manual (10330-MF)                                            | A user/reference manual for the MGA software developer's kit for DOS and Windows 3.1.                                                                                                |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>MGA DynaView /2D for AutoCAD<br/>Manual (10345-MN)</li> </ul> | A user/reference manual for the Matrox MGA <b>DynaView</b> driver for <b>AutoCAD</b> and 3D Studio.                                                                                  |

| <ul> <li>MGA Supplemantary Drivers Manual<br/>(10352-MN)</li> </ul>    | An installation/user manual which describes our OS/2, Windows NT, and MicroStation PC drivers, as well as the MGA WinSqueeze! and ConsistentColor programs for the Windows platform. |

\* Like the *ATLAS Specification*, these are restricted documents. See your Matrox Sales representative for more details.

The *PCI Bus Specification* from the PCI Special Interest Group contains additional information on hardware implementation for the PCI architecture.

# Chapter 2: ATLAS Overview

**T**his chapter introduces the Matrox MGA ATLAS chip and its component sections.

## 2.1 Introduction

The Matrox ATLAS chip supports both VGA and Power Graphic mode displays. VGA mode supports the VGA standard, while Power Graphic mode provides additional high-speed, ultra-high resolution displays. You can switch between the two modes while using the same monitor for both. ATLAS can be configured for PCI bus systems, or for ISA (and other) bus systems.

The ATLAS chip is a stand-alone graphics controller which is composed of several sections that work together to accomplish the many tasks required of them. The ATLAS sections are listed below, and discussed in the following sections of this chapter.

- Bus Interface

- VGA

- Bus Interface FIFO (BFIFO)

- Address Processing Unit (APU)

- Data Processing Unit (DPU)

## 2.1.1 Bus Interface

This section of ATLAS implements the interface with the host. Two bus interfaces are supported: an ISA interface and a PCI interface for the PCI bus.

The Bus Interface section includes:

- □ All of the control circuitry for the ISA and PCI buses

- □ PCI control, decoding, and re-mapping circuitry

- □ Configuration registers

- □ I/O buffers (8-location FIFO for writable devices; 4-location FIFO for ILOAD operations)

- □ Byte-alignment circuitry; 32-to-8 bit access conversion for VGA and I/O

- □ The control circuitry for external devices

## 2.1.2 VGA

This section implements the VGA functions, and includes:

- □ The VGA core, which interfaces directly with the frame buffer in VGA mode.

- □ The circuitry for video refresh in Power Graphic mode (see Section 6.3.5), which includes address generation, data transfer requests, and video control circuitry.

Figure 2-1: ATLAS Block Diagram

## 2.1.3 Bus Interface FIFO (BFIFO)

This section implements the Command FIFO from the host to the drawing engine. All access to the drawing registers passes through this 32-location **FIFO**, which holds the data as well as the address of the targeted register in the drawing engine.

## 2.1.4 Address Processing Unit (APU)

This section of ATLAS generates the sequencing of the drawing operations. Each drawing operation is broken down into a sequence of read and write commands which are sent to the DPU. The APU includes:

- Generation of the sequence for each drawing operation, and the addresses and mask

- D Processing of the slope for vectors and trapezoid edges

- □ Rectangle clipping

## 2.1.5 Data Processing Unit (DPU)

This section manipulates the data according to the currently-selected operation. It also converts read and write commands from the APU into memory cycles to the frame buffer. The DPU includes:

- □ Generation of memory cycles

- □ Host compress, decompress, and data formatting

- □ The funnel shifter for data alignment

- □ The Boolean ALU

- □ Anti-aliasing

- □ The patterning and dithering circuitry

- □ The Data FIFO for **BitBLIT** operations

- □ The color expansion circuitry for character drawing

## 2.2 Frame Buffer

ATLAS can interface directly with the VRAM and DRAM. Memory combinations of 128K x 8 VRAM, 256K x 8 VRAM, 256K x 16 VRAM, and 256K x 16 DRAM are supported in order to permit design of different configurations. This allows ATLAS to support 8, 16, 24 and 32 bits/pixel formats and resolutions up to 1600 x 1200.

VRAM is used for the frame buffer itself. Since VRAM has two ports, the serial port of the VRAM is used for the screen refresh while the random port is devoted to drawing operations. Useful VRAM functions such as split data transfer, block mode, and write/bit are all exploited.

# **Chapter 3: Operation Modes**

This chapter explains the VGA and Power Graphic operation modes of the Matrox MGA ATLAS chip. The Power Graphic mode description contains explanations of the memory configuration, frame buffer formats, drawing operations, DMA, and initialization, configuration, and reset.

## 3.1 VGA Mode

ATLAS's VGA contains all of the functions and support logic required to implement the IBM VGA, EGA, and CGA display adapter and MDA/ Hercules graphics card standards at a register-compatible level.

Since ATLAS is register-compatible with VGA, EGA, CGA and MDA/Hercules adapters, all display modes for these adapters can be supported. As with most display adapters, a BIOS is required to configure ATLAS for each display mode.

As well as the standard control registers required by the various display adapters, ATLAS uses auxiliary registers to enable enhanced modes and emulation functions.

## 3.1.1 FlexFont

In all alphanumeric modes, **FlexFont** is an available option. When enabled, it forces the character backgrounds to a single color and allows bits **D4-D6** of the attribute byte to be used for character font selection. Up to eight character fonts can be displayed simultaneously. The character fonts are programmable and are stored in Dynamic Memory Plane 2.

## 3.1.2 Enhanced Modes

ATLAS enhances some display modes, and provides new high-resolution 256 and 16-color VGA modes.

The ATLAS chip permits high resolution VGA display modes of 640 x 400, 640 x 480, 800 x 600, or 1024x768 pixels with 256 simultaneous colors, both interlaced and non-interlaced. ATLAS also permits 16 color resolutions of up to 1024x768 interlaced and non-interlaced. Bits in the ATLAS auxiliary registers are used to enable these modes. Otherwise, the programming for these modes is similar to that for VGA modes 13h and 12h.

VGA mode 13h can be enhanced to provide up to 16 pages at 320x200 resolution with 256 colors (standard VGA supports only one page). The CPU can access two pages simultaneously, and the others are selected for access using page select bits in ATLAS's auxiliary ports. The CRTC start address register is used to select a page to display, or to scroll through all pages.

## 3.1.3 Display Adapter Support

Four modes of ATLAS VGA operation and emulation are available: VGA, EGA, CGA, and MDA/Hercules.

The VGA and EGA **CRTCs** are fully implemented and are used to perform the operations of a 6845 CRTC for the CGA and MDA/Hercules modes.

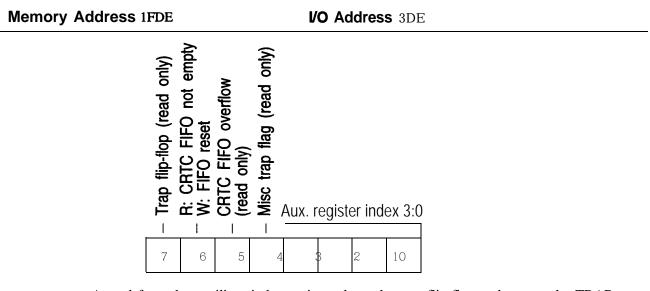

The control registers of the CGA and MDA/Hercules adapters are fully supported in the ATLAS hardware. When a control register bit is changed, a trap interrupt (NMI) is generated. The interrupt handler then interprets the control register's contents and sets up the VGA CRTC to perform the required operation. In addition, the chip can be configured to allow software emulation to override any or all of the hardware functions to permit support of special display modes.

## 3.1.4 Differences Between ATLAS Ports and IBM VGA Display Adapter Ports

There are differences between ATLAS's VGA mode and the IBM display adapters that it emulates. Some ports are changed from write-only to read/write to simplify emulation. Other ports have been deleted because they aren't required. The following subsections describe the differences.

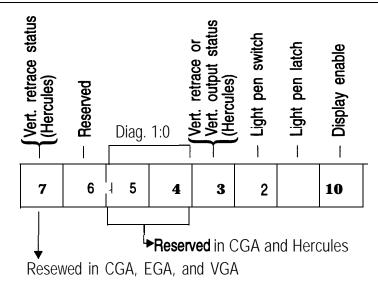

### 3.1.4.1 Hercules Mode Port Differences

The 6845 CRTC is replaced by the EGA or VGA CRTC. Hardware emulation of the 6845 requires software assistance and is enabled through the trap and emulation control registers.

The mode control and configuration registers are now read/write.

### 3.1.4.2 CGA Mode Port Differences

The 6845 CRTC is replaced by the EGA or VGA CRTC. Hardware emulation of the 6845 requires software assistance and is enabled through the trap and emulation control registers.

The mode control and color select ports are now read/write.

### 3.1.4.3 EGA Mode Port Differences

The CRTC registers are now read/write. Otherwise, the CRTC is identical to the IBM EGA CRTC when the EGA CRTC mode is selected. The VGA CRTC can be selected when ATLAS is in EGA mode.

The attributes controller registers are now read/write. The address and data registers of the sequencer and graphics controller are also read/write.

Graphics position registers A and B have been deleted and replaced by read-only ports for the feature control and miscellaneous registers. Graphics position A is fixed at 0 and B is fixed at 1, according to standard EGA programing practice.

### 3.1.4.4 VGA Mode Port Differences

In VGA mode, ATLAS is register compatible with the IBM VGA. The light pen set and clear ports remain accessible. The EGA CRTC can be selected when ATLAS is in VGA mode.

## 3.2 Power Graphic Mode

Power Graphic mode employs hardware-coded graphical acceleration to improve the speed of GUI (Graphical User Interface) environments.

## 3.2.1 Memory Configurations

Several hardware memory configurations are supported in Power Graphic mode. These configurations can further be organized by the fbm (frame buffer mode) field of the OPMODE register. The three basic configurations are:

- 1. Support of up to 2 MB of VRAM and 2 MB of DRAM using 128K x 8 VRAM. This configuration supports 8, 16, and 32 bit/pixel displays.

- 2. Support of up to 3 MB of VRAM and 2 MB of DRAM using 128K x 8 and 256K x 8 VRAM. This configuration supports 8, 16, and 32 bit/pixel displays.

- 3. Support of up to 6 MB of VRAM and 4 MB of DRAM. This configuration supports 24 or 32 bit/pixel displays. Use fbm = 1 XX, depending on the amount of available memory and whether the frame buffer is configured as 24 or 32 bits.

- :\* Note: In No DUBIC mode, only Banks 0, 1, 2, and 3 are supported. Therefore, only fbm= 0, 1, 2, and 3 may be used.

In all cases, the resolution depends on the amount of available memory. Section 6.3, 'VRAM Interface' contains tables that show which fbms can be used with which hardware configurations. The following figures show the memory mapping of the hardware memory configurations.

#### Memory Configuration Tables:

Figure 3-1: **fbm** = 0

Figure 3-6: fbm = 5

#### Notes (Figures 3-1 to 3-8):

- (1) All addresses are hexadecimal byte addresses. These addresses correspond to pixel addresses in 8 bits/pixel mode.

- (2) 'Memory Bank' indicates the type of memory used, as well as which bank of memory is used in this space. Refer to Section 6.3 for details on the frame buffer modes.

- (3) This part of the frame buffer can't be used for display.

#### Notes (continued):

- (4) Depending on the number of chips/banks populated in this section, any data, or possibly only 24-bit data may be stored in this section of memory.

- (5) Depending on the number of chips/banks populated in this section, and if bank 7 is populated, any data, or possibly only 24-bit data may be stored in this section of memory.

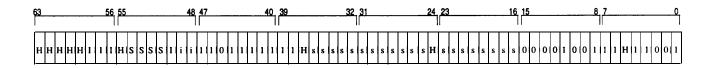

## 3.2.2 Pixel Format

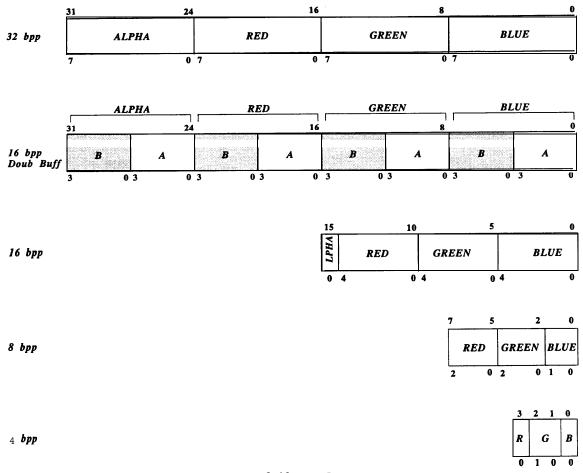

The pixel slice is 64 bits long and is organized as shown below. In all cases, the least significant bit is 0. The Alpha part of the color refers to a section of the pixel which is not used to drive the RAMDAC. In the following illustrations, 'A' refers to Buffer A and 'B' to Buffer B when a double buffer mode is selected. ANTI refers to anti-aliased pixels, and MONO is a monochrome pixel slice.

|                     | 63 60 | 56  | 52  | 48  | 44  | 40  | 36  | 32  | 28  | 24  | 20  | 16  | 12  | 8          | 4         | 0   |

|---------------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------|-----------|-----|

| 32 bpp              |       |     |     | I   | P1  |     |     |     |     |     |     | I   | 20  |            |           |     |

| 16 bpp<br>Doub Buff | PIB   | PIA | P1B | PIA | PIB | PIA | PIB | PIA | POB | POA | POB | POA | POB | POA        | POB       | POA |

| 16 bpp              | P3    |     |     |     | 1   | P   | 2   |     |     | 1   | P1  |     |     | F          | <b>PO</b> |     |

| 8 bpp<br>Doub Buff  | P:    | 3B  | P   | 3A  | P2  | B   | P   | 2A  | Pl  | 'B  | PI  | A   | Pl  | )B         | P         | DA  |

| 8 bpp               | P     | 7   | 1   | P6  | 1   | 25  | F   | 94  | P   | 3   | P   | 2   | F   | 21         | P         | 0   |

| 4 bpp<br>Doub Buff  | P7B   | P7A | P6B | P6A | P5B | P5A | P4B | P4A | P3B | P3A | P2B | P2A | PIB | PIA        | POB       | POA |

| ANTI                | P15   | P14 | P13 | P12 | P11 | P10 | P9  | P8  | P7  | P6  | P5  | P4  | P3  | <b>P</b> 2 | P1        | PO  |

| MONO                | P63   | •   |     | •   |     |     | •   | •   | •   |     | •   | •   |     |            | •         | PO  |

#### Figure 3-9: Pixel Slice

In all cases the data is true color; however in 8 bits/pixel and 4 bits/pixel formats, pseudo color can be used when shading and anti-aliasing are not used.

The following figure shows how the data is organized for each pixel (for all supported pixel depths).

When performing direct frame buffer access, 32-bit access depends on the format of the memory at this location. Data is organized as follows for the various pixel sizes:

|                     | 31 28      | 24  | 20  | 16  | 12  | 8     | 4   | 0         |  |

|---------------------|------------|-----|-----|-----|-----|-------|-----|-----------|--|

| 32 bpp              |            | 1   | I   | P   | 0   | 1<br> | I   | I <u></u> |  |

| 16 bpp<br>Doub Buff | POB        | POA | POB | POA | POB | POA   | POB | POA       |  |

| 16 bpp              |            | ŀ   | 91  |     |     | F     | 0   |           |  |

| 8 bpp<br>Doub Buff  | Pl         | B   | PI  | A   | P   | )B    | POA |           |  |

| 8 bpp               | P3 P2      |     |     | 1   | 21  | PO    |     |           |  |

| 4 bpp<br>Doub Buff  | P3B        | P3A | P2B | P2A | PIB | PIA   | POB | POA       |  |

| ANTI                | <b>P</b> 7 | P6  | P5  | P4  | P3  | P2    | P1  | PO        |  |

| MONO                | P31        |     |     |     |     |       |     | PO        |  |

Figure 3-11: 32-bit Access

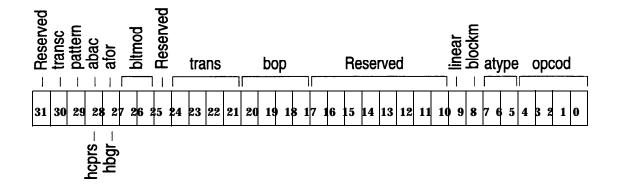

In addition to the direct **frame** buffer access format, the following formats are supported for **ILOAD** and **IDUMP** operations in 1, 24, and 32-bits/pixel modes. These formats are selected by the RGB (hbgr) and compress (hcprs) fields of the Drawing Control (DWGCTL) register:

|             | 32     | 24            | 16            | 8 0    | bltmod hbgr | hcprs |

|-------------|--------|---------------|---------------|--------|-------------|-------|

|             | As     | s direct fram | e buffer acce | 255    | BFCOL 0     | 0     |

|             | 31     |               |               | 0      | BMONO 0     | 0     |

|             | 24 31  | 16 23         | 8 15          | 0 7    | BMONO 1     | 0     |

|             | ALPHA  | BLUE          | GREEN         | RED    | BUCOL 1     | 0     |

|             |        |               | UNLLIV        |        | 20002 1     | -     |

| First Word  | RED1   | BLUEO         | GREEN0        | RED0   | BUCOL 1     | 1     |

| Second Word | GREEN2 | RED2          | BLUE1         | GREENI |             |       |

| Second Word | BLUE3  | GREEN3        | RED3          | BLUE3  |             |       |

|             |        | 1             | 1             | 1      | i           |       |

|             | ALPHA  | BLUE          | GREEN         | RED    | BUCOL 0     | 0     |

| First Word  | BLUEI  | RED0          | GREEN0        | BLUE0  | BUCOL 0     | 1     |

| Second Word | GREEN2 | BLUE2         | REDI          | GREENI |             |       |

| Third Word  | RED3   | GREEN3        | BLUE3         | RED2   |             |       |

Figure 3-12: ILOAD/IDUMP Formats /1, 24, 32 bpp

## 3.2.3 Overview of Drawing Operations

The following three groups of drawing operations are supported by ATLAS:

- LINE: Used for vectors. These operations can be auto-initialized. In this case, the Brezenham parameters are **automaticaly** computed by ATLAS. Brezenham parameters can also be provided directly by the host processor.

- TRAP: Used for rectangle fills (1 operand BITBLTs) and polygon drawing.

- BITBLT: Used for copy and other operations (2 operand BITBLTs with or without expansion).

All of these drawing operations support several attributes in order to perform different type of actions. The attributes include: line style, patterning, block mode, raster, anti-aliasing, and others.

The following table summarizes how the drawing engine registers must be initialized for these basic operations:

|        |       | REGISTERS |          |        |     |      |        |       |        |              |

|--------|-------|-----------|----------|--------|-----|------|--------|-------|--------|--------------|

|        |       |           |          |        |     |      |        |       |        |              |

| opcode | event | ar0       | ar 1     | ar2    | ar3 | ar4  | ar5    | ar6   | length | SGN          |

| AUTO   | INIT  | Xend      |          | Yend   |     |      | Xstar  | Ystar |        |              |

| LINE   | END   | 2b        | err      | 2b-2a  |     |      | Xend   | Yend  | 0      | <u>signs</u> |

| LINE   | INIT  | 2b        | 2b-a-Sdy | 2b-2a  |     |      |        |       | а      | signs        |

| DRAW   | END   | 2b        | err      | 2b-2a  |     |      |        |       | 0      | signs        |

| TRAP   | INIT  | dY1       | eol      | -ldX1l |     | eor  | -ldXrl | dYr   | lines  | signs        |

|        | END   | dY1       | err1     | -ldX1l |     | errr | -ldXrl | dYr   | 0      | signs        |

| BITBLT | INIT  | sea       | ssa      |        | sca |      | syinc  |       | lines  | signs        |

|        | END   | X         | X        |        | X   |      | syinc  |       | 0      | signs        |

dX = Xend - Xstart dY = Yend - Ystart a = max( |dx|, |dy|)b = min( |dx|, |dy|) eor =  $dX_r \ge 0$ ? -  $dX_r : dX_r + dY_r - 1$ eol =  $dX_l \ge 0$ ? -  $dX_l : dX_l + dY_l - 1$ Where  $x_l$  = left edge;  $x_r$  = right edge sea = source and address ssa = source start address sca = source current address

### Table 3-1: Initialization of Drawing Registers

Every time a drawing engine operation is started, the following steps must be taken:

- 1. Since all drawing registers are accessed through the FIFO, check that there is enough room in the FIFO.

- 2. Initialize all the drawing registers, preferably starting with the 'K' flag register (see Note (2) following Table 4-4), since some degree of parallelism can be achieved doing this.

- 3. Start the drawing engine when you write the last register by offsetting the register by 100h.

### 3.2.4 DMA and Pseudo DMA

ATLAS supports two operating modes in which both the address and data are sent via the data bus:

**DMA** A DMA channel on the host system is used to sequence operations (ISA interface only).

**Pseudo DMA** The host processor must sequence all access through the DMAWIN memory space (ISA and PCI interface).

In both cases, the address of the modified register is generated internally by the ATLAS chip. Additional operation modes are available for both DMA and Pseudo DMA:

| DMA                       | Pseudo DMA                |

|---------------------------|---------------------------|

| DMA General Purpose Write | DMA General Purpose Write |

| DMA Vector Write          | DMA Vector Write          |

| DMA BLIT Write            | DMA BLIT Write            |

|                           | DMA BLIT Read             |

#### **DMA General Purpose Write**

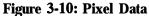

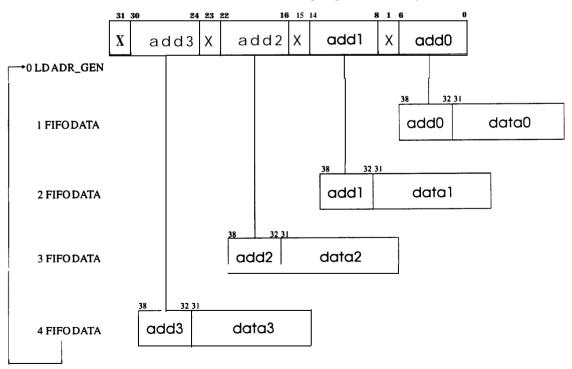

The first double word (dw) transferred is loaded into the Address Generator. This dw contains the addresses of the next four drawing registers to be written, and the next four dw transfers contain the data to be written to those four registers.

When each dw of data is transferred, the Address Generator will send the appropriate 7-bit address to the Bus FIFO. When the fourth (final) address has been used, the next double word transfer reloads the Address Generator.

A direct access to a drawing register during a Pseudo DMA General Purpose write resets the Address Generator state machine to the 'LD **ADR\_GEN**' state. The following Pseudo DMA write transfer must contain the addresses of the data for the next four drawing registers. The cycle is illustrated below.

Figure 3-13: DMA General Purpose Write Sequence

Figure 3-14: DMA Gen. Purpose Transfer Buffer Structure

### DMA Vector Write

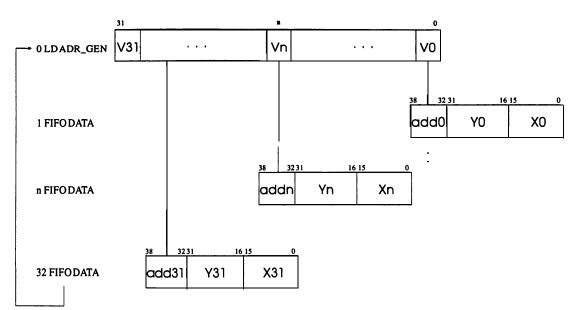

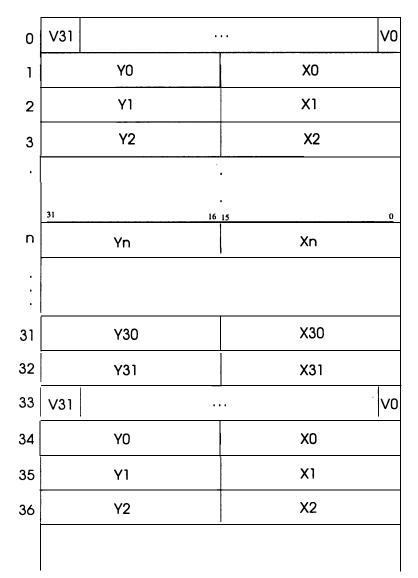

The first double word transferred is loaded into the Address Generator. This dw contains one bit of 'address select' for each of the next 32 vector vertices to be sent to the drawing registers. These 32 bits are called the vector tags. The next 32 double word transfers contain the XY address data to be written to the drawing registers.

When the tag bit is set to zero (0), the address generator will force the address to that of the XYStart register without setting the bit to start the drawing engine. When the tag bit is set to one (1), the address generator will force the address to that of the XYEnd register with the flag set to start the drawing engine.

When each dw of data is transferred, the Address Generator checks the associated tag bit and sends the appropriate 7-bit address to the Bus FIFO. When the  $32^{nd}$  (final) tag has been used, the next double word transfer reloads the Address Generator with the next 32 vector tags.

A direct access to a drawing register during a Pseudo DMA VECTOR resets the Address Generator state machine to the 'LD ADR\_GEN' state. The following Pseudo DMA write transfer must contain the vector tags for the next XY coordinate data.

The cycle is illustrated on the next page.

When Vn = 0, addn = XY\_START address (10h)

When Vn = 1,  $addn = XY\_END address + START DWG ENG (51h)$

Figure 3-15: DMA Vector Sequence

Figure 3-16: DMA Vector Transfer Buffer Structure

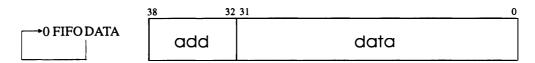

#### **DMA BLIT Write**

The DMA BLIT write is hard coded, so there's no reason to load the Address Generator. The result is that every transfer consists of data to be transferred.

When each dw of data is transferred, the Address Generator sends the srcregblit register address to the Bus FIFO. The address generator state machine is not used for this type of DMA.

All pixels expected by the drawing engine must be transferred, otherwise it could jam. The total number of dword transfers needed to complete the BLIT operation depends on, among other factors:

- The size of the window to be drawn (upper left comer coordinate, length in X and Y)

- The number of bits per pixel (8, 16, or 32)

The cycle is illustrated below. No address is required for data transfer during DMA blits, so 'add' is 'don't care'.

Figure 3-17: DMA BLIT Write Sequence

Figure 3-18: DMA BLIT Write Transfer Buffer Structure

## **DMA BLIT Read**

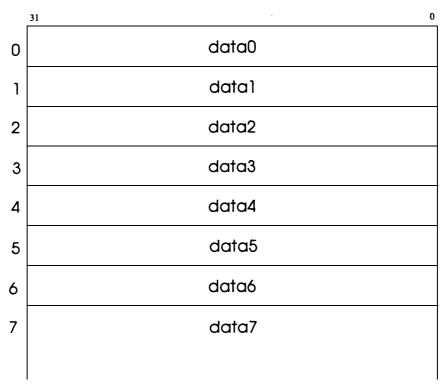

As specified earlier, the DMA BLIT Read mode is available for Pseudo DMA only, and is used to dump pixels from a window of the screen to system memory. Each double word that's transferred may contain 4, 2, or 1 pixel(s), depending on the configuration (8, 16, or 32 bits per pixel, respectively).

The coordinate of the upper left comer and the length in X and Y are a few of the parameters that are required by the graphic engine for this operation.

### A Important Note:

It is **extremely important** that the number of dwords dumped accounts for all of the pixels that are to be transferred. The last dword for **each scan line of pixels** may contain insignificant information in the case of 8 or 16 bit/pixel modes if the number of transferred pixels is not evenly divisible by 4 (for 8 bpp modes) or by 2 (for 16 bpp modes).

If the window to be drawn is not aligned at the beginning of a slice, the insignificant pixels to the left of the window are effectively disregarded, and the slice alignment begins at the start of the window.

|             | Slice O<br>Boundary |    |    | Slice 1 |    |   |   |   |             |     | Slice 10 |     |     |   |   |

|-------------|---------------------|----|----|---------|----|---|---|---|-------------|-----|----------|-----|-----|---|---|

| Scan line O | <b>P</b> 0          | P1 | P2 | P3      | P4 | • | • | • | <b>P</b> 37 | P38 | P39      | P40 | P41 | x | x |

| Scan line 1 | PO                  | P1 | P2 | P3      | P4 | • | • | • | P37         | P38 | P39      | P40 | P41 | x | x |

The following illustration shows the case of an 8 bits/pixel mode transfer that is 42 pixels wide:

### 3.2.4.1 DMA

\* The ATLAS chip's DMA capabilities can only be used with the AT (ISA) interface.

ATLAS supports only DMA I/O write transfers. The goal is use the host's DMA controller to transfer a block from the system memory into ATLAS's Bus IWO (only the Bus FIFO is accessed during DMA write). This provides a means to write to drawing registers for specific drawing operations.

Only **16-bit** DMA transfers are supported. The total number of transfers must be an integral number of double words, to align with ATLAS's internal 32-bit data bus. The words are accumulated before sending double words to the Bus FIFO. The memory block to be transferred must be aligned on a double word boundary.

| Timing Type       | Mode   | Data Size | System   |

|-------------------|--------|-----------|----------|

| ISA<br>Compatible | Single | 16        | ISA/EISA |

| Type 'B'          | Single | 16        | EISA     |

|                   | Demand | 16        | EISA     |

#### Table 3-2: DMA Access Types

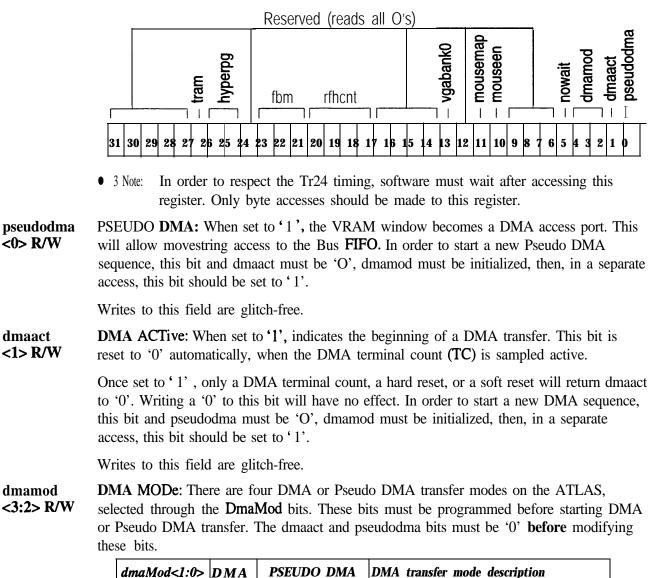

To initiate a DMA transfer, take the following steps:

- 1. Ensure that 'dmaact' and 'pseudodma' (OPMODE register bits 1 and 0) are not active (active if '1').

- 2. Program the dmamod bits (OPMODE register bits 2 and 3) to one of three modes listed below (keep dmaact and pseudodma at '0'):

- DMA General Purpose Write

- DMA BLIT Write

- DMA Vector Write

The function of the dmamod bits is explained later on.

- 3. Program the host DMA controller.

- 4. Start the DMA transfer by setting dmaact to '1' (keep pseudodma at '0').

Once dmaact is set, ATLAS will request DMA service by asserting DRQ. The requests will continue until the terminal count is reached. If the Bus FIFO becomes full during the DMA transfer, the request will stop automatically and resume when there is space available in the Bus FIFO.

When the DMA transfer is in progress, any access to the following devices is forbidden:

- The drawing registers (offset 1C00h -1DFFh)

- VRAMWIN (offset 0000h 1BFFh, vgaen = '0' and pseudodma = '0' see Chapter 4)

- DMAWIN (offset 0000h 1BFFh, vgaen = '0' and pseudodma = '1')

Access to other MGA resources is still possible, however.

Dmaact will be automatically reset after the last transfer, when the DMA terminal count (TC) is sampled active.

DRQ is normally tri-state. When dmaact is active, DRQ is driven to the appropriate state. This allows for resource sharing in a system with multiple **MGAs**. Only one MGA can have dmaact active at any time. When dmaact becomes inactive due to TC, ATLAS will have been driving DRQ low, then it will tri-state the signal.

It's possible to generate an interrupt when a DMA terminal count occurs. For more information, refer to Section 3.2.6.

#### 3.2.4.2 Pseudo DMA

The goal of Pseudo DMA is the same as that of DMA, with the only difference being that read transfers are possible. Instead of using the DMA controller, Pseudo DMA transfers are 'move string' instructions in the DMAWIN memory space (offset 0000h - 1BFFh, vgaen = '0' and pseudodma = '1').

Only double word accesses (read or write) are allowed in the DMAWIN memory space. When performing Pseudo DMA transfers, all of the MGA map is available, except the VRAMWIN memory space, which is disabled.

#### Write Transfers

To transfer a block of data from the system memory to the Bus FIFO of the ATLAS chip, the steps listed below must be followed:

- 1. Make sure that 'dmaact' and 'pseudodma' are not active.

- 2. Program the dmamod bits to one of the three modes listed below (keep dmaact and pseudodma at '0'):

- DMA General Purpose Write

- DMA BLIT Write

- DMA Vector Write

a) If DMA BLIT Write is used, program all affected drawing registers. Note that all writes to the drawing registers must be double word accesses.

- b) If DMA BLIT Write is used, send the **ILOAD** opcode to the drawing engine.

- 3. Set 'pseudodma' to '1' (keep dmaact at '0').

- 4. Transfer system memory data to the MGA DMAWIN memory space, with 'move string' or 'read and write' instructions.

- 5. Reset 'pseudodma' to '0' at the end of the block transfer.

As long as the Bus FIFO isn't full, and if the **nowait** bit of the OPMODE register is set to '1', then no wait will be generated for write cycles to the DMAWIN memory space. When the Bus FIFO is full, there is one more dword location, which is the Byte Accumulator of the host section. Once the Byte Accumulator and the Bus FIFO are full, the next write to the DMAWIN space will be put in waiting as long as the Byte Accumulator data isn't loaded in the Bus FIFO.

If the CHRDY ready signal is kept inactive for more than 64 gclks, the STATUS register bferrsts bit will be set. This will cause an interrupt if the proper interrupt enable is set. If CHRDY is still inactive after 128 gclks, the host section will abort the write cycle by reasserting CHRDY and by resetting the Byte Accumulator full flag.

For DMA BLIT Write operations, the drawing engine will fetch data until all pixels have been loaded, once the **ILOAD** opcode is sent, and if the Bus FIFO isn't empty.

#### **Read Transfers**

To dump screen data to the system memory, take these steps:

- 1. Make sure that 'dmaact' and 'pseudodma' are not active.

- 2. Program the dmamod bits to DMA BLIT Read (keep dmaact and pseudodma at '0').

- 3. Program all affected drawing registers. Note that all writes to the drawing registers must be double word accesses.

- 4. Set 'pseudodma' to '1' (keep dmaact at '0').

- 5. Send the **IDUMP** opcode to the drawing engine.

- 6. Transfer data from the DMAWIN memory space to the system memory, with 'move string' or 'read and write' instructions.

- 7. Reset 'pseudodma' to '0' at the end of the dump.

Once the **IDUMP** opcode is sent to the drawing engine, it begins fetching pixels from the **VRAMs**. During a read in the DMAWIN memory space, CHRDY will be deactivated (ISA bus system), or a retry will be generated (PCI bus system) if the data from the drawing engine isn't ready. When the data is available, it will be latched in the host section of ATLAS, and the access is completed. A new request will be sent to the drawing engine for the next dword when the last byte, the last word, or the current dword is being read, depending on whether ATLAS is 8, 16, or 32-bit. The latched dword will be present until all bytes are read.

If an access takes more than 64 gclks, the bferrsts bit will be set in the STATUS register. This may cause an interrupt if the proper interrupt enable is set. If an access takes more than 128 gclks, the host section will abort the read cycle.

# 3.2.5 Programming the CRTC for Power Graphic Mode

This section explains the video parameters required for the Power Graphic display modes.

#### 3.2.5.1 Registers

In Power Graphic mode (for all resolutions and pixel depths), the video parameters that are programmed in the registers are **always** based on a video clock that is divided by 8.

• :\* Note: When you change any video parameters, it is important to halt the video operation circuitry of the VRAM chips to prevent the **VRAMs** from entering an unrecoverable state. The 'Screen Off' bit in the Clocking Mode sequencer register (Address 1FC5, Index 01, Bit 5) will force the screen to blank and halt the VRAM circuitry mentioned above. This bit must be maintained to 'off' for at least 10 µs after the last video parameter modification.

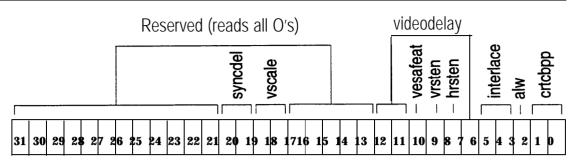

The CRTC\_CTRL register is used as specified. Table 3-3 shows the registers that are implicated in programming the video for the Power Graphic modes.

#### 3.2.5.2 Interlace Modes

In Power Graphic mode, the hardware can only be properly programmed in interlace modes at specific memory pitches (768, 1024, and 1280). For other pitches, the hardware must be programmed in such a way that the display area is less than the memory pitch.

It is not possible to have a horizontal resolution greater than 1280 pixels in interlace mode.

#### 3.2.5.3 Hardware Panning

Panning is achieved by programming a start address that is equivalent to the desired region. The start address is programmed in two VGA CRTC registers and one auxiliary register. Panning must be done on a multiple of 16 pixels.

#### 3.2.5.4 Hardware Zooming

Zooming by lx, 2x, and 4x is supported.

Zooming in the X direction is performed by the clock generator. For the CRTC, this is seen simply as a division of the video clock. However, the CRTC registers that control the horizontal signals must be reprogrammed properly (relative to the divided clock) to deliver the same frequency to the monitor.

It's important to note that if you wish to maintain a constant image between each zoom switch, the horizontal parameters must be exact multiples. For this reason, multiples of 32 must be used for each parameter (front porch, sync, etc.), even if you zoom by lx.

To zoom in the Y direction, you must reprogram the Maximum Scan Line register in the CRTC. This will affect the way that the CRTC address counter generates line addresses.

The dt request module must also operate in non-automatic line wrap mode (refer to Bit 2 of the CRTC\_CTRL Power Graphic mode register description on page 5-53) when not zooming by **1x.**

## 3.2.5.5 Programming Constraints

In order to have a correct image on the screen, you must respect different constraints when calculating the video parameters. The videodelay field of the CRTC\_CTRL register can be programmed for 3, 4, 5, 11, 24, or 28 videlks. The video parameters must be calculated so that at least one of the six possible values of videodelay meets the three constraints. Unexpected video results could occur otherwise.'

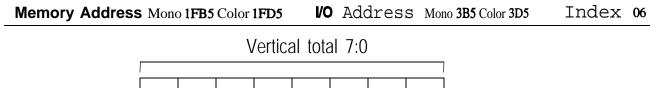

| Section      | Index Name                        | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|--------------|-----------------------------------|----|----|----|----|----|----|----|----|

| <b>C</b> RTC | 00 Horizontal Total               | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 01 Horizontal Display Enable End  | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 02 Horizontal Blanking Start      | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 03 Horizontal Blanking End        | 0  | 0  | 0  | S  | S  | S  | S  | S  |

|              | 04 Horizontal Retrace Start       | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 05 Horizontal Retrace End         | S  | 0  | 0  | S  | S  | S  | S  | S  |

|              | 06 Vertical Total                 | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 07 Overflow                       | S  | S  | S  | 1  | S  | S  | S  | S  |

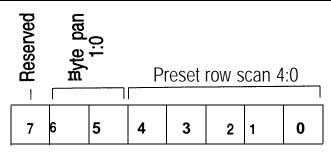

|              | 08 Preset Row Scan                | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|              | 09 Maximum Scan Line              | 0  | 1  | S  | Ζ  | Ζ  | Ζ  | Ζ  | Ζ  |

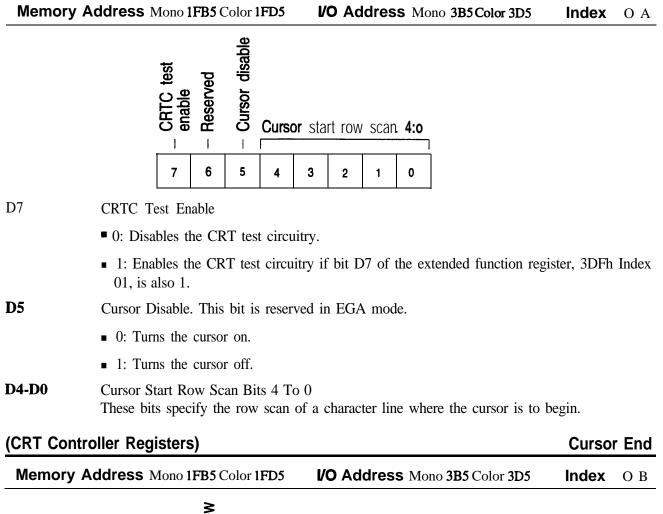

|              | 0A Cursor Start                   | 0  | 0  | 1  | Х  | Х  | Х  | Х  | Х  |

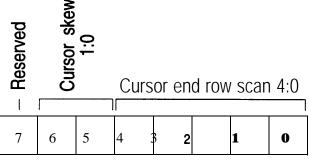

|              | 0B Cursor End                     | 0  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

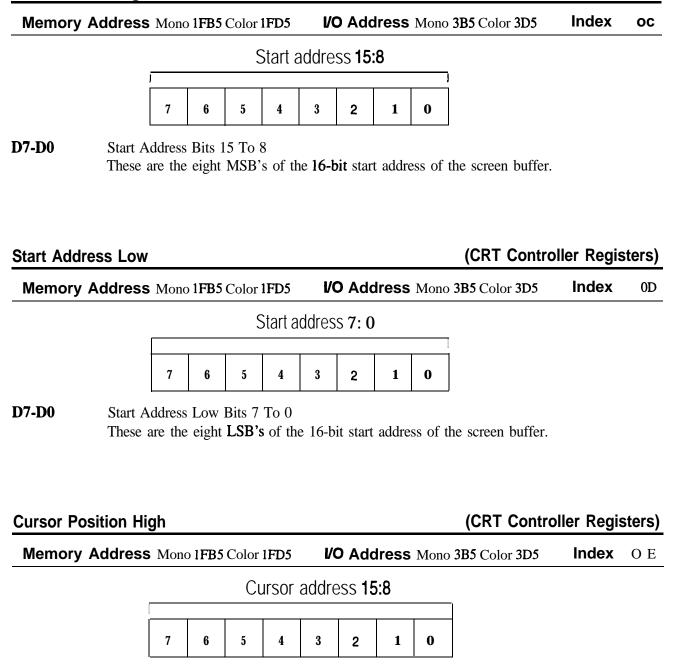

|              | OC Start Address High             | S  | S  | S  | S  | S  | S  | S  | S  |

|              | OD Start Address Low              | S  | S  | S  | S  | S  | S  | S  | S  |

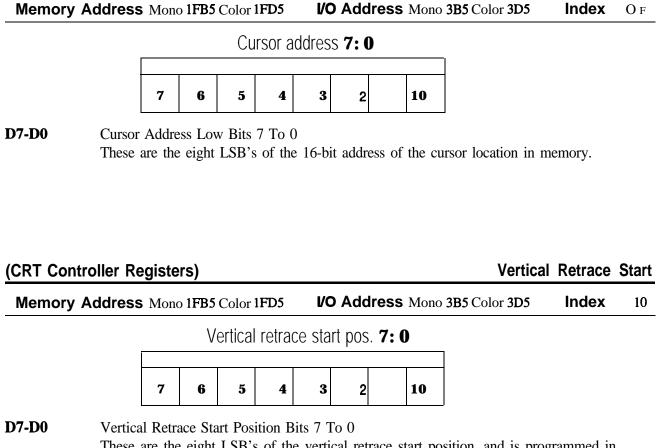

|              | OE Cursor Position High           | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

|              | OF Cursor Position Low            | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |

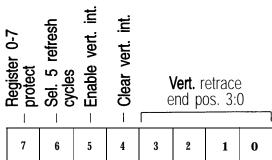

|              | 10 Vertical Retrace Start         | S  | S  | S  | S  | S  | S  | S  | S  |

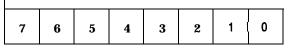

|              | 11 Vertical Retrace End           | S  | Х  | S  | S  | S  | S  | S  | S  |

|              | 12 Vertical Display Enable End    | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 13 Offset                         | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 14 Underline Location             | 0  | 0  | 0  | Х  | Х  | Х  | Х  | Х  |

|              | 15 Vertical Blanking Start        | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 16 Vertical Blanking End          | S  | S  | S  | S  | S  | S  | S  | S  |

|              | 17 Mode Control                   | S  | Х  | Х  | 0  | 0  | S  | Х  | Х  |

|              | 18 Line Compare                   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| AUX          | 00 Mode Control Register          | х  | х  | Х  | 0  | 0  | 0  | 0  | 0  |

|              | 02 Emulation Control Register     | 0  | х  | Х  | х  | х  | х  | Х  | Х  |

|              | OA CRTC Extended Address Register | S  | х  | Х  | 1  | х  | Х  | S  | S  |

|              | OD Interlace Support Register     | х  | S  | Х  | Х  | х  | х  | х  | Х  |

|              | OE Vertical Sync Adjust Register  | s  | S  | S  | S  | S  | S  | S  | S  |

| SEQ          | 01 Clocking Mode                  | х  | х  | S  | Х  | Х  | х  | Х  | Х  |

|              | Miscellaneous Output Register     | 1  | 1  | Х  | 0  | S  | S  | Х  | S  |

#### Legend: 0 The bit must always be programmed to 0

- 1 The bit must always be programmed to 1

- X The bit can be programmed to either 0 or 1

- S The bit works as specified

- Z The bit is used by the zoom in the Y direction

#### Table 3-3: Power Graphic Mode Video Registers

The following formula explains how to calculate the three constraints. The drawing engine response (in video clocks) is:

$dw_eng_res = \frac{int(925ns*videofrequency+0.9)}{8}$

Constraint #1: Videodelay >= Horizontal FrontPorch+2-3

Constraint **#2:** Videodelay >=  $dw_eng_res+l-1^{3}/_{8}$

Constraint **#3:** Videodelay **=<** *Horizontal blank+l-dw\_eng\_res-3*

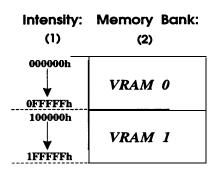

#### 3.2.5.6 Frame Buffer Alignment

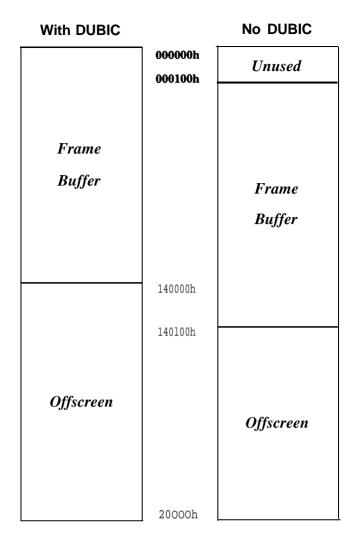

When 'No DUBIC' mode is selected, the frame buffer display must be arranged in such a way that bank switching appends during the blank (between two lines).

#### For example:

Assume that we want to display 1280x1024x8 using two **1MB** banks. The bank transition occurs after **1M** pixels:

1048576 / 1280 = 819.2 pixels pixels/line lines

Round this up to 819 lines, and up-front padding will have to be added in order to ensure that the bank transition takes place between two lines:

| pixels  |   | pixels/line |   | lines |   | pixels |

|---------|---|-------------|---|-------|---|--------|

| 1048576 | - | (1280       | * | 819)  | = | 256    |

This means that the frame buffer will have to be started at address 256 (rather than at address 0). This produces the following results:

- The CRTC start address must be 256, rather than 0.

- The drawing operation must be moved by 256 pixels. This can be done automatically by the drawing engine for the destination address by initializing YDSTORG to 256. Note that this will affect the value loaded in CYBOT and CYTOP. For source addresses this adjustment will have to be done manually.

- Off-screen memory is reduced by 256 bytes.

Figure 3-19: Memory Org. (1280x1024x8 - two 1M Banks)

#### 3.2.5.7 **Overscan**

The hardware can support the **overscan** feature, but using it will reduce the length of the blank period. This reduced blank will have a direct impact on your ability to meet the constraints of the video delay. It might be possible to lose the zoom feature at low resolutions, or even the integrity of the display itself if the **overscan** is large.

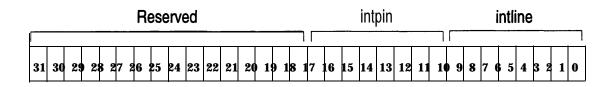

# 3.2.6 Interrupts

ATLAS supports interrupts for both ISA and PCI configurations.

• In the ISA configuration, ATLAS can generate two types of interrupts: edge interrupts, and level interrupts. The choice of interrupts is system-dependent, and is programmed by the **CONFIG** register's leveling bit. In the Power Graphic modes, several interrupt sources exist:

| Interrupt                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus FIFO Error Interrupt | This interrupt is generated when a cycle is aborted.<br>It is useful during software debugging and testing.                                                                                                                                                                                                                                                                                                                                                                                                                |

| DMA TC Interrupt         | This interrupt is generated when a terminal count occurred at the end of a DMA transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Picking Interrupt        | This interrupt is generated when a pixel is written<br>by the drawing engine.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vertical Sync Interrupt  | This interrupt is generated at every vertical sync.<br><b>Note:</b><br>The vertical sync interrupt behaves differently than<br>the others, because two other bits must be set for it<br>to be enabled. Bit 7 of the AUX_DATA register,<br>and Bit 5 of the Vertical Retrace End register<br>(IFB5/1FD5, Index 11) must be set before the<br>vertical sync interrupt can be enabled.<br><b>Note:</b><br>This interrupt must be cleared by accessing Bit 4 of<br>the Vertical Retrace End register (IFB5/IFD5,<br>Index 11). |

#### **Table 3-4: Interrupt Sources**

• In the PCI configuration, ATLAS uses only one interrupt line (INTA), and is a single function device. In order to integrate the DUBIC interrupts, the other external interrupts, and the current TITAN interrupt, a new register has been added.

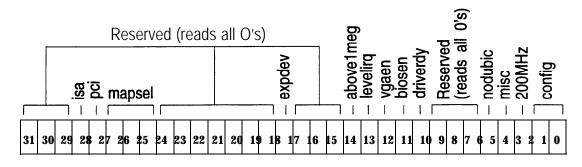

In the PCI configuration, the interrupts must be programmed as level interrupts (levelirq) in the **CONFIG** register.

Three registers are used for interrupt control:

- **STATUS** This register indicates the status of each of the interrupt sources.

- **IEN** This register is used to individually enable each of the four interrupt sources.

- **ICLEAR** This register is used to individually reset each of the four interrupt sources. Note that there is no bit in this register to clear the vertical sync interrupt, which is cleared by accessing Bit 4 of the Vertical Retrace End register (IFB5/IFD5, Index 11).

# 3.3 Access Restrictions to Some Resources

Consideration must be given to several resource access restrictions (which vary depending on how the ATLAS chip is used in a system). Refer to the information on bus sizing in Sections 6.2.1.3 and 6.2.2.1.

# 3.4 Initialization and Configuration

# **3.4.1 Configuration Elements**

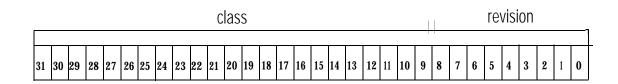

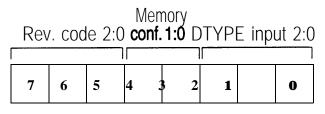

Note: In the lists which follow, H indicates that a field is hard-reset. All others are soft-reset. When MGA is powered up, ATLAS's **DSTx** registers are loaded with the following configuration elements:

| pcbrev<3:0>  | rambank<8:0> | ramspeed<1:0> | expdev |

|--------------|--------------|---------------|--------|

| product<3:0> | vgabank0     | hyperpg<1:O>  | tram   |

As well, ATLAS's host interface section receives these configuration elements:

| <i>H</i> config<1:0> | <i>H</i> vgaen        | <b>H</b> above lmeg         | H | poseidon | H | vbank0 |

|----------------------|-----------------------|-----------------------------|---|----------|---|--------|

| H driverdy           | H biosen (indirectly, | <b><i>H</i></b> mapsel<2:0> | H | isa      |   |        |

|                      | according to vgaen)   |                             |   |          |   |        |

The following configuration elements are not programmed at power up:

| ATLAS drawing en   | ngine:      |                      |                 |            |

|--------------------|-------------|----------------------|-----------------|------------|

| mctlwtst (RO)      |             |                      |                 |            |

| ATLAS host interfa | ace:        |                      |                 |            |

| ien<3:0>           | H mouseen   | hyperpg <l:o>*</l:o> | interlace<1:O>  | H vesafeat |

| H levelirq         | H mousemap  | tram*                | videodelay<1:0> |            |

| expdev*            | rfhcnt<3:0> | crtcbpp<1:0>         | H hrsten        |            |

| H nowait           | fbm<2:0>    | alw                  | <i>H</i> vrsten |            |

|                    |             |                      |                 |            |

\* Value available in DST0

#### 3.4.2 Booting in VGA Mode

The following configuration elements from the ATLAS host interface affect the VGA, and are not programmed at power up. All the other elements are VGA-standard, and are taken care of by the BIOS.

H levelirq H vesafeat H hrsten H vrsten

# 3.4.3 Booting in Power Graphic Mode

The following operations take place during the Power Graphic mode boot procedure:

- 1. In a PCI system, the PCI Configuration Space is initialized by the system booting procedure.

- 2. The card is detected

- 3. Configuration straps/switches are read

- 4. Depending on the configuration information and the selected hardware mode, the following non-initialized configuration elements must be programmed at power up:

| ATLAS host interface               | RAMDAC    |

|------------------------------------|-----------|

| ATLAS drawing engine               | CLOCK GEN |

| Video Interface (DUBIC if present) | VGA-CRTC  |

# 3.5 Mode Switching

# 3.5.1 Switching From VGA Mode to Power Graphic Mode

If the system has no DUBIC, disregard any step that mentions the DUBIC chip.

- 1. Make a call to the BIOS to select VGA Mode 3.

- 2. Disable VGA Mode.

- Once the VGA has been disabled, reset the vgaen bits in ATLAS's CONFIG register.

- 3. Disable interrupts from DUBIC.

- Note: If you'll be returning to Power Graphic mode later, make a note of the current value of DUBIC's DUB\_SEL register.

- Set DUBIC's DUB\_SEL register to 40h.

- 4. Stop the enhanced mode sequencer.

- Set the softreset bit in ATLAS's RESET register, then wait 1.5 µsec.

- 5. Set DUBIC to Power Graphic mode.

- Reset the blankdel and vga\_en bits in DUBIC's DUB\_CTL register.

- 6. Restart the Power Graphic sequencer.

- Reset the softreset bit in ATLAS's RESET register, then wait 1.5 µsec.

- 7. Restore the value of the DUB\_SEL register of the DUBIC.

- 8. Restart Initialization of Power Graphic mode.

# 3.5.2 Switching From Power Graphic Mode to VGA Mode

If the system has no DUBIC, disregard any step that mentions the DUBIC chip.

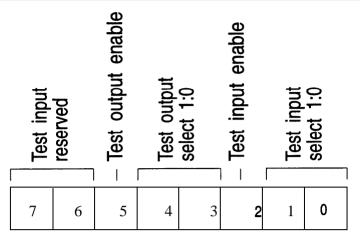

1. Place the card in ISA mode if it's currently in WIDEISA mode.

- If the isa bit in ATLAS's **CONFIG** register is 0:

- Unlock access to the **isa** bit by writing 1000 1101 b to the MSB byte in ATLAS's TEST register.

- Set the isa bit in ATLAS's **CONFIG** register.

- Lock access to the **isa** bit.

- 2. Disable the interrupts from DUBIC.

Note : If you'll be returning to Power Graphic mode later, make a note of the current value of DUBIC's DUB\_SEL register.

- Set DUBIC's DUB\_SEL register to 40h.

- 3. Stop the Power Graphic sequencer.

- Set the softreset bit in ATLAS's RESET register, then wait 1.5 µsec.

- 4. Place DUBIC in VGA mode.

- Set the state bit in DUBIC's DUB\_CTL register. If the bus mouse is enabled, set SRATE = 18. If the laser printer port is enabled, set SRATE = 2

- Set the blankdel and vga\_en bits of DUBIC's DUB\_CTL register.

- 5. Restart the Power Graphic mode sequencer.

- Reset the softreset bit in ATLAS's RESET register, then wait 1.5 µsec.

- 6. Place the RAMDAC in VGA mode. Program the appropriate registers as shown below:

#### For the **BT485** RAMDAC:

Command register  $0 = 0000 \ 0000 \ b$

Command register  $1 = 0000 \ 0000 \ b$

Command register  $2 = 0000 \ 0000 \ b$

Command register  $3 = 0000 \ 0000 \ b$

#### For the BT482 RAMDAC:

Command register  $A = 0000 \ 0000 \ b$

Command register B = 0001 1110 b

Command register C = 0000 0000 b

- 7. Program the LookUp Table (LUT) for VGA

- 8. Activate VGA Mode

- Set the vgaen and biosen bits of ATLAS's CONFIG register.

- 9. Restore the value of DUBIC's DUB\_SEL register.

- 10. Make a call to the BIOS to select a VGA mode (for example: Mode 3 for text).

# 3.6 Power up and Reset

It's possible to reset ATLAS with a hard or **soft** reset. Both methods are explained in the following subsections.

# 3.6.1 Hard Reset

A hard reset results when a low pulse is applied to the reset pin of the ATLAS chip. The minimum pulse width required is 8 µs.

On a hard reset, the following resources are reset:

- VGA section

- Drawing engine

- Bus FIFO

- Host section

- All registers

As well, external configurations are loaded into registers, as appropriate.

Three rules must be followed for proper chip reset:

- 1. In the PCI configuration, no host access must occur within the first two PCLKs of a hard reset.

- 2. LDCLK, GCLK, and PCLK must be active during reset.

- 3. You must ensure that a PLL or clock oscillator oscillates within specifications when the power-up reset ends.

# 3.6.2 Soft Reset

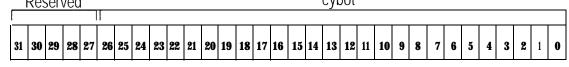

A soft reset results when bit 0 of the RESET register is set to '1', then reset to '0'. On a soft reset, external strapping is not loaded.