# Mpact™R Media Processor

# **Preliminary Data Sheet**

# **Features**

The new Mpact R media processor with a higher clock rate and an integrated display RAMDAC, continues to keep the Mpact product line the complete PC multimedia solution with the highest performance, integration and flexibility, and the lowest total cost.

- Complete

- A total hardware solution for all multimedia ports: display monitor, audio, telephone, video and joystick/MIDI

- Integrated software for all major multimedia functions on an x86 Windows 95 PC

- High Performance

- Very Long Instruction Word (VLIW) processor with 3.6 billion operations per second peak in the Mpact R/3600 version

- 5 concurrent I/O and memory controllers

- 132 MB/s PCI bus mastering interface

- Concurrent operation with MRK multitasking real-time kernel

- Dynamically shared processing with x86 host for highest total system efficiency using the MRM resource manager

- Flexible

- Loadable mediaware modules provide the latest multimedia functionality using evolving APIs and operating system standards, while retaining the same hardware

- Software programmable hardware interfaces support today's popular displays, video encoders and decoders, and audio and modem codecs, while allowing future I/O device requirements to be met

- Low Cost

- High integration interfaces require minimal support circuitry

- Internal 24-bit true-color display RAMDAC

- A single low-cost 2-Mbyte Rambus DRAM needed for normal operation

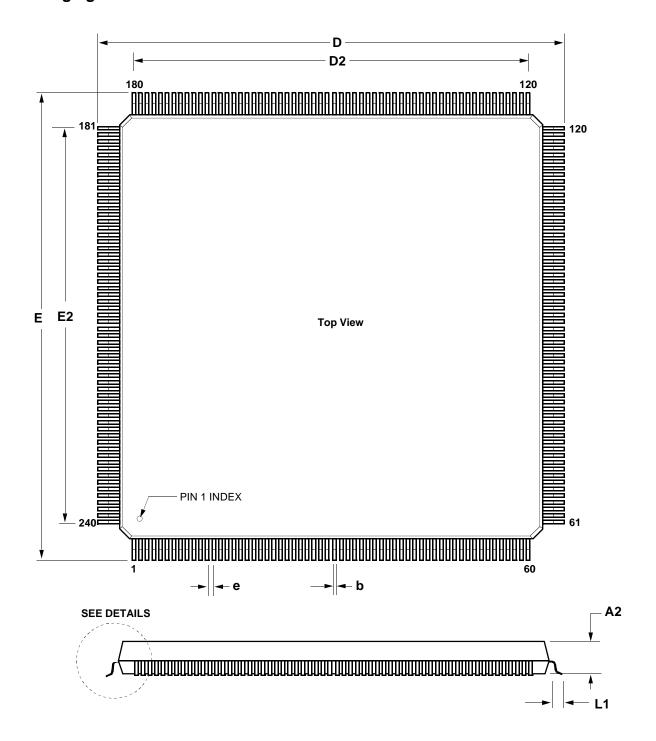

- Small footprint 240-pin HQFP package

# **Description**

An Mpact media processor is a high performance coprocessor for Windows 95 based PCs. Loaded with Mpact mediaware modules, the media processor adds or enhances support for all seven multimedia functions:

- Video: MPEG-1 & -2 decode, MPEG-1 encode

- 2D graphics: Full VGA, SVGA support, acceleration of video playback and GUI through GDI and DirectDraw

- 3D graphics: Full 3D acceleration through Direct3D

- Digital Audio: Industry-standard Sound Card compatibility, 3D Audio (SRS) and 3D positional audio effects (DirectSound), Dolby AC-3™ and MPEG-1 decode and Wave Table and Waveguide synthesis

- Fax/modem: Data up to 33.6 kb/s, fax up to 14.4 kb/s and DSVD (Digital Simultaneous Voice and Data)

- Telephony: Full-duplex speakerphone, Voicemail and caller ID

- Videophone: H.324 over POTS and H.320 over ISDN

An Mpact media processor uses an optimized real-time multitasking kernel to simultaneously execute these Mpact mediaware modules. The kernel allows, for example, 2D and 3D graphics, music synthesis audio and modem communications to run concurrently.

The Mpact R media processor with its associated Rambus media memory resides on the PCI bus. An internal 170-MHz 24-bit RAMDAC supports RGB display monitors. A digital video interface and a programmable I/O interface support a wide range of peripheral devices. This flexibility makes the Mpact media processor the ideal solution for designing integrated, low cost, multimedia PCs.

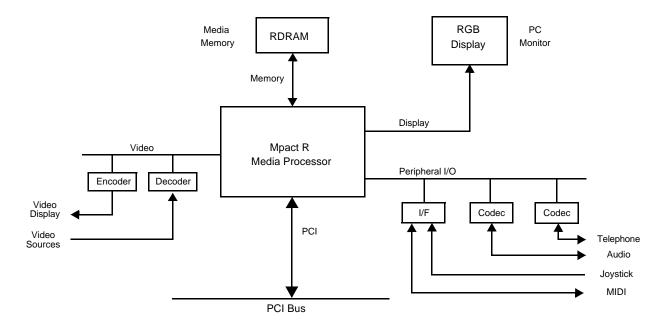

Figure 1. A Single Mpact R Media Processor On The PCI Bus Supports All Multimedia Functions.

# **GENERAL DESCRIPTION**

# Multimedia On The PC

The functionality and performance of the x86 PC has steadily increased to meet the demands of multimedia. This has been through higher host x86 performance and a variety of peripheral processors and accelerator boards designed for specific media related functions. Commercial success has brought some generally accepted standard functions, hardware interfaces and, importantly with Windows 95, the DirectX family of uniform Application Programming Interfaces (APIs).

The high functional density and speed of submicron integrated circuit technology now allows all of the special multimedia processing to be combined in one programmable processor. Also, Rambus technology now provides low-cost, but high bandwidth dynamic memories to support graphics and video buffer needs. Chromatic Research and its partners have utilized these three trends: a more uniform hardware and software operating environment; large, fast, low-cost memories; and high density VLSI circuits to form a total multimedia solution for the Windows 95 PC. The result is the Mpact media processor with associated Mpact mediaware modules of software.

# The Mpact R Media Processor

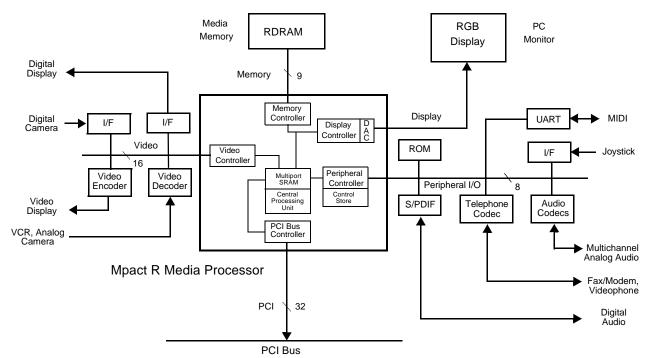

The Mpact R media processor is on the host PCI bus for tightly coupled sharing of the multimedia tasks being executed. The arithmetic and display buffer intensive portions of the tasks are done in a very long instruction word (VLIW) central processing unit (CPU) that operates out of

a shared eight port SRAM. The Mpact R/3600 CPU has five execution units operating in parallel from a single 72-bit instruction word at a peak 3600 million operations per second rate.

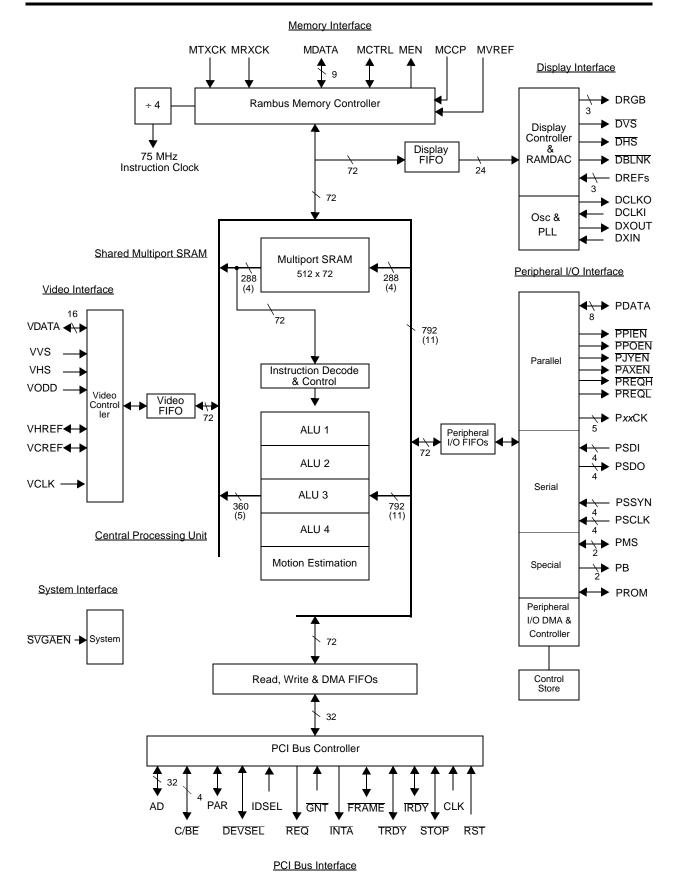

Five controllers share the SRAM with the CPU to concurrently support the wide variety of multimedia peripherals shown in Figure 2. These peripherals, the media buffer memory and the PCI bus connect through five distinct interfaces whose signals are summarized in Table 1.

# **Interfaces**

# Display

A direct connection to RGB color PC monitors capable of up to 1600 x 1200 resolution displays.

#### Video

For YUV digital video from analog or digital sources and to analog or digital displays.

### Peripheral I/O

For serial and parallel digital audio and telephony codecs, digital interfaces to joysticks and MIDI, and the BIOS and Plug and Play ROMs. Microprogrammable for flexibility.

#### Memory

For 9-bit-wide modules of 600 MB/s Rambus media memory. Normal configuration uses one 2-MB RDRAM.

#### PCI Bus

A 132 MB/s burst connection to the x86 host system.

Figure 2. A CPU And Five I/O Controllers Operating Out Of A Multiport SRAM Concurrently Service The Elements Of A Multimedia PC.

Table 1. Mpact R Media Processor Interface Signal Summary

| NAME                                   | NUMBER          | TYPE   | DESCRIPTION                                                                                                            |

|----------------------------------------|-----------------|--------|------------------------------------------------------------------------------------------------------------------------|

| Display Interface                      | 13              |        | •                                                                                                                      |

| DRED, DGRN, DBLUE                      | 3               | AO     | Display analog color intensity, RGB                                                                                    |

| DVS, DHS, DBLNK                        | 3               | 0      | Display Vertical and Horizontal Synchronization and Blanking                                                           |

| DVREF, DRSET, DCOMP                    | 3               | Al     | Display Voltage Reference, Set Resistance and Compensation                                                             |

| DCLKI, DCLKO, DXIN, DXOUT              | 4               | I, O   | Display Clock and Xtal Inputs and Outputs                                                                              |

| Video Interface                        | 22              |        |                                                                                                                        |

| VDATA [15:0]                           | 16              | I/O    | Video Data, YUV                                                                                                        |

| VVS, VHS, VODD                         | 3               | ı      | Video Vertical and Horizontal Synchronization and field indicator                                                      |

| VCREF, VHREF                           | 2               | I/O    | Video pixel Clock Reference and Horizontal Reference                                                                   |

| VCLK                                   | 1               | ı      | Video Clock                                                                                                            |

| Peripheral I/O Interface - Parallel    | 19              |        |                                                                                                                        |

| PDATA[7:0]                             | 8               | I/O    | Peripheral Parallel Data                                                                                               |

| PPIEN, PPOEN                           | 2               | 0      | Peripheral Parallel data Input and Output Enables                                                                      |

| PJYEN, PAXEN                           | 2               | 0      | Peripheral Parallel Joystick and Auxiliary control input Enables                                                       |

| PREQH, PREQL                           | 2               | 0      | Peripheral Parallel Request input Enables, High and Low bytes                                                          |

| PPDCK, PPACK, PCSCK, PCOCK, PJYCK      | 5               | 0      | Peripheral Parallel Data, Parallel Address, Chip Select, Control and Joystick register Clocks                          |

| Peripheral I/O Interface - Serial      | 16              |        |                                                                                                                        |

| PSDI[3:0], PSDO[3:0]                   | 8               | I, O   | Peripheral Serial Data Inputs and Outputs, channels 0-3                                                                |

| PSSYN[3:0]                             | 4               | ī      | Peripheral Serial Synchronization inputs, channels 0-3                                                                 |

| PSCLK[3:0]                             | 4               | ı      | Peripheral Serial Clock inputs, channels 0-3                                                                           |

| Peripheral I/O Interface - Special     | 5               |        | 1                                                                                                                      |

| PMSD, PMSC                             | 2               | I/O    | Peripheral Mpact Serial bus Data and Clock                                                                             |

| PB0, PB1                               | 2               | 0      | Peripheral Programmed output Bits 0 and 1                                                                              |

| PROM                                   | 1               | I/O    | Peripheral system identification ROM, serial input/output                                                              |

| Memory Interface - Rambus              | 15              |        | , , ,                                                                                                                  |

| MDATA[8:0]                             | 9               | I/O    | Memory Data                                                                                                            |

| MCTRL, MEN                             | 2               | I/O, O | Memory Control and Enable                                                                                              |

| MCCP, MVREF                            | 2               | Al     | Memory Current Control Program and Voltage Reference (analog)                                                          |

| MTXCK, MRXCK                           | 2               | I      | Memory Transmit and Receive Clocks. The processor clock.                                                               |

| PCI Bus Interface                      | 48              |        |                                                                                                                        |

| AD[31:0]                               | 32              | I/O    | PCI bus Address and Data                                                                                               |

| C/BE[3:0]                              | 4               | I/O    | PCI bus Command or Byte Enable                                                                                         |

| PAR                                    | 1               | I/O    | PCI bus Parity                                                                                                         |

| DEVSEL                                 | 1               | I/O    | PCI bus Device Select                                                                                                  |

| IDSEL                                  | 1               | I      | PCI bus Initialization Device Select                                                                                   |

| REQ, GNT                               | 2               | O, I   | PCI bus master Request and Grant                                                                                       |

| INTA                                   | 1               | 0      | PCI bus Interrupt A request                                                                                            |

| FRAME                                  | 1               | I/O    | PCI bus Frame transaction                                                                                              |

| IRDY, TRDY                             | 2               | I/O    | PCI bus Initiator and Target Readies                                                                                   |

| STOP                                   | 1               | I/O    | PCI bus Stop transaction                                                                                               |

| CLK                                    | 1               | I      | PCI bus Clock                                                                                                          |

| RST                                    | 1               | ı      | PCI bus Reset                                                                                                          |

| System Interface & No Connect          | 12              |        | •                                                                                                                      |

|                                        |                 |        |                                                                                                                        |

| Power                                  | 90              |        |                                                                                                                        |

|                                        | <b>90</b><br>45 | P      | +5 Volt power supply and +3.3 Volt power supply in 11 groupings                                                        |

| Power V <sub>DD</sub> V <sub>GND</sub> |                 | P<br>P | +5 Volt power supply and +3.3 Volt power supply in 11 groupings  Power supply ground in one core and ten I/O groupings |

# **Mpact Mediaware**

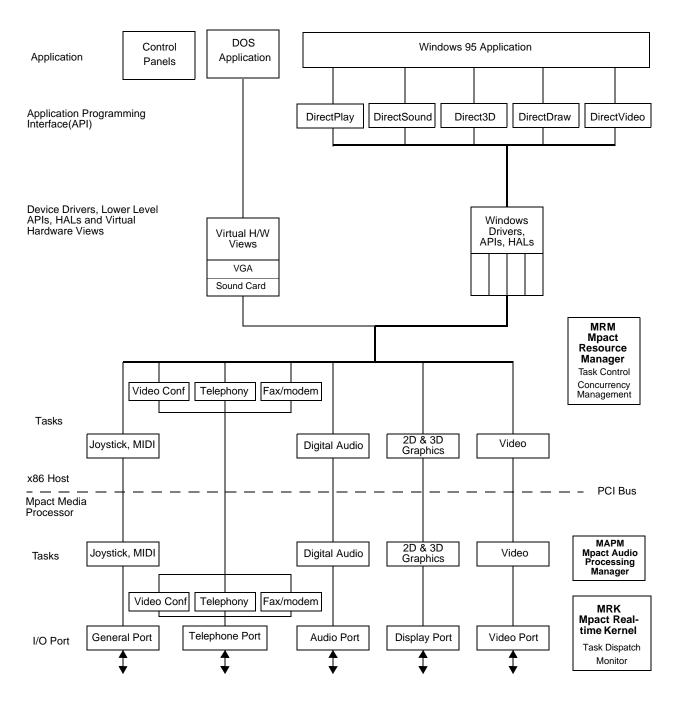

Mpact mediaware by Chromatic Research is the software that enables access to the high-performance Mpact media processor on an x86 system. Through support for the latest DirectX APIs, in addition to alternative and earlier component APIs and legacy hardware views, the mediaware provides Mpact's power to DOS and Windows applications running on Windows 95. The system software component parts are shown schematically in a highly simplified form in Figure 4.

# **System Operation**

Applications, when running, invoke various functions through their API or hardware view. These become single or multiple individual tasks related to the I/O port that is involved: video tasks use the Video port, 2D and 3D graphics use the Display port, digital audio tasks use the Audio port, fax/modem, telephony and videoconferencing use the Telephone port and the joystick, MIDI and ancillary functions use the General Port. These five classes of port are an important logical distinction. A port may use more than one electrical interface and is I/O device specific for the system.

#### Mpact Resource Manager - MRM

Operational tasks are executed on the x86 host, the media processor or both (as shown in Figure 4) as determined by the MRM resource manager operating on the host. MRM performs dynamic real-time task linking and loading based on the resources available as well as providing a backoff or graceful degradation strategy when either is over subscribed.

#### Mpact Real-time Kernel - MRK

The MRK dynamically schedules and dispatches tasks based on nearest deadlines. It is Mpact media processor resident and can be pre-emptive to meet the nearest deadline requirements.

## Mpact Audio Processing Manager - MAPM

Real-time audio related tasks are controlled by a sub-task processing manager to ensure that synchronous audio operations are maintained without interruption. The human ear is more sensitive to time lapses than the eye is to the lapse's visual effects.

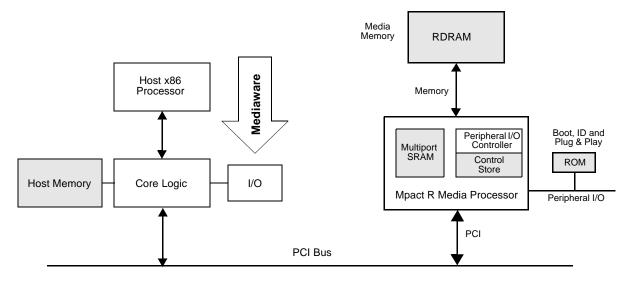

# **Memory Resources**

Figure 3 shows the five memories managed by the Mpact Resource Manager. All media processor operations, including the MRK control, are from instructions resident in its multiported SRAM. Task instructions and corresponding SRAM data buffers are kept current from the media memory. The media memory also contains graphic and video display and audio buffers which are maintained directly by the processor and controllers.

The Peripheral I/O controller microcode executes out of its control store RAM. Normally all I/O routines can be resident, with only error handling needing to be downloaded from the media memory on a demand basis.

Boot initialization routines for the media processor and extended BIOS reside in the ROM on the Peripheral I/O interface. All other operational software is resident on the x86 host memory system and managed by the MRM. Mediaware modules are easily updated for new functionality using diskettes, CDROMs or by using on-line services.

Figure 3. Real-Time Multimedia Operation Utilizes Mpact Mediaware Modules Resident In Five Memories.

# **Mpact Mediaware Modules**

A mediaware module can be thought of as a narrow vertical slice extending from the top to the bottom of Figure 4. Each mediaware module adds a multimedia function generally defined by its primary task. These functions are summarized in Table 4 with primary attributes for the eight functional groups. Of equal importance are the supported APIs at the top that invoke the functions and the devices at the bottom that are supported by an I/O port. Table 4 summarizes the supported APIs and Table 5 in

the Input/Output Interface section summarizes the supported devices. Table 4 shows by major API the functions that are enabled.

Individual Mpact mediaware releases should be consulted for specific performance specifications.

# Video Compression and Decompression

The mediaware video modules support international standards for decompression, including MPEG-1 and MPEG-2 video, audio and system decoding through the

Figure 4. Distribution Of Operating Software Between The Mpact Media Processor And A Windows '95 PC Host.

DirectVideo, MCI and ActiveMovie APIs. The media processor's patented hardware motion estimation function enables high quality real-time MPEG-1 video, audio and system encoding as well as videoconferencing.

## 2D Graphics - VGA and GUI Acceleration

The mediaware graphics module provides full VGA compatibility for legacy applications and full SVGA as defined in VESA BIOS extension 2.0. Internal buffers support 8-, 15-, 16-, 24- and 32-bits per pixel views. The special 18-bit Chro-color format provides color depth performance between the 16-bit and 24-bit true-color with greater memory efficiency.

GUI acceleration is optimized for Windows 95 performance with a hardware cursor through the GDI and DirectDraw APIs. Acceleration is provided for solid and pattern fill, font and polygon generation, line draw, scaling and clipping, and color space conversion.

## 3D Graphics Acceleration

The mediaware 3D graphics module is optimized to fully accelerate 3D rendering for game play through the Direct3D API.

Table 2. Mpact Mediaware API Summary By Function.

| ·                                |                                                    |

|----------------------------------|----------------------------------------------------|

| FUNCTION                         | APIs                                               |

| Video                            |                                                    |

| MPEG Decode:                     | DirectVideo, MCI, ActiveMovie                      |

| MPEG Encode:                     | ActiveMovie                                        |

| Graphics - 2D                    | •                                                  |

| Graphics Card:                   | VGA, SVGA compatible                               |

| GUI Acceleration:                | DirectDraw, GDI                                    |

| Graphics - 3D                    |                                                    |

| 3D Acceleration:                 | Direct3D, OpenGL, RealityLab                       |

| Digital Audio                    |                                                    |

| Sound Card:                      | Industry Standard with FM                          |

| Output:                          | DirectSound, MCI                                   |

| Music:                           | MCI, MIDIout/in, WAVEout/in                        |

| Effects:                         | DirectSound 3D Audio                               |

| Fax/Modem                        |                                                    |

| Fax/Data modem                   | TAPI, TSPI, VCOMM, DirectPlay                      |

| Telephony                        |                                                    |

| Speakerphone,<br>DSVD, Voicemail | TAPI, TSPI, VCOMM, DirectPlay                      |

| Videoconferencing                |                                                    |

|                                  | ActiveMovie, Independent Software Vendor's (ISV's) |

| General                          |                                                    |

| Joystick/MIDI                    | Industry Standard Sound Card                       |

## Digital Audio

The mediaware digital audio modules can utilize full 36-bit processing at 48 kHz sampling rates, even for compute-intensive functions like Dolby AC-3 and Waveguide physical modeling music synthesis. Automatic resampling is used so that all processing is at a uniform 48-kHz rate.

#### Fax/Modem

The mediaware Fax/modem modules support the latest current data and Fax modem standards. For data modulation to 33,600 b/s there is V.34bis, V.32bis, V.22bis, V.21, Bell 212A and Bell 103. For Fax modulation to 14,400 b/s there is V.17, V.29, V.27ter, and V.21.

### Telephony

The mediaware telephony modules combine the AT+V command set with various functions like echo-cancelling, DTMF, ADPCM coding and DSVD processing to permit a full range of telephony operations like speakerphone, voicemail, answering machine and voice response.

# Videoconferencing

The mediaware videoconferencing modules support international standards over ISDN and standard telephone lines to interface with various ISV's videophone applications.

#### General

For games and entertainment, the industry standard sound board interfaces to a joystick with buttons and MIDI, the Musical Instrument Digital Interface, are supported in mediaware modules.

Table 3. Mpact Mediaware API Support Summary.

|                 | 1                                              |

|-----------------|------------------------------------------------|

| API             | FUNCTIONS                                      |

| DOS             |                                                |

| VGA Compatible  | All                                            |

| SVGA Compatible | All VESA Extension 2.0                         |

| Sound Card      | All                                            |

| WINDOWS 95      |                                                |

| DirectVideo     |                                                |

|                 |                                                |

| ActiveMovie     | MPEG encode and decode, vid-<br>eoconferencing |

| DirectDraw      |                                                |

|                 |                                                |

| Direct3D        |                                                |

|                 |                                                |

| DirectSound     |                                                |

|                 |                                                |

| DirectPlay      |                                                |

Table 4. Mpact Mediaware Functions Summary

| 14515             | Thipact Mediaware Functions Summary                                                                                                                                        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FUNCTION          | DESCRIPTION                                                                                                                                                                |

| Video             |                                                                                                                                                                            |

| Encode & Decode:  | MPEG-1 Decoder, SIF 352 x 240, 30 f/s                                                                                                                                      |

|                   | MPEG-2 Decoder, Main Level, Main Profile, NTSC 720 x 480, 30 f/s or PAL 720 x 576 25 f/s                                                                                   |

|                   | MPEG-1 Real-time encode, SIF I frames 30 f/s, 10 Mb/s                                                                                                                      |

|                   | MPEG-1 Non-real-time encode, IBP frames                                                                                                                                    |

| Graphics - 2D     |                                                                                                                                                                            |

| Graphics Card:    | VGA, all modes, up to 640 x 480 x 4 b/p @ 85 Hz                                                                                                                            |

|                   | SVGA, up to 1280 x 1024 x 18 b/p @ 75 Hz or 1024 x 768 x 24 b/p @ 85 Hz                                                                                                    |

| GUI Acceleration: | Full 256 Ternary ROPs, BitBLT, font acceleration, line draw, polygon engine, YUV color conversion, H/W cursor                                                              |

| Graphics - 3D     | F = 7 g = 1 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 -                                                                                                                          |

| 3D Acceleration:  | Full rendering with lighting, shading, texturing, anti-aliasing support for rectangle fills, 3D spans and geometric primitives such as lines, triangles and quadrilaterals |

| Digital Audio     |                                                                                                                                                                            |

| Sound Card:       | Industry Standard with FM synthesis                                                                                                                                        |

| Encode & Decode:  | MPEG-1, Layers 1 & 2                                                                                                                                                       |

|                   | MPEG-2 AC-3 decode                                                                                                                                                         |

|                   | Dolby AC-3, 5.1 channel decode                                                                                                                                             |

|                   | Dolby ProLogic, 4 channel and stereo decode                                                                                                                                |

|                   | IMA ADPCM for Windows                                                                                                                                                      |

| Music:            | FM synthesis                                                                                                                                                               |

|                   | Wave Table synthesis (32 voices, 32 multitrimbality parts), Synclavier® sample library                                                                                     |

|                   | Waveguide synthesis                                                                                                                                                        |

|                   | General MIDI, 128 instruments +>50 percussion, 64 voices                                                                                                                   |

| Effects:          | Surround and 3D Sound (SRS), 3D Positional Audio<br>Effects (Direct Sound), reverb, chorus, noise cancellation                                                             |

| Fax/Modem         |                                                                                                                                                                            |

| Data Rates:       | Up to V.34bis @ 33.6 kb/s                                                                                                                                                  |

| Fax Rates:        | Up to V.17 @ 14.4 kb/s                                                                                                                                                     |

| Data Protocols:   | V.42, V.42bis, MNP 2-4 error correction, compression.                                                                                                                      |

|                   | AT Command set                                                                                                                                                             |

| Fax Protocols:    | Class 1 (TIA-578), 2, 2.0 (TIA-592)                                                                                                                                        |

| Telephony         |                                                                                                                                                                            |

|                   | Full-duplex speakerphone, caller ID and answering machine using the IS-101A (AT+V Command set)                                                                             |

|                   | IMA ADPCM encoding/decoding                                                                                                                                                |

|                   | Digital simultaneous voice and data (DSVD)                                                                                                                                 |

| Videoconferencing |                                                                                                                                                                            |

|                   | H.320 over ISDN                                                                                                                                                            |

|                   | H.324 over POTS                                                                                                                                                            |

| General           |                                                                                                                                                                            |

| Joystick:         | Industry standard connector including MIDI                                                                                                                                 |

| MIDI:             | Industry standard NS16550 UART I/O                                                                                                                                         |

|                   |                                                                                                                                                                            |

Figure 5. The Mpact R/3600 Media Processor Block Diagram

# **FUNCTIONAL DESCRIPTION**

An Mpact R/3600 media processor is composed of the interconnected functional hardware units shown in the block diagram of Figure 5. The five interface controllers with their associated memory or FIFOs share the 4 kbyte multiport SRAM with the central processing unit (CPU). The basic bus width is that of a double word of eight 9-bit bytes for a total of 72 bits. Wider buses are shown with multiples of this basic width in parenthesis. Most interconnection is by crossbar connection to a 792-bit bus that allows multiple data sinks for an aggregate bandwidth of 10.8 GB/s. Transfers are controlled by the instructions executed by the CPU in combination with the interface controllers whose operation is setup by the CPU. The FIFOs on the non-memory interfaces ensure steady I/O data flows and a direct link to the display interface from the RDRAM media memory maintains the display.

# **Shared Multiport SRAM**

All CPU instructions are fetched out of the shared multiport SRAM and most data operations are on data stored there. The simultaneous four read and four write ports provide a steady flow of instructions and data to the CPU, allow I/O buffers to be maintained in the SRAM and execute load and store instructions with the RDRAM media memory. The 4 kbytes SRAM is organized as 512 double words of 8 bytes each. The CPU maintains the cache of data and instructions in the SRAM from the RDRAM media memory.

# **Central Processing Unit (CPU)**

The central processing unit consists of four arithmetic/logic unit (ALU) groups, a motion estimation unit and the instruction decode and control.

#### Instruction Execution

The Mpact R/3600 media processor is a very long instruction word (VLIW) processor where each instruction word is 72 bits. Each word is composed of two instructions that are 3 to 5 bytes in length each. Instructions cause multiple operations within a group and even multiple operations in multiple groups. A single instruction word can cause 8 single-byte operations to be executed on each of the four ALU groups for sustained rates of 2.4 billion operation per second (2.4 BOPS). Peak rates can reach 3.6 BOPS. Instruction memory efficiency is high because of vector and block repeat instructions.

# ALU1

Each ALU group operates on double words of 8 bytes which can be 1, 2, 4 or 8 operands. ALU1 is a shift and align group which uses three inputs for extensive crossbar operations to produce two results.

# ALU2

ALU2 is a general purpose ALU group with two inputs and a single output result except for special FFT butterfly instructions which produce a sum and difference result.

#### **ALU3 & 4**

ALU3 is a general purpose ALU group without the butterfly operations but it is augmented with three inputs for ternary operations that produce two results. ALU4 uses Booth encoders in a Wallace tree structure to produce various precisions of multiply and multiply-add operations in combination with ALU3 which outputs the results.

#### **Motion Estimation Unit**

The Mpact R/3600 media processor motion estimation unit consists of some 400 arithmetic elements which produce an additional 24 BOPS performance for MPEG motion estimation.

# **Input/Output Interfaces And Ports**

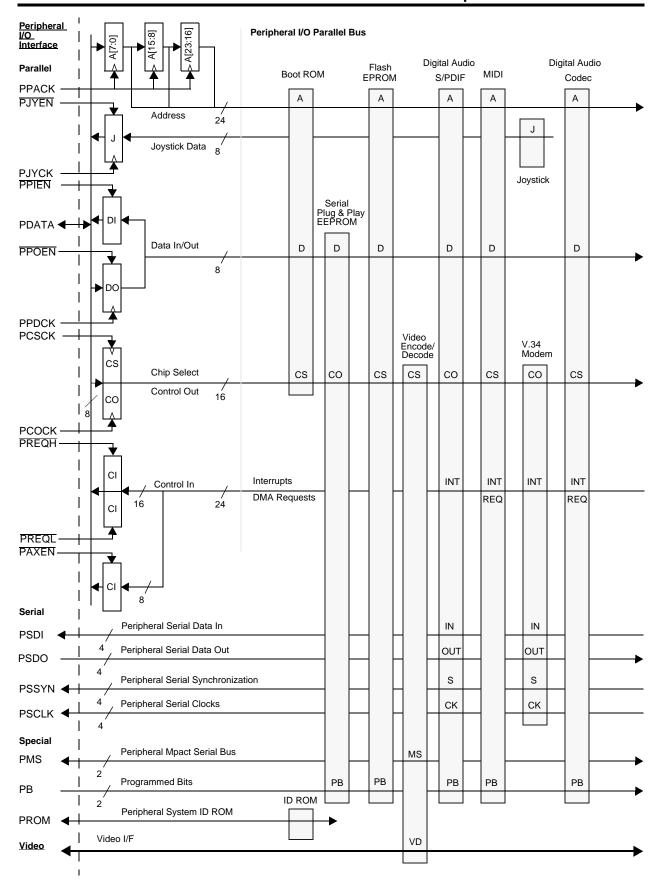

Of the five interfaces on the media processor, three are used for system input/output devices: the Display, the Video and the Peripheral I/O interfaces. A typical I/O device uses signals from more than one interface. The combination of signals from various interfaces to support a particular class of I/O device and its associated mediaware is called a port. There are five classes of ports for display, video, digital audio, telephone and general digital devices. Table 5 lists available ports and the interfaces signals that are used in each. Each port supports different functions and specific commercial devices for that function. These functions and devices are also listed in Table 5 with the Appendix which describes each port's design and operation. Example ports and devices are illustrated in Figure 6. Appendices are also provided for the Rambus Memory and PCI Bus Interfaces, and two alternative implementations for the Peripheral I/O Parallel Bus.

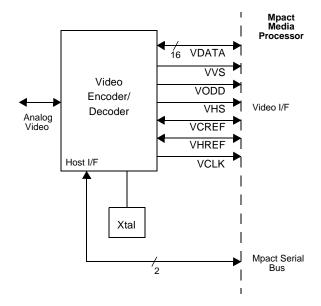

#### Video Port

The video port is used for direct digital video input or output in the 4:2:2 YUV format of CCIR 601. The video interface signals can be used directly for most digital video cameras, solid-state digital displays or the Zoom Video interface.

Analog video is input through decoders and output through encoders. Data is transferred on the video interface with the Mpact Serial and/or the Peripheral I/O parallel interface used for control functions.

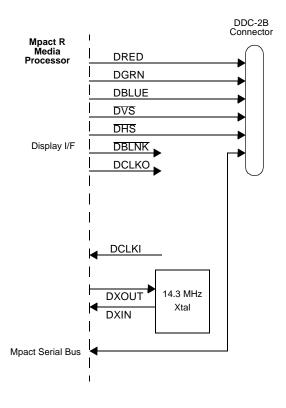

# Display Port

The display port is used for the PC monitor's RGB color display. Analog RGB signals are generated by an internal 170-MHz RAMDAC and the Mpact Serial interface can be used for display control functions.

# **Digital Audio Port**

The digital audio port is used for both analog codecs and digital S/PDIF devices for input and output. Data is transferred on the Peripheral I/O interface along with control.

# **Telephone Port**

The telephone port uses the Peripheral I/O interface for supporting telephony, fax/modem and videoconferencing codecs.

#### General Port

The general port uses the Peripheral I/O interface for transfers with other digital support devices that are in the typical multimedia system. These include game joysticks, MIDI and the various system ROMs.

### Memory And PCI Bus Interfaces

These interfaces are used for standard Rambus media memory and the industry standard 32-bit PCI bus.

### Peripheral I/O Parallel Bus

The Peripheral I/O Parallel Bus is formed from Peripheral I/O Interface signals using discrete external buffers or the Mpact System Integration ASIC (MSIA).

Table 5. Mpact Input/Output Ports & Interfaces

| I/O Function                 | Interface*    | I/O Device | A** |

|------------------------------|---------------|------------|-----|

| Video Port - YUV             | •             |            |     |

| Analog output encoder:       |               |            |     |

| NTSC/PAL                     | V, PP, PMS    | SAA7187    | A11 |

|                              |               | AD7176     |     |

| Analog input decoder:        |               |            |     |

| NTSC/PAL/SECAM               | V, PP, PMS    | SAA7110    | A12 |

| NTSC/PAL                     | V, PP, PMS    | KS0122     |     |

| Digital I/O:                 |               |            |     |

| CCIR 601 4:2:2 YUV           | V             |            | A15 |

| Display Port - RGB           |               |            |     |

| RGB display                  | D, PMS        |            | A4  |

| Digital Audio Port           |               |            |     |

| Parallel Codec               |               |            |     |

| 16 bit, 48 KHz, stereo       | PP, PB        | CS4231A    | A5  |

|                              |               | AD1845, 48 |     |

| Serial Codec                 | •             |            |     |

| 16 bit, 48 KHz, stereo       | PS, PB        | CS4216     | A13 |

| S/PDIF                       |               |            |     |

| Output                       | PP, PS, PB    | CS8401     | A6  |

| Telephone Port               | •             |            |     |

| Fax/Modem/Telephony/H.       | 324 Videoconf | erencing   |     |

| V.34                         | PP, PS        | CSP1027    | A7  |

| Fax/Modem/Telephony          |               |            |     |

| V.32bis                      | PP, PS        | T7525      | A14 |

| Videoconferencing            |               |            |     |

| H.320 for ISDN               |               |            | A16 |

| General Port                 |               |            |     |

| Joystick                     | PP            | Ind. Std.  | A8  |

| MIDI UART                    | PP, PB        | NS16550A   |     |

| System ID ROM                | PROM          | DS2430A    | A10 |

| Boot and P&P                 | PP            | Am29F010   |     |

| Flash EPROM                  |               |            |     |

| Boot ROM                     | PP            | Ind. Std.  |     |

| Plug & Play<br>serial EEPROM | PP, PB        | X84041     |     |

| Memory Interface             | Memory        | Rambus     | A1  |

| PCI Bus Interface            | PCI Bus       | Ind. Std.  | A2  |

| Peripheral I/O Parallel B    | us            | •          | •   |

| Discrete components          | PP            |            | А3  |

| ASIC                         | PP            |            |     |

|                              |               | •          |     |

$<sup>^{\</sup>star}$  V = Video, D = Display, PP = Peripheral I/O Parallel, PS = Peripheral I/O Serial, PMS = Peripheral Mpact Serial, PB = Peripheral Programmed Bits.

<sup>\*\*</sup> Data Sheet Appendix number.

# **Video Controller And Interface**

The video controller, in combination with the 32-byte video FIFO, inputs or outputs YUV video data on the 16-bit video interface. This programmable interface is bidirectional but transfers are half-duplex. The three input synchronization signals, two bidirectional reference clock signals and an external video clock input can support a wide variety of 16-bit input video sources and output devices in either 8- or 16-bit formats. Industry standard NTSC or PAL encoders and decoders can be used at full scan rates for analog composite or S-video signals. Digital interfaces can be used for Zoom Video or CCIR 601 YUV 4:2:2 digital cameras or displays. Formats can be interlaced or progressive scan. The video controller is capable of horizontal decimation on input or output.

Among the supported devices in the Mpact mediaware modules video port are the SAA7187 and AD7176 encoders and the SAA7110 and KS0122 decoders. Control of the interfaced device is with the Peripheral Mpact Serial bus (the PMSD and PMSC signals) with possible device selection from the Peripheral I/O parallel interface.

# Display Controller, RAMDAC And Interface

The display controller in combination with the 512-byte display FIFO provides continuous RGB display data to the internal 170-MHz RAMDAC from buffers in the RDRAM media memory.

Display data is stored in the media memory in one-, twoor three-byte formats to support 8, 15, 16, 18 and 24 bits per pixel. The special 18 bits per pixel data Chro-color format provides a 32-bit buffer view yet takes only two bytes in the media memory. The conversion from media memory format to RAMDAC format takes place in the display controller.

The display controller generates all data, synchronization and clock signals to the internal display RAMDAC (digital-to-analog converter) from a single video clock generator input DCLKI or from the internal 14.3181 MHz oscillator and PLL. 24-Bit true-color and other possible display resolutions and the pixel clock frequency DCLKO are shown in Table 6. The maximum refresh rate may not be possible with the maximum pixel depth.

Table 6. Display Resolutions

| Display<br>Resolution | Pixel Clock<br>Frequency<br>MHz | Maximum<br>Refresh<br>Rate Hz | Maximum<br>Pixel<br>Depth |

|-----------------------|---------------------------------|-------------------------------|---------------------------|

| 1600 x 1200           | 170                             | 60                            | 8                         |

| 1280 x 1024           | 135                             | 85                            | 16                        |

| 1152 x 870            | 121                             | 85                            | 18                        |

| 1024 x 768            | 94.5                            | 85                            | 24                        |

| 800 x 600             | 56                              | 85                            | 24                        |

| 640 x 480             | 36                              | 85                            | 24                        |

| NTSC: 720 x 480       | 14.318                          | 30                            | 24                        |

| PAL: 720 x 576        | 16.250                          | 25                            | 24                        |

Control of a DDC-2B display monitor is through the use of the Mpact Serial bus in the Peripheral I/O interface connected as shown.

Figure 6. Peripheral I/O Interface External Components And Connections To Example Mediaware Supported I/O Devices.

# Peripheral Input/Output Controller And Interface

The Peripheral I/O controller and its associated FIFOs provide the interface to lower bandwidth peripheral components of the multimedia system. This is done with eight generic unidirectional bit-serial data buses, a single generic bidirectional 8-bit parallel data bus and three special buses. The aggregate data rate can be as high as 6 Mbytes/second in the Mpact R/3600 media processor. These generic buses become device and function specific ports with the loading of the 96-byte controller microcode RAM and the use of the various mediaware modules. A total of fourteen different transaction ports may be operational at one time, with twelve of them using separate DMAs and 8-byte each FIFOs. Figure 6 shows the interface connections to ten example I/O devices that are supported by mediaware. Signals labelled and shown visibly passing through the block are connected in that block. The device types are listed in Table 5. These serve to illustrate typical interfaces to I/O peripherals.

The Peripheral Input/Output Interface divides naturally into three sections for parallel data, serial data and special transfers.

#### Parallel Interface

The 8-bit bidirectional PDATA[7:0] bus transfers not only data in and out, but also has specific clocking and control signals to support 24-bit addressing, 8 chip-select outputs, 8 general control signal outputs, 12 interrupt requests and 12 DMA requests. Also, it provides the periodic clock timing for a joystick input. Figure 6 shows the clocking and output enables for the seven 8-bit registers and four input multiplexers. Table 8 summarizes the Peripheral I/O Parallel Bus signals that result.

Table 7. Peripheral I/O Parallel Bus Signals

| Signal                 | Number | Туре |

|------------------------|--------|------|

| Data In/Out [7:0]      | 8      | I/O  |

| Address [23:0]         | 24     | 0    |

| Chip Select [7:0]      | 8      | 0    |

| Control Out [7:0]      | 8      | 0    |

| Interrupt In [11:0]    | 12     | I    |

| DMA Request In [11:0]  | 12     |      |

| Joystick Data In [7:0] | 8      | I    |

This configuration can support most popular I/O peripherals with a parallel data interface today, but because its timing and function is programmable it can easily adapt to the data, address and sequence formats of future devices.

### Serial Interface

The bit-serial interface has four input channels 0 - 3 and four output channels 0 - 3. Like numbered input and output channels, PSDI[3:0] and PSDO[3:0], share common

data clocks PSCLK[3:0] and frame synchronization signals PSSYN[3:0]. These can support the wide variety of slave mode serial data formats used in audio and telephony codecs as well as the serial control ports of many microprocessor peripherals.

## Special Interface

**Mpact Serial Bus**

Many microprocessor peripherals, including display and video products, use a two-wire bidirectional bus for multimaster control. The peripheral Mpact Serial Bus, PMSD and PMSC, is an enhanced version of the industry standard for support of these devices.

**Programmed Bits**

The PB[1:0] signals are two outputs without external registering that can be used for peripheral communication without regard to other transfers on the parallel or serial interfaces. They are set and cleared directly by the peripheral I/O controller's microcode.

System Identification ROM

Each Mpact media processor has a unique system identification number read from a one-time-programmable ROM. The bidirectional PROM signal provides a single pin connection to a DS2430A or similar device for this purpose.

# Rambus Memory Controller And Interface

The memory controller supports external Rambus DRAM (RDRAM) media memory connected to the memory interface. Media memory is used for both data and instruction storage for transfer to the processor's multiported SRAM as well as for video and display data buffers.

The controller has direct access to the multiported SRAM and the display FIFO for rapid transfers with the RDRAM. All addresses are translated in the controller to provide tiling for greater transfer rates on large video and display buffers. In addition, the controller provides memory refresh and facilitates internal RDRAM register initialization.

The minimum media memory is 2 Mbytes of 9-bit (18-Mbit) RDRAM. Increments of 2 Mbytes can be added up to a maximum of 8 Mbytes. The interface utilizes the Rambus Signaling Logic (RSL) for transfers on each clock edge at a 600 Mbytes/second peak rate on the Mpact R/3600 media processor. The minimum amount of media memory required is a function of the maximum display resolution and associated pixel depth as shown in Table 8.

Both base and low-latency types of RDRAMs are supported on the Mpact R media processor.

Table 8. Media Memory Requirements

| Display<br>Resolution | Pixel Depth<br>In Bits | Minimum<br>RDRAM<br>Size |

|-----------------------|------------------------|--------------------------|

| 1600 x 1200           | 8                      | 4 MB                     |

| 1280 x 1024           | 16                     | 4 MB                     |

| 1280 x 1024           | 8                      | 2 MB                     |

| 1152 x 870            | 18                     | 4 MB                     |

| 1152 x 870            | 8                      | 2 MB                     |

| 1024 x 768            | 24                     | 4 MB                     |

| 1024 x 768            | 8, 18                  | 2 MB                     |

| 800 x 600             | 8, 18, 24              | 2 MB                     |

| 640 x 480             | 8, 18, 24              | 2 MB                     |

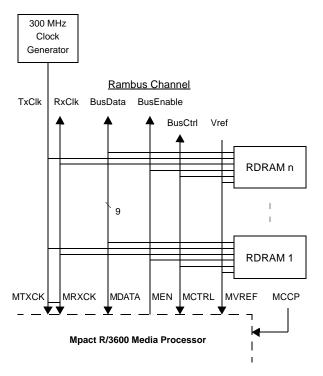

The interconnection of the RDRAM media memory on the Rambus channel is shown in Figure 7. Note that on the Mpact R/3600 media processor the external 300 MHz Rambus clock is the main processor system clock. The MCCP analog current input determines drive capability of the memory interface as specified by RSL.

Figure 7. RDRAM Media Memory On The Rambus Channel

### **PCI Bus Controller And Interface**

The PCI bus controller and its three FIFOs manage access between the Mpact media processor and the host x86. The interface is fully compliant with PCI Local Bus Specification, Revision 2.0 with either 3.3- or 5-Volt signaling. Peak transfer rates are 132 MB/second on the 32-

bit bus.

The Mpact media processor acts as a target or a bus master with transfers being fully concurrent with the host or memory subsystem at a synchronous 33-MHz rate. Three separate FIFOs provide for variable length read and write burst operation as a target and DMA operation as a master. The DMA FIFO is four 32-bit words, the write FIFO is eight words and the read only a single word buffer

As determined in the PCI configuration space, the Mpact media processor appears in address space in three forms: as 128 MB of memory, as 128 kB of extension ROM and as specific device compatibility addresses. Autoconfiguration for add-in cards and components is supported.

Correct 5 Volt PCI bus signaling operation is assured by connecting the six V5DD power pins to +5 Volts rather than +3.3 Volts.

# **System Interface**

The Mpact R media processor can be configured and tested using signals in the system interface.

The SVGAEN signal allows disabling the Mpact R media processor from appearing in PCI configuration space as a VGA device. When asserted the class code is 030000 Hex for VGA Compatible Controller. When not asserted the class code is 048000 Hex for Other Multimedia Device.

The TMS signal puts the media processor in a test mode of operation that changes the function of certain pins. For normal operation it should not be asserted.

# **SIGNAL DESCRIPTION**

Table 9. Mpact R Media Processor Signal Description

| Table 9. Mipact K Media Processor Signal Description |                        |      |                                                                                        |  |  |  |

|------------------------------------------------------|------------------------|------|----------------------------------------------------------------------------------------|--|--|--|

| NAME                                                 | NUMBER                 | TYPE | DESCRIPTION                                                                            |  |  |  |

|                                                      | Display Interface (13) |      |                                                                                        |  |  |  |

| DRED                                                 | 1                      | AO   | Display Red analog output, RS-343                                                      |  |  |  |

| DGRN                                                 | 1                      | AO   | Display Green analog output, RS-343                                                    |  |  |  |

| DBLUE                                                | 1                      | AO   | Display Blue analog output, RS-343                                                     |  |  |  |

| DVS                                                  | 1                      | 0    | Display Vertical Synchronization                                                       |  |  |  |

| DHS                                                  | 1                      | 0    | Display Horizontal Synchronization                                                     |  |  |  |

| DBLNK                                                | 1                      | 0    | Display Blanking                                                                       |  |  |  |

| DVREF                                                | 1                      | Al   | Display Voltage Reference                                                              |  |  |  |

| DRSET                                                | 1                      | Al   | Display Set Resistance for full-scale output current adjustment                        |  |  |  |

| DCOMP                                                | 1                      | Al   | Display Compensation capacitance                                                       |  |  |  |

| DCLKI                                                | 1                      | _    | Display Clock Input. External pixel clock source.                                      |  |  |  |

| DCLKO                                                | 1                      | 0    | Display Clock Output. Pixel clock.                                                     |  |  |  |

| DXIN                                                 | 1                      | Al   | Display Xtal Input. 14.3181 MHz.                                                       |  |  |  |

| DXOUT                                                | 1                      | AO   | Display Xtal Output                                                                    |  |  |  |

|                                                      |                        |      | Video Interface (22)                                                                   |  |  |  |

| VDATA [15:0]                                         | 16                     | I/O  | Video Data, YUV                                                                        |  |  |  |

| VVS                                                  | 1                      | -    | Video Vertical Synchronization                                                         |  |  |  |

| VHS                                                  | 1                      | _    | Video Horizontal Synchronization                                                       |  |  |  |

| VODD                                                 | 1                      | -    | Video Odd field indicator                                                              |  |  |  |

| VCREF                                                | 1                      | I/O  | Video pixel Clock Reference                                                            |  |  |  |

| VHREF                                                | 1                      | I/O  | Video Horizontal Reference                                                             |  |  |  |

| VCLK                                                 | 1                      | _    | Video Clock. Twice the pixel rate.                                                     |  |  |  |

|                                                      |                        |      | Peripheral I/O Interface - Parallel (19)                                               |  |  |  |

| PDATA[7:0]                                           | 8                      | I/O  | Peripheral Parallel Data                                                               |  |  |  |

| PPIEN                                                | 1                      | 0    | Peripheral Parallel data Input Enable. Enables I/O parallel bus onto PDATA.            |  |  |  |

| PPOEN                                                | 1                      | 0    | Peripheral Parallel data Output Enable. Enables DO register onto I/O parallel bus      |  |  |  |

| PJYEN                                                | 1                      | 0    | Peripheral Parallel Joystick input Enable. Enables joystick register onto PDATA.       |  |  |  |

| PAXEN                                                | 1                      | 0    | Peripheral Auxiliary control input Enable. Enables auxiliary control input onto PDATA. |  |  |  |

| PREQH                                                | 1                      | 0    | Peripheral Parallel Request input Enable, High byte. Enables requests onto PDATA.      |  |  |  |

| PREQL                                                | 1                      | 0    | Peripheral Parallel Request input Enable, Low byte. Enables requests onto PDATA.       |  |  |  |

| PPDCK                                                | 1                      | 0    | Peripheral Parallel Data register Clock. Clocks PDATA data into DO register.           |  |  |  |

| PPACK                                                | 1                      | 0    | Peripheral Parallel Address register Clock. Clocks PDATA data into address registers.  |  |  |  |

| PCSCK                                                | 1                      | 0    | Peripheral Chip Select register Clock. Clocks PDATA data into chip select register.    |  |  |  |

| PCOCK                                                | 1                      | 0    | Peripheral Control Output register Clock. Clocks PDATA data into control out register. |  |  |  |

| PJYCK                                                | 1                      | 0    | Peripheral Joystick register Clock. Clocks joystick data into joystick input register. |  |  |  |

|                                                      |                        |      | Peripheral I/O Interface - Serial (16)                                                 |  |  |  |

| PSDI[3:0]                                            | 4                      | I    | Peripheral Serial Data Inputs, channels 0-3                                            |  |  |  |

| PSDO[3:0]                                            | 4                      | 0    | Peripheral Serial Data Outputs, channels 0-3                                           |  |  |  |

| PSSYN[3:0]                                           | 4                      | Ι    | Peripheral Serial Synchronization inputs, channels 0-3                                 |  |  |  |

| PSCLK[3:0]                                           | 4                      | Ι    | Peripheral Serial Clock inputs, channels 0-3                                           |  |  |  |

|                                                      |                        |      | Peripheral I/O Interface - Special (5)                                                 |  |  |  |

| PMSD                                                 | 1                      | I/O  | Peripheral Mpact Serial bus Data                                                       |  |  |  |

| PMSC                                                 | 1                      | I/O  | Peripheral Mpact Serial bus Clock                                                      |  |  |  |

| PB[1:0]                                              | 2                      | 0    | Peripheral Programmed output Bits 1 and 0                                              |  |  |  |

| PROM                                                 | 1                      | I/O  | Peripheral system identification ROM, serial input/output                              |  |  |  |

Table 9. Mpact R Media Processor Signal Description (Continued)

| NAME               | NUMBER | TYPE | DESCRIPTION                                                                                                                                                               |

|--------------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |        |      | Memory Interface - Rambus (15)                                                                                                                                            |

| MDATA[8:0]         | 9      | I/O  | Memory Data to/from the Rambus BusData signal                                                                                                                             |

| MCTRL              | 1      | I/O  | Memory Control to/from the Rambus BusCtrl signal                                                                                                                          |

| MEN                | 1      | 0    | Memory Enable to the Rambus BusEnable signal                                                                                                                              |

| MCCP               | 1      | AI   | Memory Current Control Program (CCtlPgm), an analog input derived from V <sub>term</sub>                                                                                  |

| MVREF              | 1      | Al   | Memory Voltage Reference, an analog input from the Rambus V <sub>ref</sub>                                                                                                |

| MTXCK              | 1      |      | Memory Transmit Clock from the Rambus TxClk signal. Transmit from memory.                                                                                                 |

| MRXCK              | 1      | _    | Memory Receive Clock from the Rambus RxClk signal. Receive into memory.                                                                                                   |

|                    |        |      | PCI Bus Interface (48)                                                                                                                                                    |

| AD[31:0]           | 32     | I/O  | PCI bus Address and Data                                                                                                                                                  |

| C/BE[3:0]          | 4      | I/O  | PCI bus Command or Byte Enable during address transactions                                                                                                                |

| PAR                | 1      | I/O  | PCI bus Parity                                                                                                                                                            |

| DEVSEL             | 1      | I/O  | PCI bus Device Select. Target has decoded its address.                                                                                                                    |

| IDSEL              | 1      | I    | PCI bus Initialization Device Select input                                                                                                                                |

| REQ                | 1      | 0    | PCI bus master Request                                                                                                                                                    |

| GNT                | 1      | I    | PCI bus master Grant                                                                                                                                                      |

| ĪNTĀ               | 1      | 0    | PCI bus Interrupt A request                                                                                                                                               |

| FRAME              | 1      | I/O  | PCI bus Frame transaction                                                                                                                                                 |

| IRDY               | 1      | I/O  | PCI bus Initiator Ready                                                                                                                                                   |

| TRDY               | 1      | I/O  | PCI bus Target Ready                                                                                                                                                      |

| STOP               | 1      | I/O  | PCI bus Stop transaction request by target                                                                                                                                |

| CLK                | 1      | I    | PCI bus Clock                                                                                                                                                             |

| RST                | 1      | I    | PCI bus Reset                                                                                                                                                             |

|                    |        |      | System Interface (3)                                                                                                                                                      |

| SVGAEN             | 1      | I    | System VGA Enable                                                                                                                                                         |

| TMS                | 1      | I .  | Test Mode Select                                                                                                                                                          |

| Test               | 1      | I    | Test                                                                                                                                                                      |

|                    |        |      | No Connection (9)                                                                                                                                                         |

| NC                 | 9      | NC   | No Connection. Must not be connected to V <sub>DD</sub> or V <sub>GND</sub> .                                                                                             |

|                    |        | _    | Power (90)                                                                                                                                                                |

| V <sub>DD</sub>    | 16     | Р    | +3.3 Volt power supply, core                                                                                                                                              |

| V5 <sub>DD</sub>   | 6      | Р    | +5 Volt power supply, I/O. Input clamping level. Should be 5.0 Volts in mixed 5/3.3-Volt supply voltage systems. Maybe 3.3 Volts in 3.3-Volt only supply voltage systems. |

| V <sub>DD</sub> 1  | 3      | Р    | +3.3 Volt power supply, display interface                                                                                                                                 |

| V <sub>DD</sub> 2  | 6      | Р    | +3.3 Volt power supply, PCI bus interface                                                                                                                                 |

| V <sub>DD</sub> 3  | 4      | Р    | +3.3 Volt power supply, peripheral interface                                                                                                                              |

| V <sub>DD</sub> 4  | 2      | Р    | +3.3 Volt power supply, video interface                                                                                                                                   |

| V <sub>DD</sub> A  | 1      | Α    | +3.3 Volt power supply, Analog, memory interface                                                                                                                          |

| V <sub>DD</sub> AX | 2      | Α    | +3.3 Volt power supply, Analog, Xtal. Oscillator and PLL.                                                                                                                 |

| V <sub>DD</sub> AR | 1      | Α    | +3.3 Volt power supply, Analog, Red                                                                                                                                       |

| V <sub>DD</sub> AG | 1      | Α    | +3.3 Volt power supply, Analog, Green                                                                                                                                     |

| V <sub>DD</sub> AB | 1      | Α    | +3.3 Volt power supply, Analog, Blue                                                                                                                                      |

| V <sub>DD</sub> AD | 2      | A    | +3.3 Volt power supply, Analog, DAC                                                                                                                                       |

| Δ DD√D             |        | ^    | 13.0 VOIL POWER SUPPLY, ATIAIOY, DAG                                                                                                                                      |

Table 9. Mpact R Media Processor Signal Description (Continued)

| NAME                | NUMBER      | TYPE                               | DESCRIPTION                                            |  |  |

|---------------------|-------------|------------------------------------|--------------------------------------------------------|--|--|

| $V_{GND}$           | 22          | Р                                  | Power supply ground, core                              |  |  |

| V <sub>GND</sub> 1  | 3           | Р                                  | Power supply ground, display interface                 |  |  |

| V <sub>GND</sub> 2  | 6           | Р                                  | Power supply ground, PCI bus interface                 |  |  |

| V <sub>GND</sub> 3  | 4           | Р                                  | Power supply ground, peripheral interface              |  |  |

| V <sub>GND</sub> 4  | 2           | Р                                  | Power supply ground, video interface                   |  |  |

| V <sub>GND</sub> A  | 1           | Α                                  | Power supply ground, Analog, memory interface          |  |  |

| $V_{GND}AX$         | 2           | Α                                  | Power supply ground, Analog, Xtal. Oscillator and PLL. |  |  |

| V <sub>GND</sub> AR | 1           | Α                                  | Power supply ground, Analog, Red                       |  |  |

| V <sub>GND</sub> AG | 1           | Α                                  | Power supply ground, Analog, Green                     |  |  |

| V <sub>GND</sub> AB | 1           | Α                                  | Power supply ground, Analog, Blue                      |  |  |

| V <sub>GND</sub> AD | 2           | A Power supply ground, Analog, DAC |                                                        |  |  |

|                     | TOTAL (240) |                                    |                                                        |  |  |

# **SPECIFICATIONS**

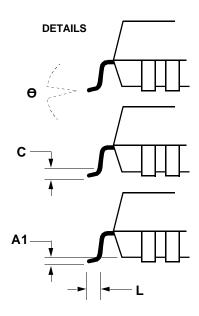

# Packaging - Pinout

Table 10. Mpact R Media Processor Pin Number By Signal Name

| Pin Name | Pin<br>Number | Pin Name  | Pin<br>Number  | Pin Name            | Pin<br>Number | Pin Name | Pin<br>Number |

|----------|---------------|-----------|----------------|---------------------|---------------|----------|---------------|

|          |               |           | Display Int    | erface (13)         |               |          | •             |

| DRED     | 237           | DHS       | 220            | DCOMP               | 227           | DXOUT    | 214           |

| DGRN     | 234           | DBLNK     | 219            | DCLKI               | 208           |          |               |

| DBLUE    | 231           | DVREF     | 225            | DCLKO               | 209           |          |               |

| DVS      | 222           | DRSET     | 226            | DXIN                | 213           |          |               |

|          |               |           | Video Inte     | erface (22)         |               |          | •             |

| VDATA15  | 137           | VDATA9    | 127            | VDATA3              | 117           | VODD     | 111           |

| VDATA14  | 136           | VDATA8    | 126            | VDATA2              | 116           | VCREF    | 112           |

| VDATA13  | 135           | VDATA7    | 125            | VDATA1              | 115           | VHREF    | 113           |

| VDATA12  | 133           | VDATA6    | 124            | VDATA0              | 114           | VCLK     | 119           |

| VDATA11  | 131           | VDATA5    | 123            | VVS                 | 110           |          |               |

| VDATA10  | 129           | VDATA4    | 122            | VHS                 | 74            |          |               |

|          |               | Periph    | eral I/O Inte  | rface - Parallel (1 | 9)            | •        | <u> </u>      |

| PDATA7   | 139           | PDATA2    | 147            | PJYEN               | 182           | PPACK    | 184           |

| PDATA6   | 141           | PDATA1    | 149            | PAXEN               | 177           | PCSCK    | 185           |

| PDATA5   | 143           | PDATA0    | 152            | PREQH               | 179           | PCOCK    | 186           |

| PDATA4   | 144           | PPIEN     | 190            | PREQL               | 178           | PJYCK    | 183           |

| PDATA3   | 145           | PPOEN     | 192            | PPDCK               | 189           |          |               |

|          |               | Peripl    | neral I/O Inte | erface - Serial (16 | )             | •        | I             |