# SM501 MSOC<sup>тм</sup> Databook

Preliminary Version B-1 6/13/03

# SM501 MSOC<sup>TM</sup> Databook

### Notice

Silicon Motion<sup>®</sup>, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice. No responsibility is assumed by Silicon Motion, Inc. for the use of this information, nor for infringements of patents or other rights of third parties.

## **Copyright Notice**

Copyright, 2003 Silicon Motion, Inc. All rights reserved. No part of this publication may be reproduced, photocopied, or transmitted in any form, without the prior written consent of Silicon Motion, Inc. Silicon Motion, Inc. reserves the right to make changes to the product specification without reservation and without notice to our users.

| Version Number | Date    | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| B-1            | 6/13/03 | <ul> <li>Updated arrows in Figure 1-5 Hitachi SH4 to SM501 Bus Interface diagram</li> <li>Changed DRAM Control Register Bit 1</li> <li>Changed Table 17-2 Pin Descriptions B19 and B21 from Type O to I/O</li> <li>Changed Figure 18-10 SH4 Read Timing</li> <li>Changed Mode Select Register Bit 4</li> <li>Changed opening paragraph for 8051-Controlled External Bus Interface, and bit address modes.</li> <li>Miscellaneous Timing Changed bit 31:28 host clock and updated bit 23</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| В              | 4/8/03  | <ul> <li>Added Timing Waveforms and Parameter Tables to Specifications chapter<br/>Reformatted register descriptions</li> <li>Added Soldering Profile section to Chapter 18</li> <li>Replaced Voyager GX with SM501</li> <li>Updated 1:8 scaling in Chapter 1 with maximum power of 2 values (ZV Port<br/>and 2D Engine subsections)</li> <li>Updated arrows in Figure 10-1, ZV Port chapter</li> <li>Added Figure 17-1, Package Outline</li> <li>Renamed H18 to XTALPWR, D19 to PLLGND, E21 to PLLPWR</li> <li>Added new information in Chapter 2, under Power Mode Control register on<br/>PLLs, Power and Sleep Modes, Clock Frequency</li> <li>Added new field to bits [31:28] in Miscellaneous Timing register, Chapter 2</li> <li>Reorganized description of Configuration 1 &amp; 2 registers in Chapter 2</li> <li>Added 1st/2nd clock entries to Table 1-3</li> </ul> |  |  |

| A-1            | 2/14/03 | <ul> <li>Global change to delete space between Voyager and GX</li> <li>Added ZV Port Timing Diagram to Chapter 18</li> <li>Deleted Pin J9, K9, L9, M9, N9 from pinout diagram 17-1</li> <li>Changed opening paragraph in Chapter 17</li> <li>Added Company Confidential in header</li> <li>Changed version number</li> <li>Added Chapter Titles to footer</li> <li>Added limits to Table 18-1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

# **Table of Contents**

| Introduction                                       |       |

|----------------------------------------------------|-------|

| Overview                                           | . 1-1 |

| Typical System Block Diagram                       | . 1-2 |

| UMA Architectures                                  | . 1-3 |

| NAND Tree Scan Testing                             | . 1-4 |

| Internal Block Description                         | 1-5   |

| Host CPU Memory or PCI Interface                   | . 1-5 |

| Command Interpreter / Command List Processor       |       |

| Zoom Video Port                                    |       |

| 2D Engine                                          |       |

| Video Display Layers                               |       |

| LCD Panel                                          | 1-16  |

| Analog RGB (Analog LCD or CRT).                    |       |

| Internal or External Memory                        | 1-21  |

| GPIO                                               | 1-21  |

| Flat Panel Data                                    |       |

| USB Controllers                                    |       |

| DMA Controller.                                    |       |

| Interrupt Controller                               |       |

| Clock Control                                      |       |

| Power Management                                   |       |

| Memory Map and Register Space.                     |       |

| MMIO Space                                         |       |

| MMIO Addressing.                                   |       |

| System Configuration                               |       |

| Functional Description                             |       |

| Operational Register Descriptions                  |       |

| Summary of SM501 Configuration Registers           |       |

|                                                    |       |

| Configuration 1 Register Descriptions              |       |

| Command List Register Descriptions                 |       |

| Interrupt / Debug Register Descriptions            |       |

| Power Management Register Descriptions             |       |

| Configuration 2 Register Descriptions              |       |

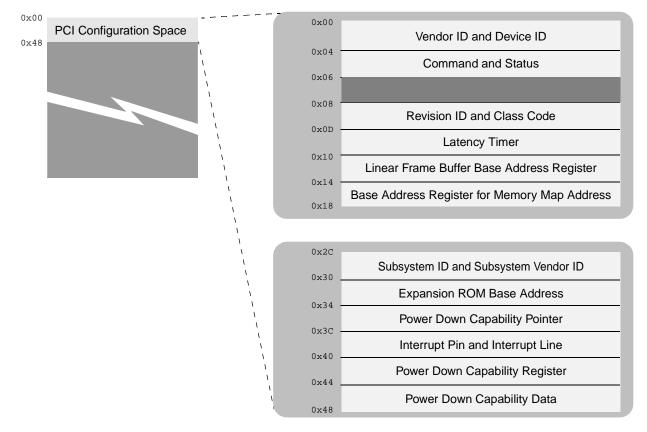

| PCI Configuration Space.                           |       |

| Operational Register Descriptions                  |       |

| Summary of SM501 PCI Configuration Space Registers |       |

| PCI Configuration Space Register Descriptions      |       |

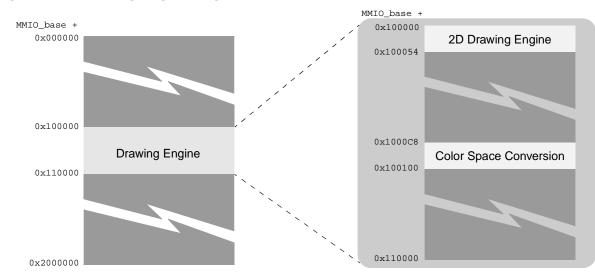

| Drawing Engine                                     |       |

| Functional Description                             |       |

| Operational Register Descriptions                  |       |

| About the Programmer's Model                       |       |

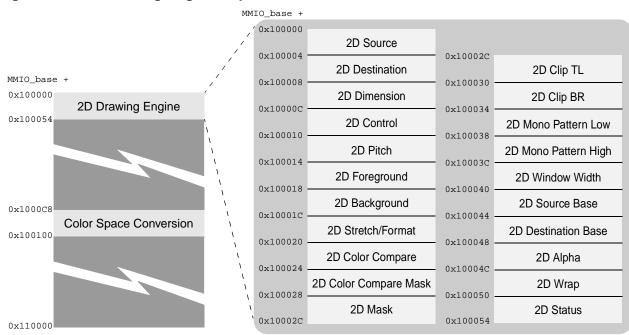

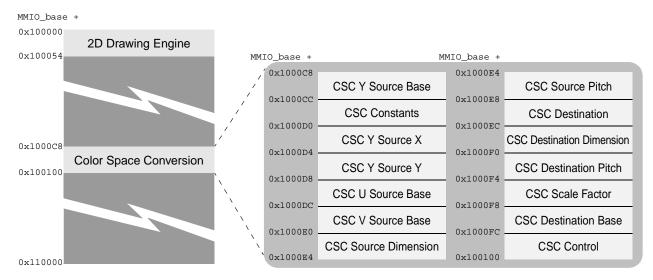

| Summary of Drawing Engine Registers                |       |

| Drawing Engine Register Descriptions               |       |

| Display Controller                                 |       |

| Operational Register Descriptions                  |       |

| About the Programmer's Model                       |       |

| Summary of Display Controller Registers.           |       |

| Display Controller Register Descriptions           |       |

| Command List Interpreter                           |       |

| Functional Description                             | . 6-1 |

|                       | ogramming                                          |       |

|-----------------------|----------------------------------------------------|-------|

|                       | ow Commands                                        |       |

|                       | ppending to the Command List                       |       |

|                       | tional Register Descriptions                       |       |

|                       | Immary of Command List Registers                   |       |

|                       | ommand List Register Descriptions                  |       |

|                       | ands                                               |       |

|                       | Dad Memory                                         |       |

|                       | Dad Register                                       |       |

|                       | Dad Memory Immediate                               |       |

|                       | Dad Register Immediate                             |       |

|                       | Dad Memory Indirect                                |       |

|                       | Dad Register Indirect                              |       |

|                       | atus Test                                          |       |

|                       | nish                                               |       |

|                       | oto                                                |       |

|                       | osub                                               |       |

|                       | eturn                                              |       |

|                       | onditional Jump                                    |       |

|                       |                                                    |       |

|                       | onal Description                                   |       |

|                       | tion Register Descriptions                         |       |

|                       | Immary of USB Host Controller Driver Registers     |       |

|                       | egister Descriptions                               |       |

|                       |                                                    |       |

|                       | ional Register Descriptions                        |       |

|                       | Immary of USB Device Internal Registers            |       |

|                       | egister Descriptions                               |       |

| GPIO/I <sup>2</sup> C |                                                    | . 9-1 |

|                       | onal Description.                                  |       |

|                       | PIO Overview                                       |       |

|                       | C Interface Overview                               |       |

|                       | tional Register Descriptions                       |       |

|                       | bout the Programmer's Model                        |       |

| Su                    | Immary of GPIO and I <sup>2</sup> C Registers      | . 9-2 |

|                       | PIO Register Descriptions                          |       |

| $I^2$                 | C Master Register Descriptions                     | . 9-8 |

| ZV Port               |                                                    |       |

|                       | onal Description                                   |       |

|                       | V Port Overview                                    |       |

|                       | ideo Capture Unit Overview                         |       |

|                       | tional Register Descriptions                       |       |

|                       | bout the Programmer's Model                        |       |

|                       | Immary of ZV Port Registers                        |       |

|                       | V Port Register Descriptions                       |       |

|                       | k & I <sup>2</sup> S                               |       |

| Functi                | onal Description.                                  | 11-1  |

|                       | C97-Link and I <sup>2</sup> S Interface Overview   |       |

|                       | tional Register Descriptions                       |       |

|                       | bout the Programmer's Model.                       |       |

|                       | Immary of AC97-Link and I <sup>2</sup> S Registers |       |

|                       | C97-Link Register Descriptions                     |       |

| 1~                    | S Register Descriptions                            | 11-12 |

| 8051 µ-Controller                                      | 12-1    |

|--------------------------------------------------------|---------|

| Functional Description                                 |         |

| 8051 μ-Controller Overview                             | . 12-1  |

| Operational Register Descriptions                      | 12-2    |

| About the Programmer's Model                           |         |

| Summary of 8051 µ-Controller Registers                 |         |

| 8051 μ-Controller Register Descriptions                |         |

| 8051 µ-Controller SRAM Address Space                   |         |

| 8051-Controlled External Bus Interface                 |         |

| Example of Implementation of MOST for Automotive Usage |         |

| DMA Controller (DMAC)                                  |         |

| Functional Description                                 |         |

| DMA Controller Overview                                |         |

| Operational Register Descriptions                      |         |

| Summary of DMA Controller Registers                    |         |

| DMA Controller Register Descriptions                   |         |

| Functional Description                                 |         |

| UART Overview                                          |         |

| UART0/UART1 Functional Description.                    |         |

| UART Timings                                           |         |

| Operational Register Descriptions                      |         |

| Summary of UART and IrDA Registers                     |         |

| Register Descriptions.                                 |         |

| Synchronous Serial Port                                |         |

| Functional Description                                 |         |

| SSP Overview                                           |         |

| SSP Operation                                          | . 15-2  |

| Operational Register Descriptions                      | . 15-14 |

| Summary of SSP Registers                               | 15-14   |

| SSP Register Descriptions                              |         |

| Interrupts                                             |         |

| PWM Specification                                      |         |

| Functional Description                                 |         |

| PWM Overview.                                          |         |

| Operational Register Descriptions                      |         |

| Summary of PWM Registers                               |         |

| PWM Register Descriptions                              |         |

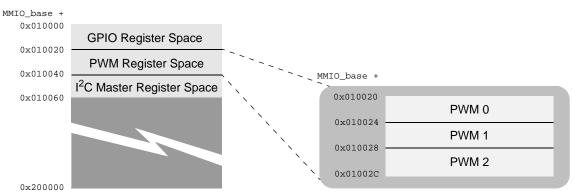

| Pin & Packaging Information                            |         |

| Packaging                                              |         |

| Signal List                                            |         |

| Pinout Pin Descriptions                                |         |

| Specifications                                         |         |

| Environmental.                                         |         |

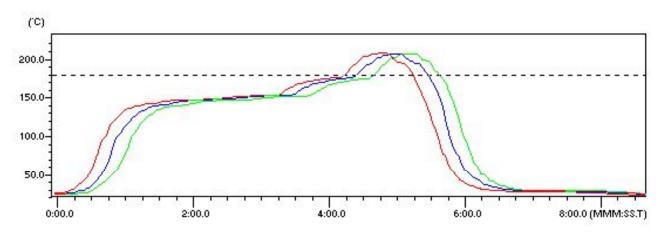

| Soldering Profile                                      |         |

| DC Characteristics                                     |         |

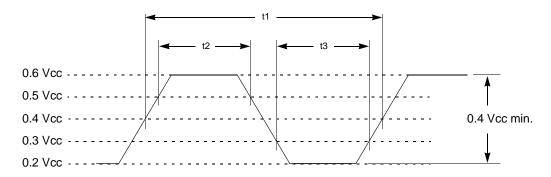

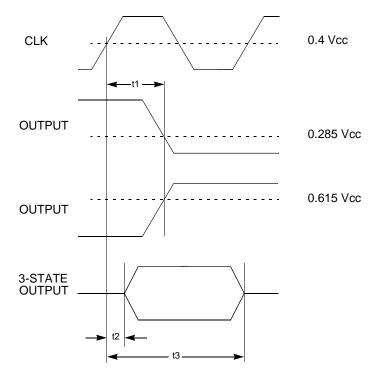

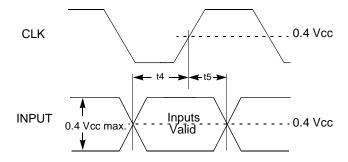

| AC Timing                                              |         |

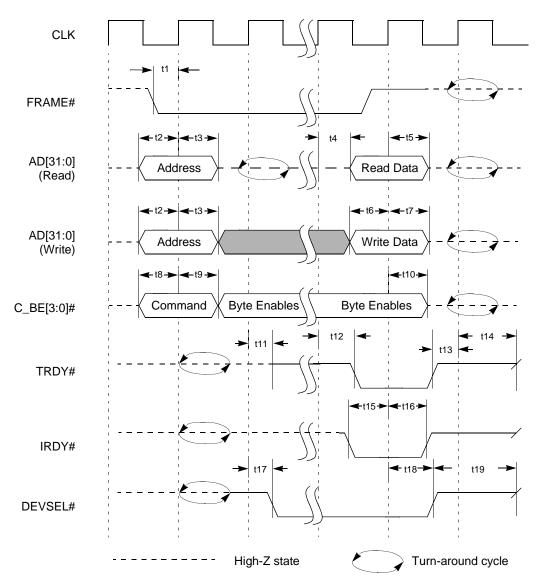

| PCI Interface Timing                                   |         |

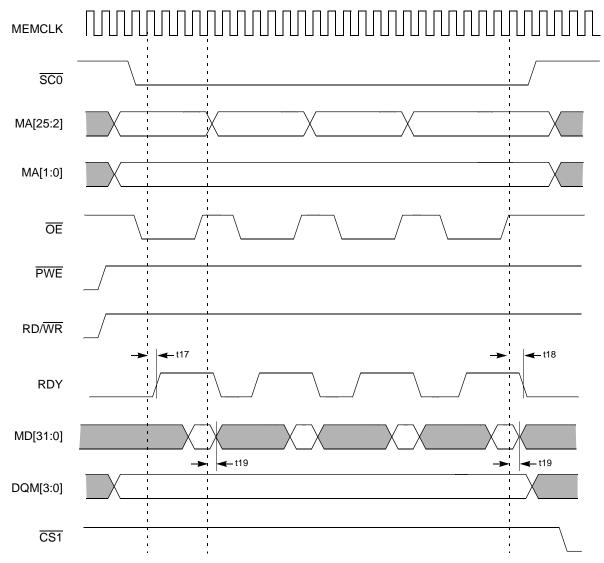

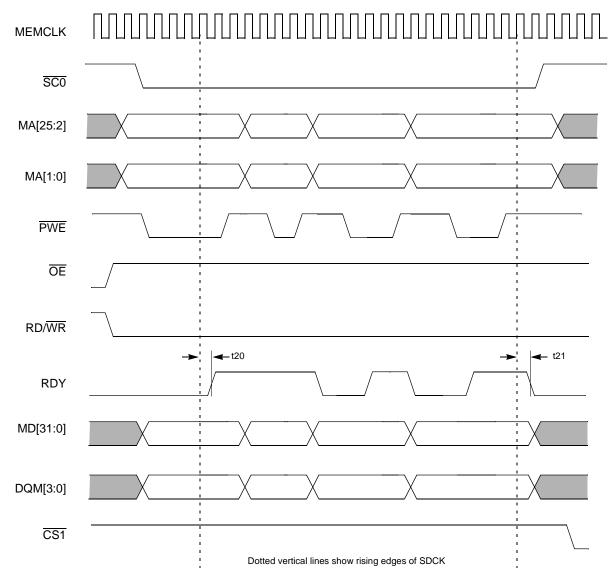

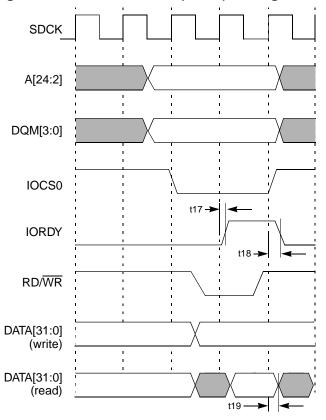

| Host Interface Timing                                  |         |

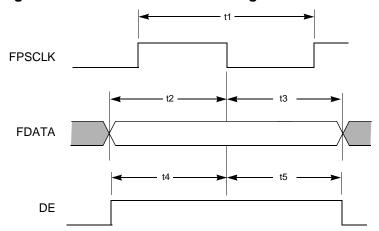

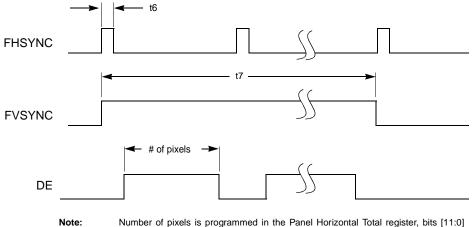

| Display Controller Timing.                             | 18-16   |

| USB Interface Timing                                   | 18-18   |

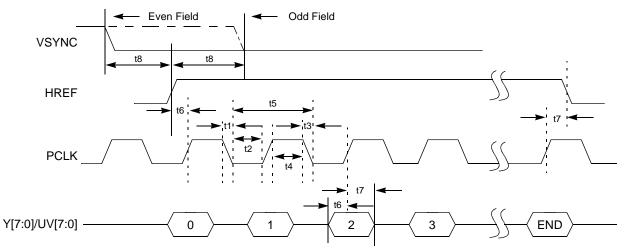

| ZV Port Timing                                         | 18-19   |

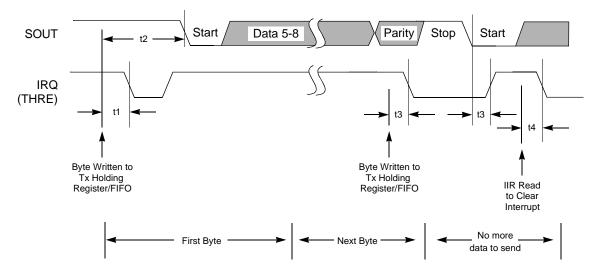

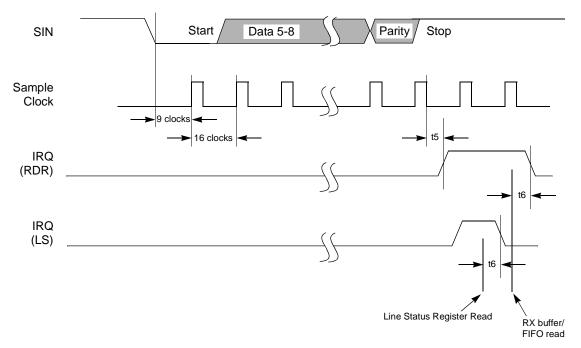

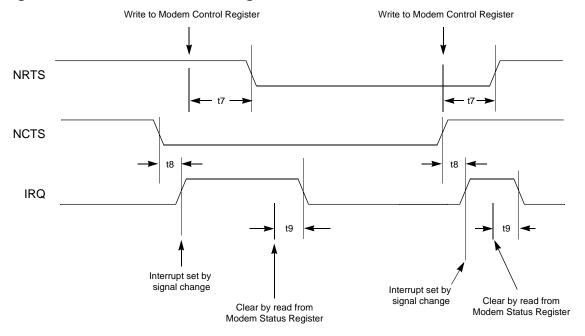

| UART Timing                                            | 18-20   |

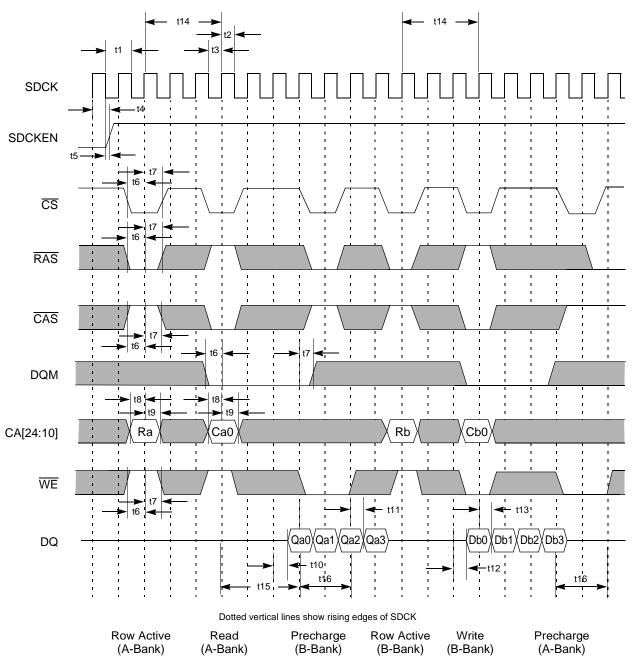

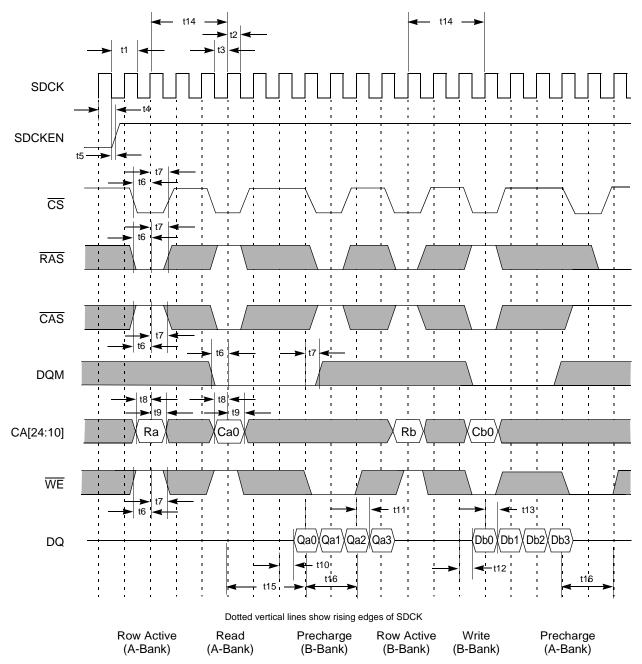

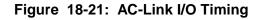

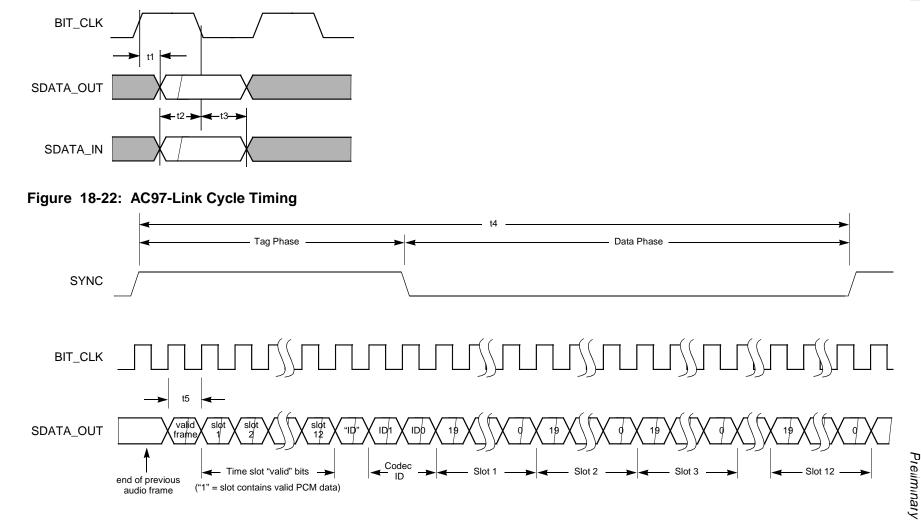

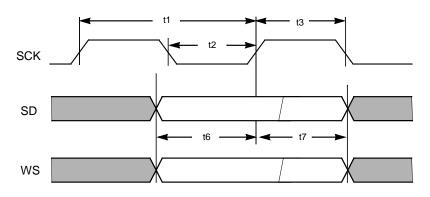

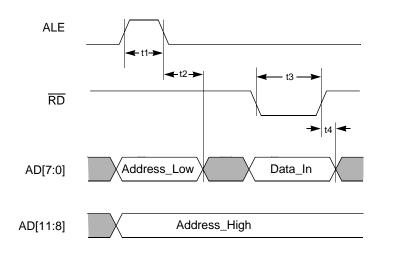

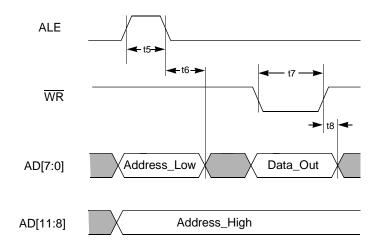

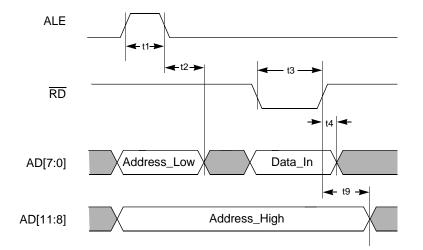

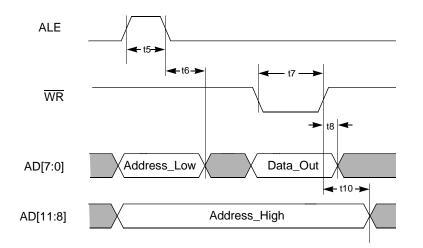

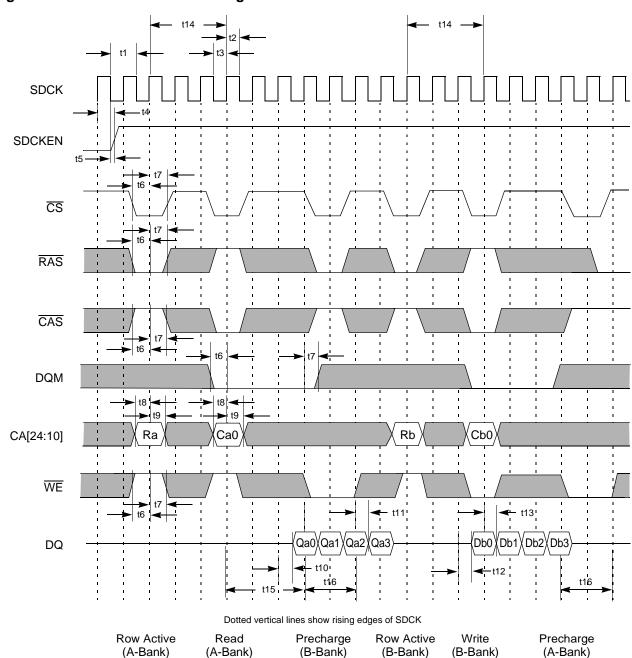

# AC97-Link and I<sup>2</sup>S Timing 18-22 8051 μ-Controller Timing 18-25 Local SDRAM Timing 18-28

# **List of Figures**

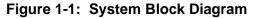

| Figure 1-1:  | System Block Diagram                                 | 1-1  |

|--------------|------------------------------------------------------|------|

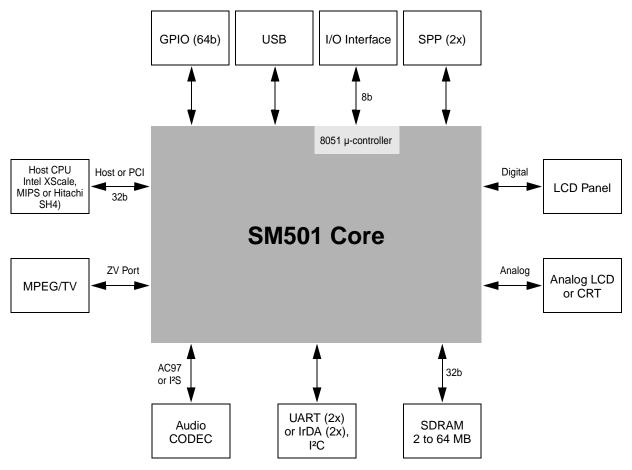

| Figure 1-2:  | Example System Diagram                               | 1-2  |

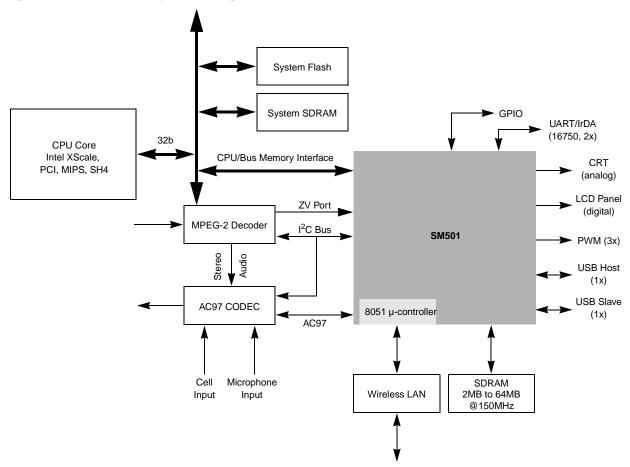

| Figure 1-3:  | System Configurations                                | 1-3  |

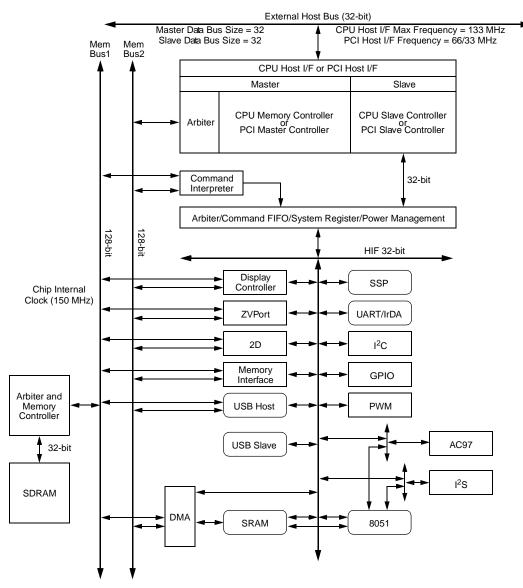

| Figure 1-4:  | Internal Block Diagram                               | 1-5  |

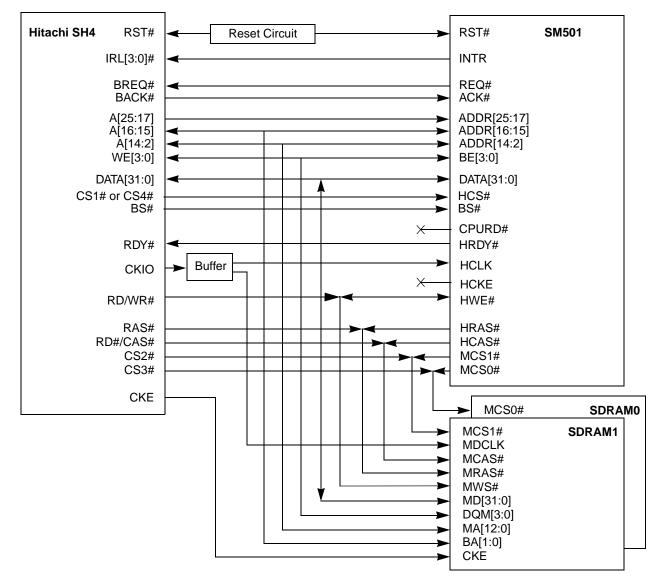

| Figure 1-5:  | Hitachi SH4 to the SM501 Bus Interface               | 1-8  |

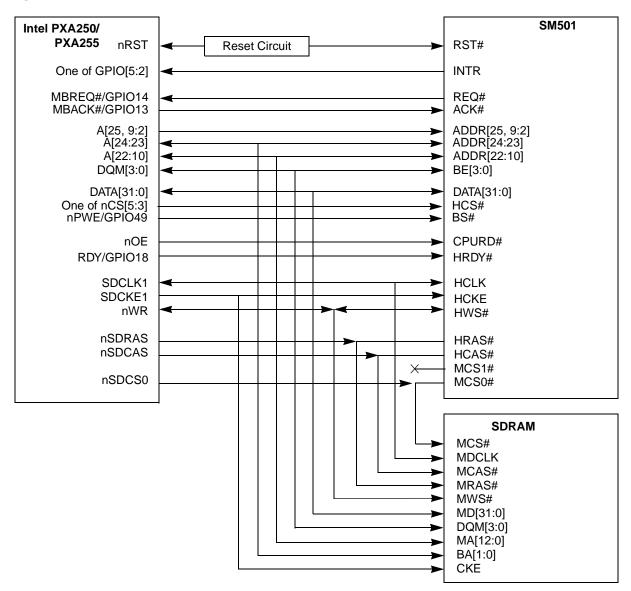

| Figure 1-6:  | Intel XScale (PXA250/255) to the SM501 Bus Interface | 1-9  |

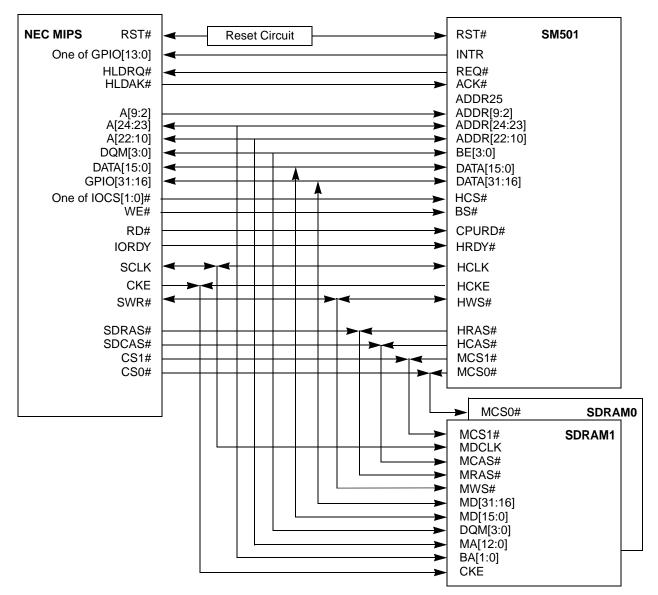

| Figure 1-7:  | NEC MIPS to the SM501 Bus Interface                  | 1-11 |

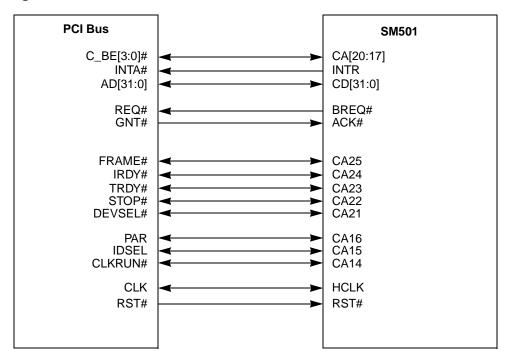

| Figure 1-8:  | PCI Bus Interconnection                              | 1-12 |

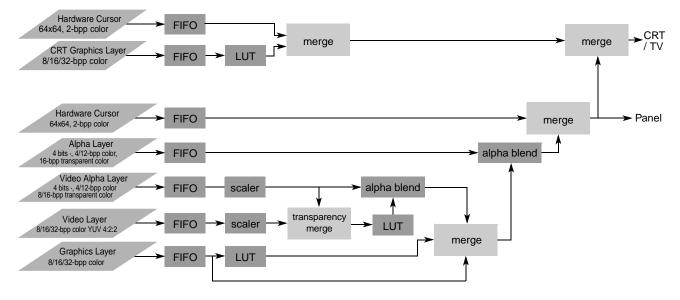

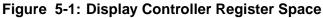

| Figure 1-9:  | Video Layers and Data Processing                     | 1-14 |

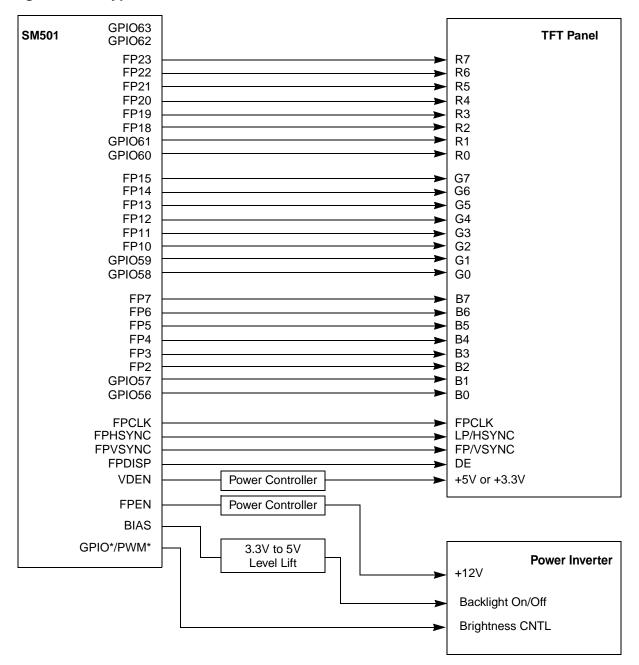

| Figure 1-10: | Typical 24-bit TFT Panel Interface                   | 1-17 |

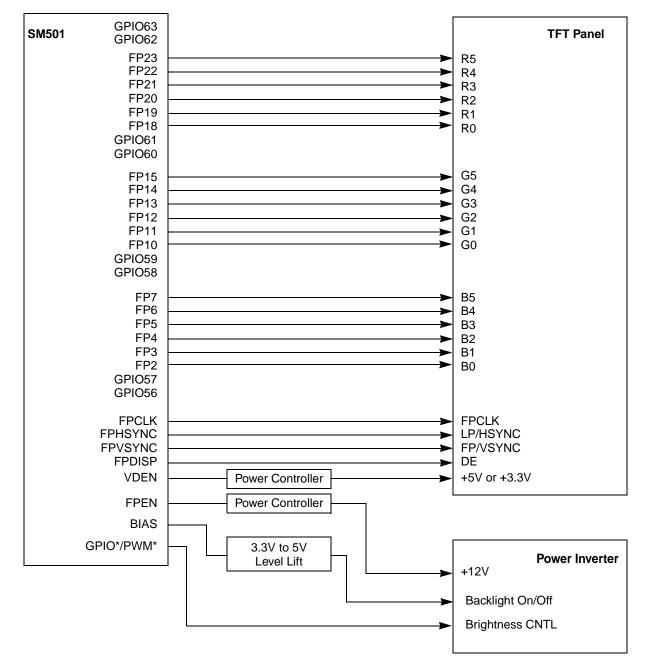

| Figure 1-11: | Typical 18-bit TFT Panel Interface                   | 1-18 |

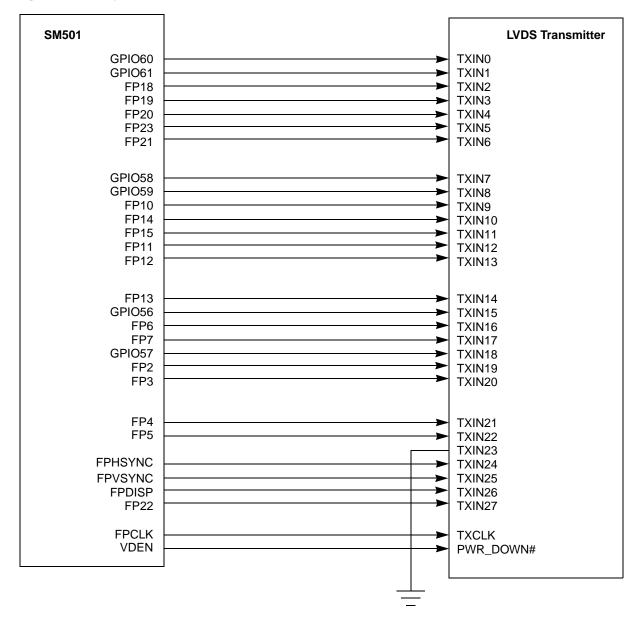

| Figure 1-12: | Typical 24-bit LVDS Interface (DS90C385)             | 1-19 |

| Figure 1-13: | GPIO Layout                                          | 1-21 |

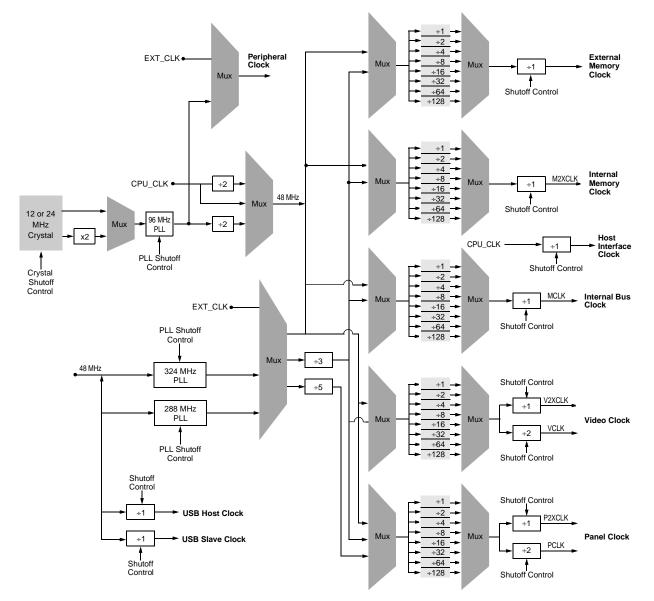

| Figure 1-14: | Clock Tree                                           | 1-25 |

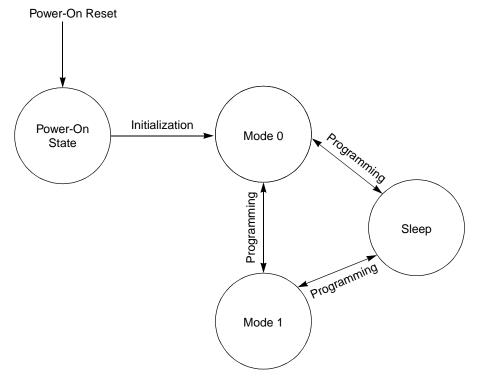

| Figure 1-15: | Power State Diagram                                  | 1-26 |

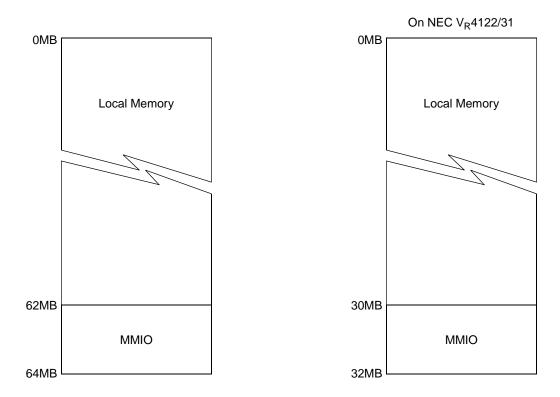

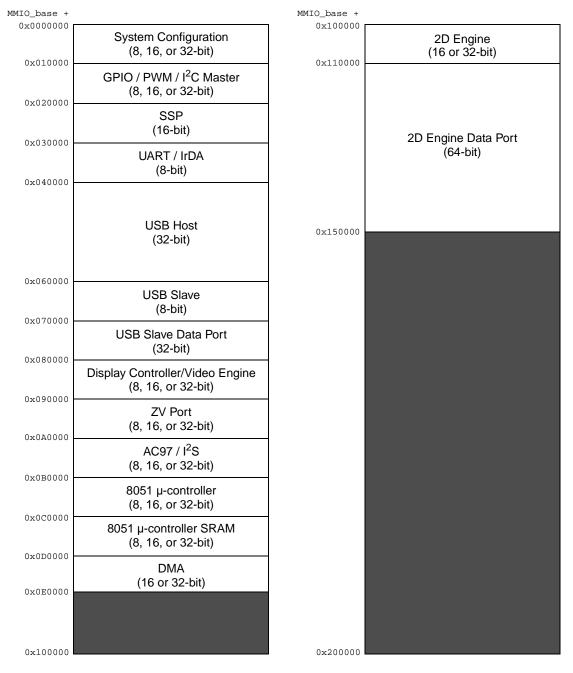

| Figure 1-16: | Memory Map                                           | 1-27 |

| Figure 1-17: | MMIO Space                                           | 1-28 |

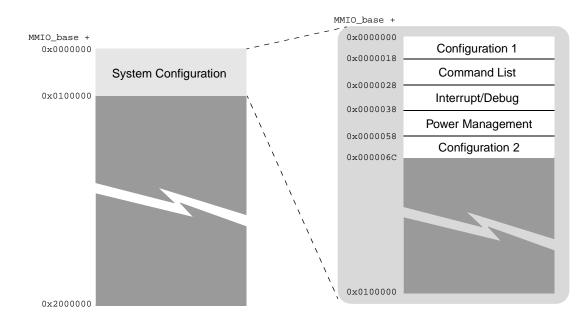

| Figure 2-1:  | System Configuration Register Space                  | 2-2  |

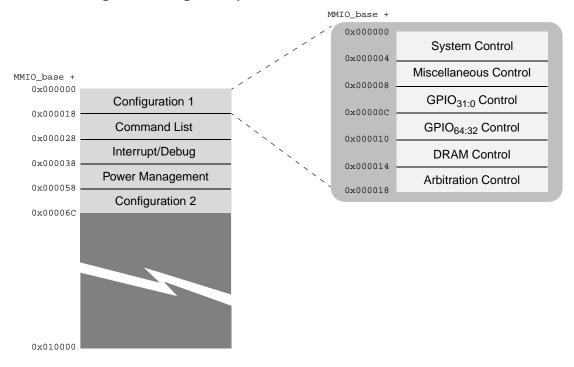

| Figure 2-2:  | Configuration Register Space 1                       | 2-4  |

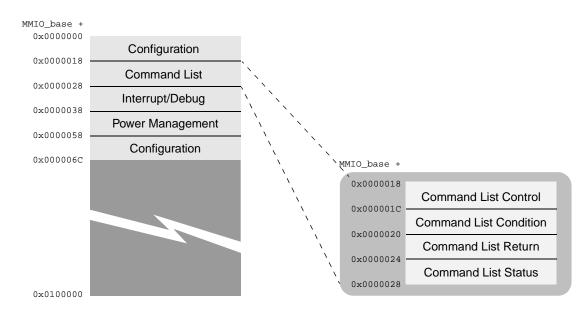

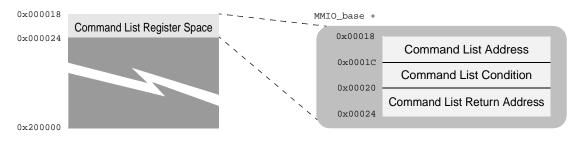

| Figure 2-3:  | Command List Register Space                          | 2-17 |

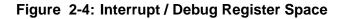

| Figure 2-4:  | Interrupt / Debug Register Space                     | 2-21 |

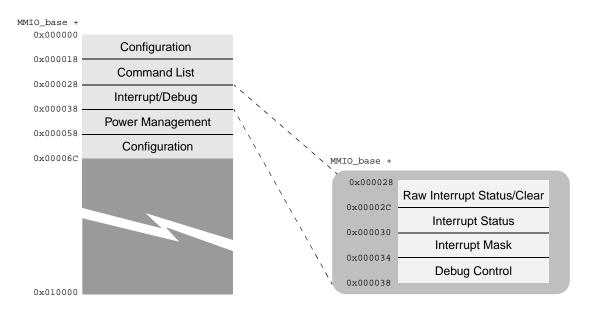

| Figure 2-5:  | Power Management Register Space                      | 2-28 |

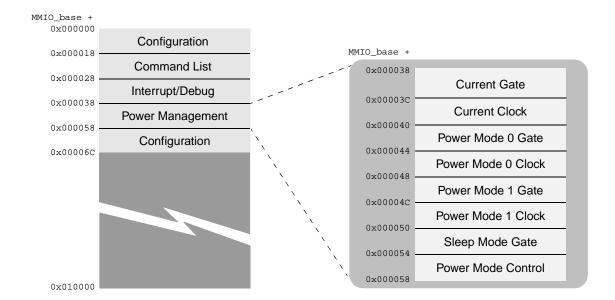

| Figure 2-6:  | Configuration Register Space 2                       | 2-41 |

| Figure 3-1:  | PCI Configuration Register Space                     | 3-2  |

| Figure 4-1:  | Drawing Engine Register Space                        | 4-2  |

| Figure 4-2:  | 2D Drawing Register Space                            | 4-4  |

| Figure 4-3:  | Color Space Conversion Register Space                | 4-18 |

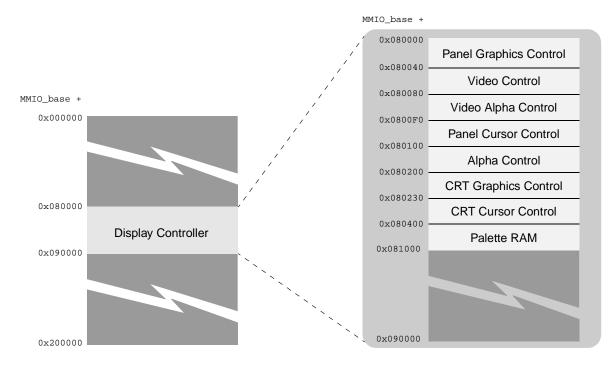

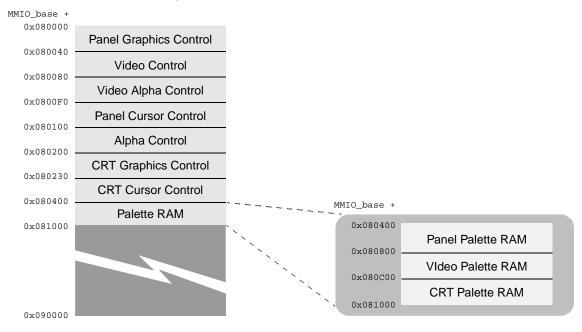

| Figure 5-1:  | Display Controller Register Space                    | 5-5  |

| Figure 5-2:  | Video Layers                                         | 5-5  |

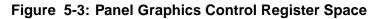

| Figure 5-3:  | Panel Graphics Control Register Space                | 5-6  |

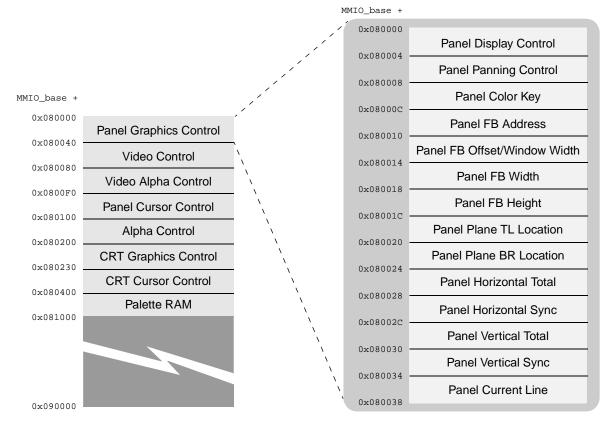

| Figure 5-4:  | Video Windowing                                      | 5-7  |

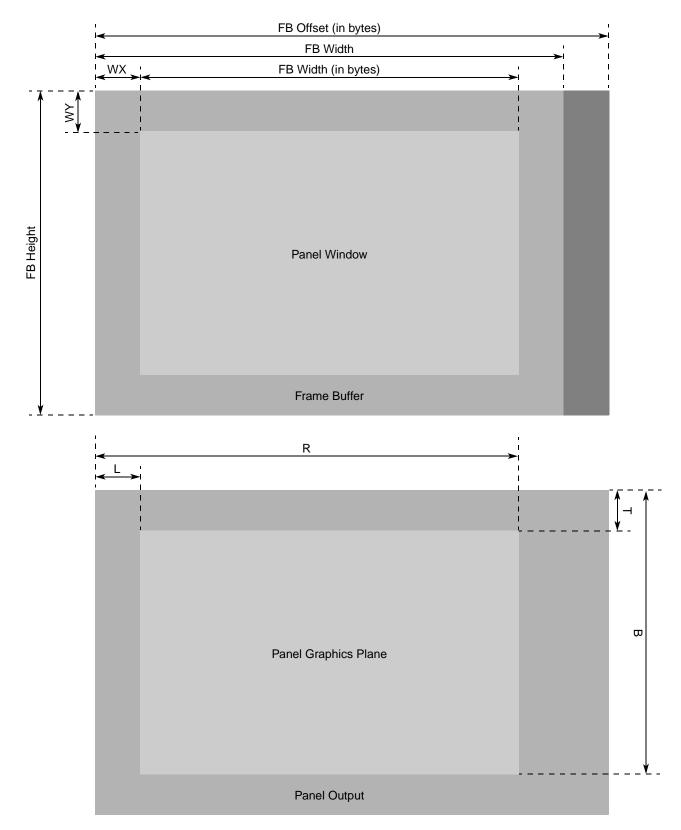

| Figure 5-5:  | Video Control Register Space                         | 5-17 |

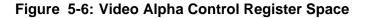

| Figure 5-6:  | Video Alpha Control Register Space                   | 5-26 |

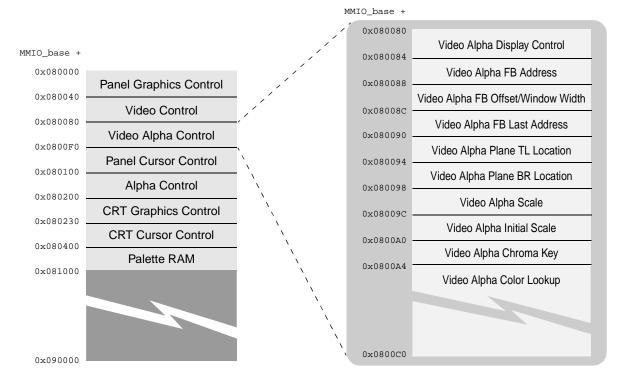

| Figure 5-7:  | Panel Cursor Control Register Space                  | 5-33 |

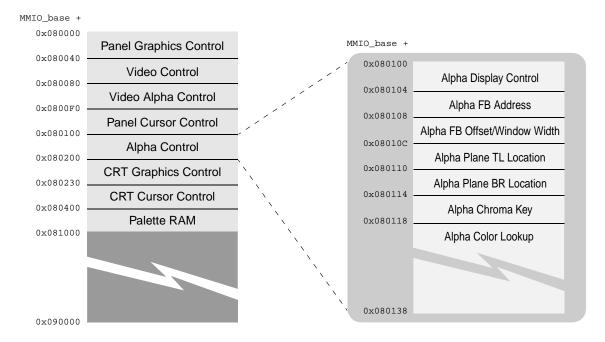

| Figure 5-8:  | Alpha Control Register Space                         | 5-36 |

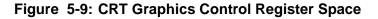

| Figure 5-9:  | CRT Graphics Control Register Space                  |      |

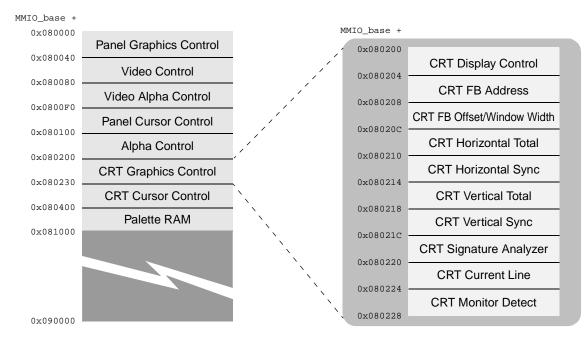

| Figure 5-10: | CRT Cursor Control Register Space                    | 5-49 |

| Figure 5-11: | Palette RAM Register Space                           | 5-52 |

| Figure 6-1:  | Command List Register Space                          | 6-3  |

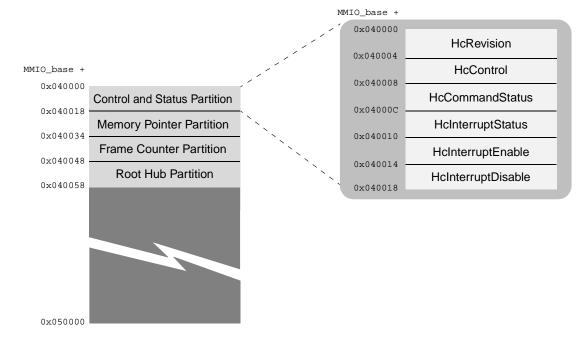

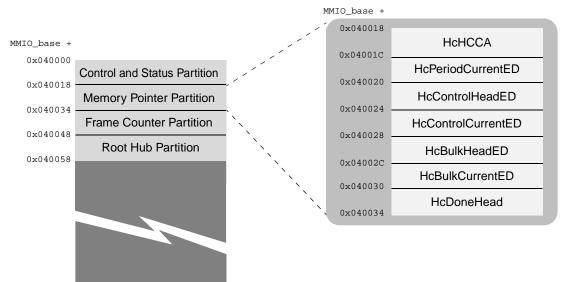

| Figure 7-1:  | USB Control and Status Partition Register Space      | 7-4  |

| Figure 7-2:  | USB Memory Pointer Partition Register Space          | 7-12 |

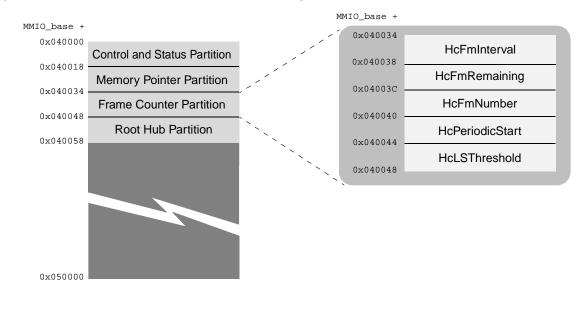

| Figure 7-3:  | USB Frame Counter Partition Register Space           |      |

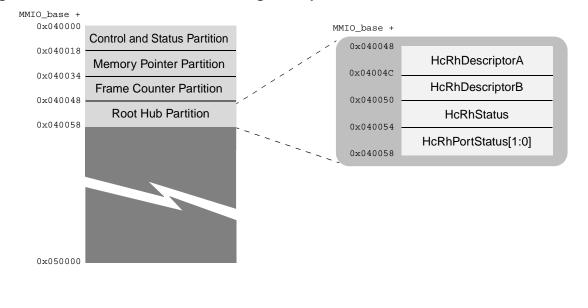

| Figure 7-4:  | USB Root Hub Partition Register Space                | 7-24 |

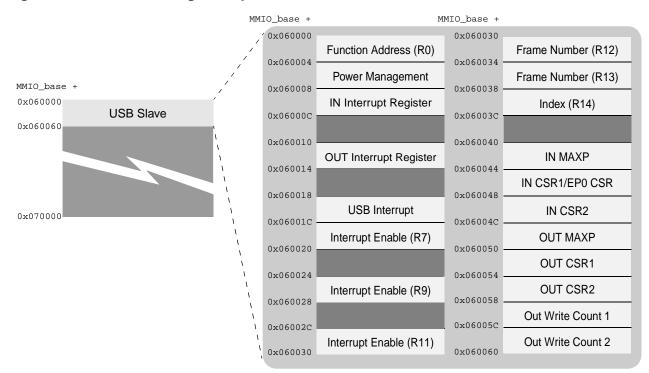

| Figure 8-1:  | USB Slave Register Space                             | 8-4  |

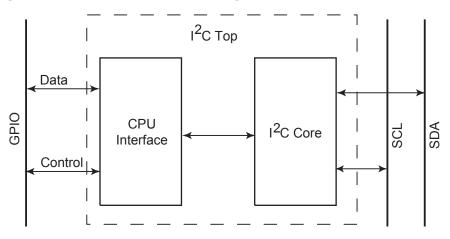

| Figure 9-1:  | I <sup>2</sup> C Interface Block Diagram             | 9-1  |

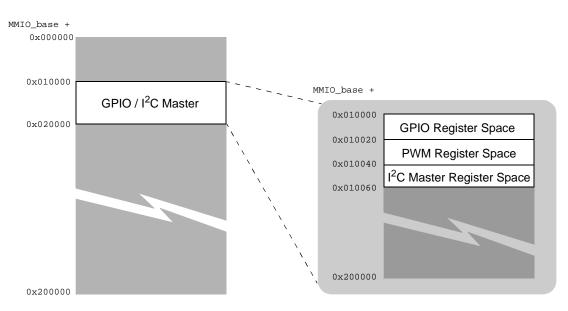

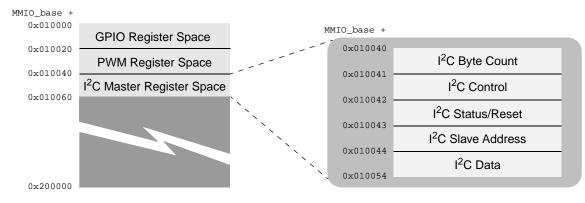

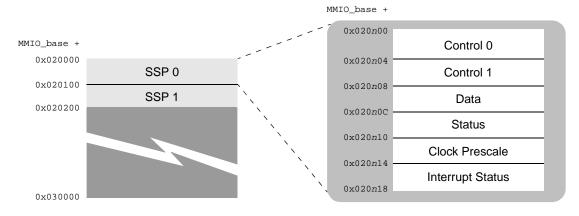

| Figure 9-2:  | GPIO / I <sup>2</sup> C Master Register Space        |      |

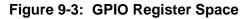

| Figure 9-3:          | GPIO Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9-3   |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 9-4:          | I <sup>2</sup> C Master Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

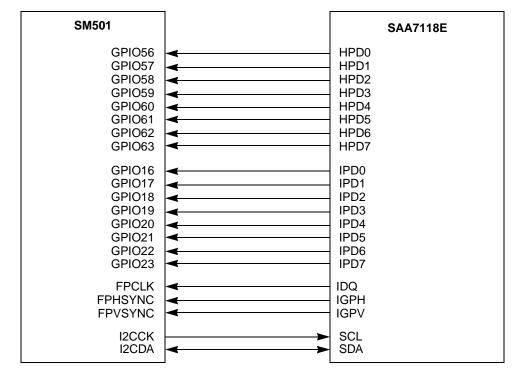

| Figure 10-1:         | Video Encoder Interface through the Video Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

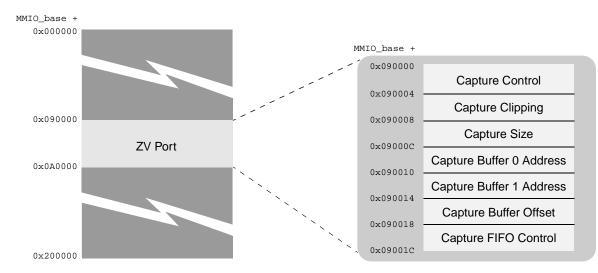

| Figure 10-1:         | ZV Port Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

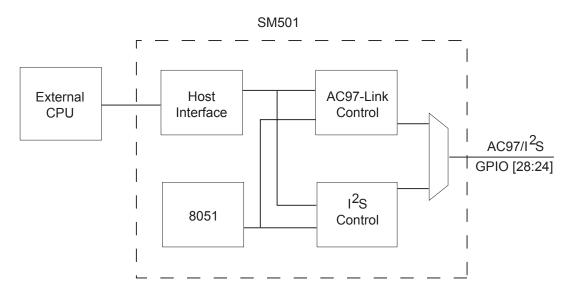

| Figure 11-1:         | AC97-Link and I <sup>2</sup> S Interface Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

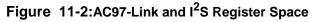

| Figure 11-2:         | AC97-Link and I <sup>2</sup> S Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

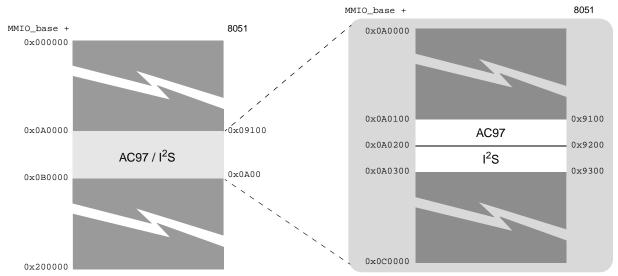

| Figure 11-2:         | AC97-Link Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

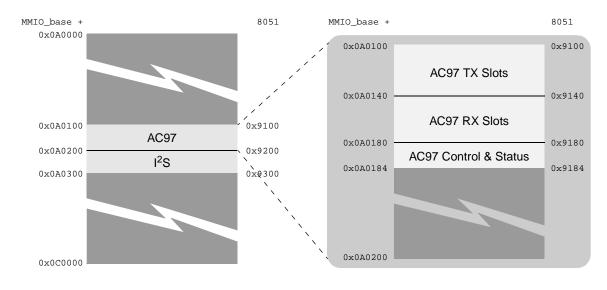

| Figure 11-4:         | I <sup>2</sup> S Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

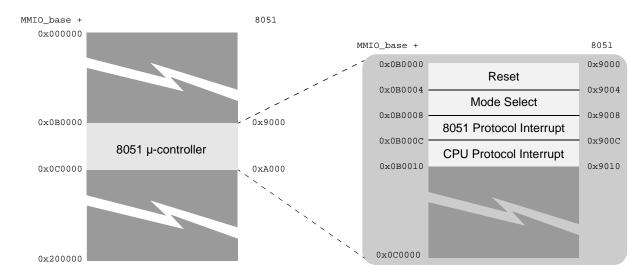

| Figure 12-1:         | 8051 μ-Controller Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

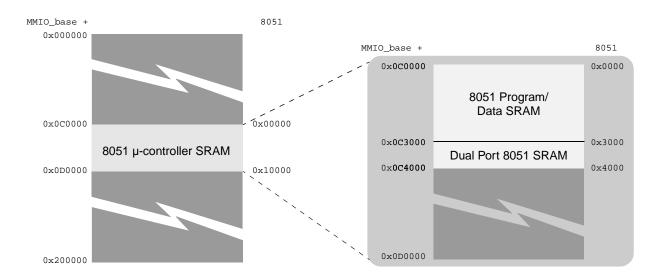

| Figure 12-2:         | 8051 μ-Controller SRAM Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

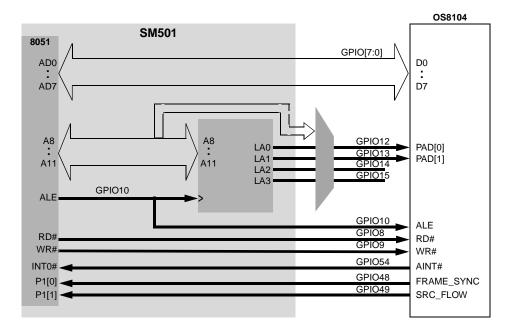

| Figure 12-3:         | 8051 μ-Controller to MOST Controller Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

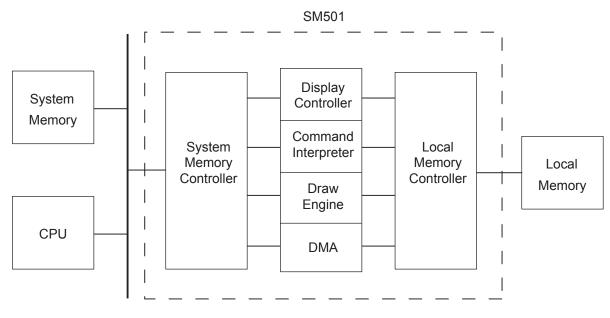

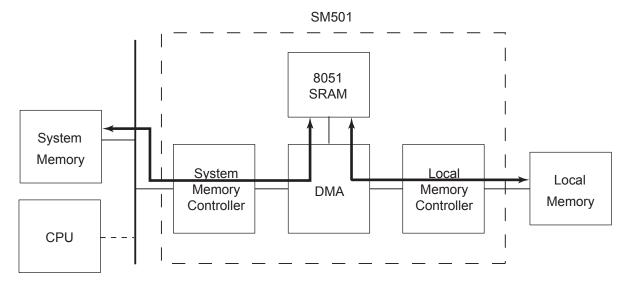

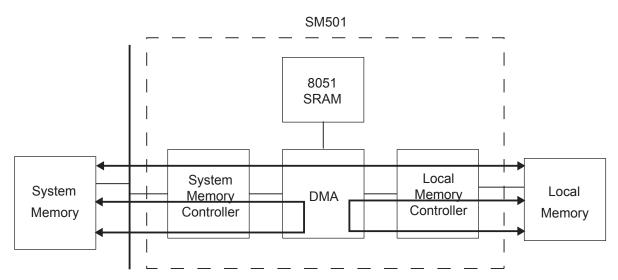

| Figure 13-1:         | SM501 Functional Block Connections to Memory Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| Figure 13-2:         | DMA Channel 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| Figure 13-3:         | DMA Channel 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

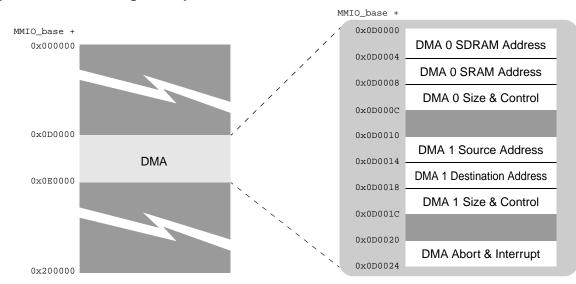

| Figure 13-4:         | DMA Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

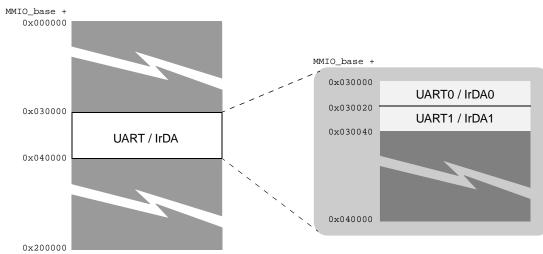

| Figure 14-1:         | UART and IrDA Register Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

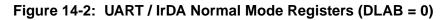

| Figure 14-2:         | UART / IrDA Normal Mode Registers ( $DLAB = 0$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

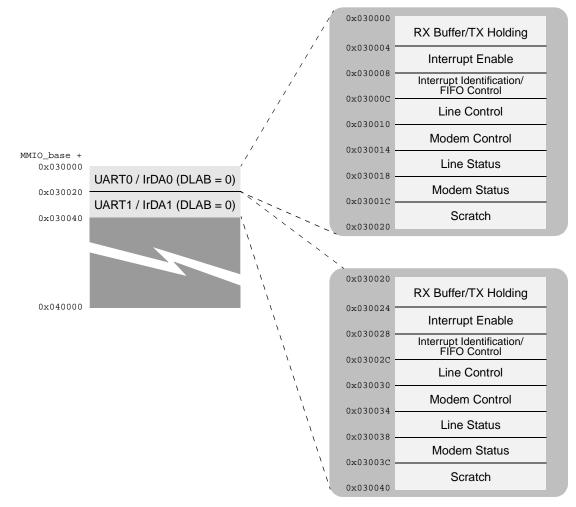

| Figure 14-3:         | Configuration Mode Registers (DLAB = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

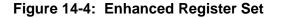

| Figure 14-4:         | Enhanced Register Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

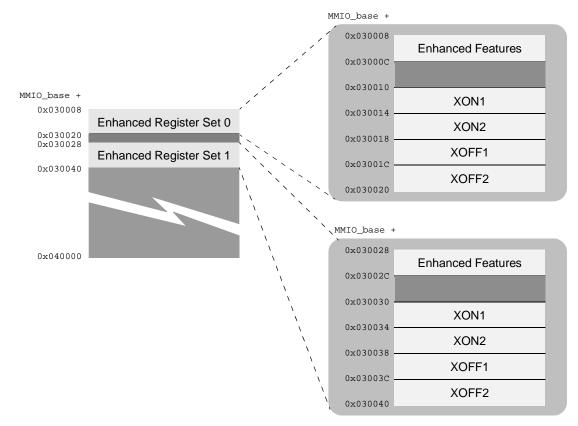

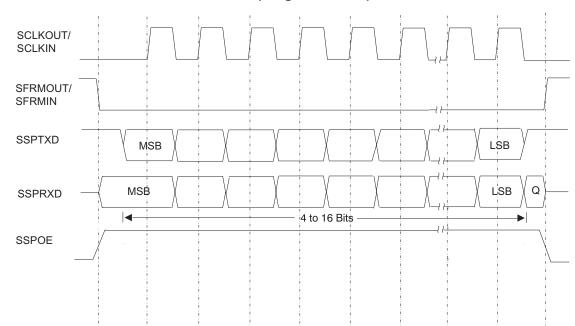

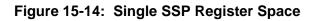

| Figure 15-1:         | Texas Instruments Synchronous Serial Frame Format (Single Transfer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

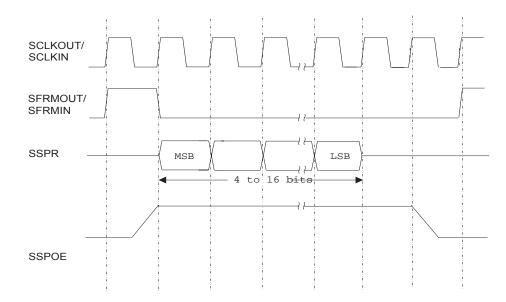

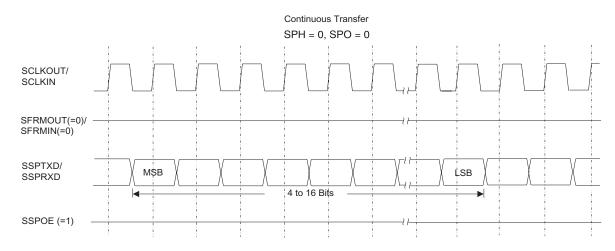

| Figure 15-2:         | TI Synchronous Serial Frame Format (Continuous Transfer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

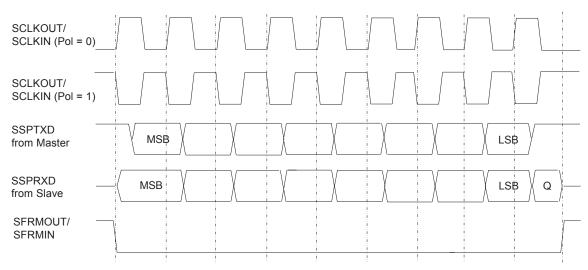

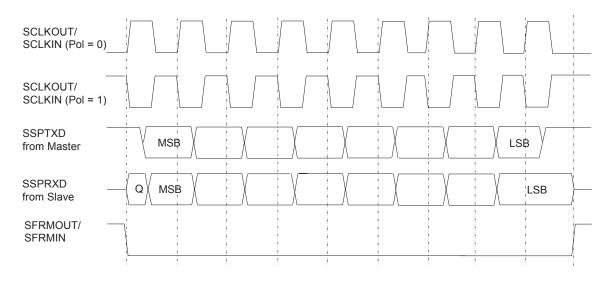

| Figure 15-3:         | Motorola SPI Frame Format (Single Transfer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| Figure 15-4:         | Motorola SPI Frame Format (Continuous Transfer) $SPO = 0$ , $SPH = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| Figure 15-5:         | Motorola SPI Frame Format with $Ph = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| Figure 15-6:         | Motorola SPI Frame Format with Ph = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

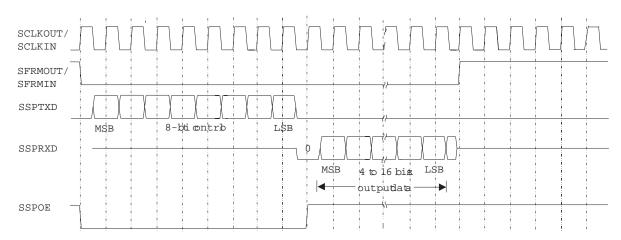

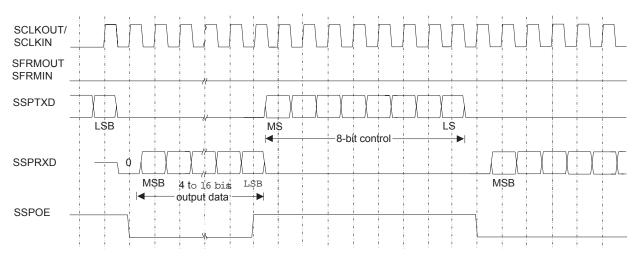

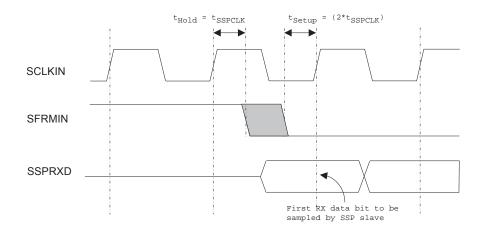

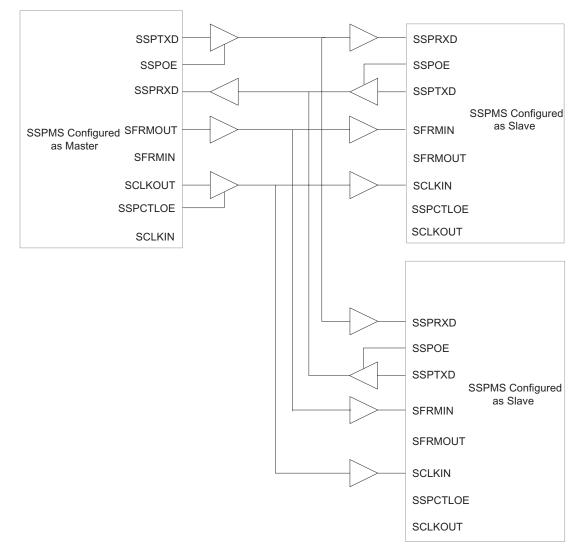

| Figure 15-7:         | Microwire Frame Format, Single Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |