TR25202

# Pyramid3D<sup>™</sup> 3D Accelerator

#### **Features**

- Full 10-component RGB model support

- · Radiosity lighting support

- High integration, including video refresh, clock synthesizer and true-color DAC

- Unified buffer architecture for efficient memory utilization

- Perspective correction for both texture and truecolor shading

- Complex shading effects including bump mapping and specular lighting

- Multiple simultaneous lighted textures with filtering

- Programmable pixel pipeline

# Applications

- 3D GUI/game accelerators for MPC

- · 3D media accelerators for MPC motherboard

- 3D accelerators for arcade

- 3D accelerators for home TV game-console

- Industrial virtual reality simulators

- Military war-game simulators

# **General Description**

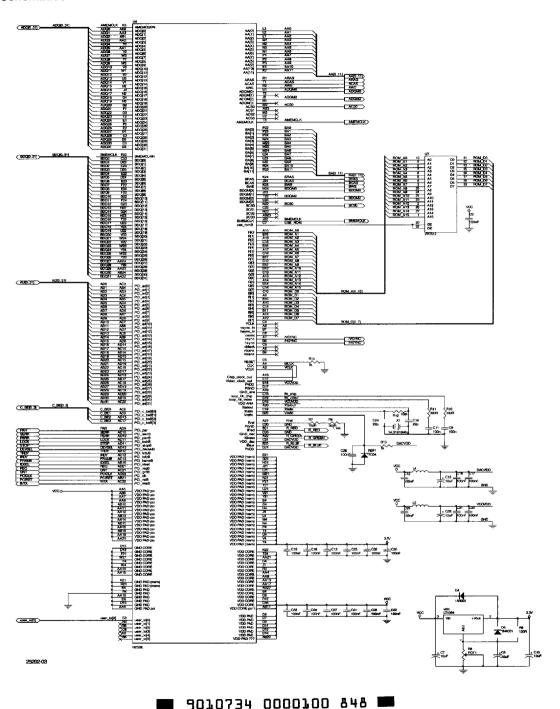

TR25202 is a member of TriTech's *Pyramid3D*™ family of highly integrated, programmable, and high performance 3D graphics accelerators. It is designed for the acceleration of games, 3D applications and user interfaces. It offers full compatibility with the emerging 3D standards including Direct3D™ for Windows® 95 and OpenGL™ for Windows NT.

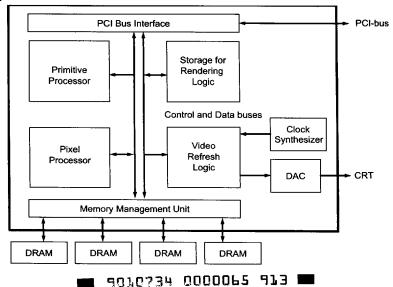

TR25202 integrates on a single chip the primitive processor, pixel processor, PCI bus master interface, memory management unit, video refresh logic, clock synthesizer, and true-color DAC.

The features of TR25202 form a solid base on which support for different 3D APIs can be built easily. A full 3D graphics system requires only memory, in addition to TR25202. A low cost system is possible with two 256K x 32 SGRAMs or EDO DRAMs.

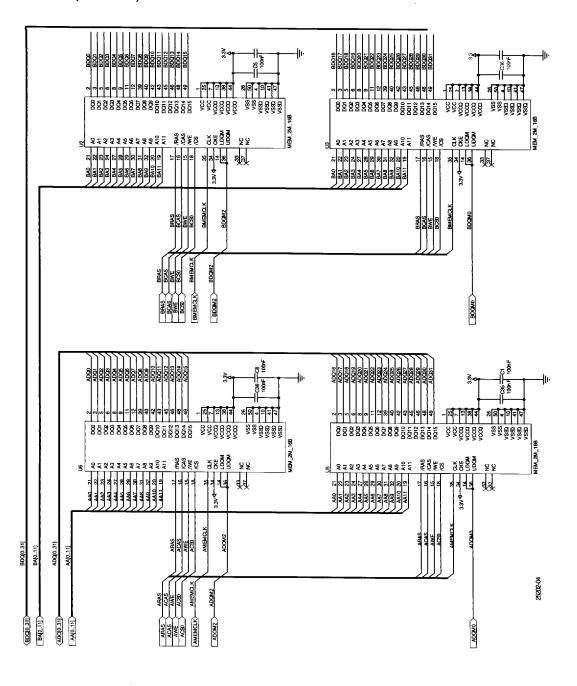

## **Block Diagram**

©1997 TriTech Microelectronics, Inc.

Revision 2.4 Jan 97

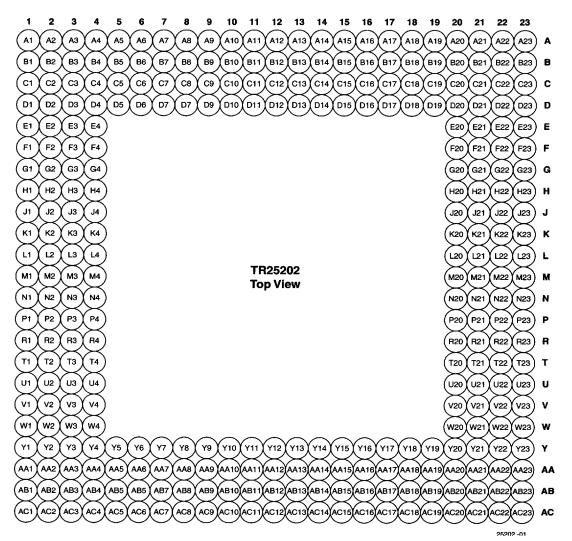

# **Pin Configuration**

TR25202 is packaged in a 304-pin Thermal Enhanced Ball Grid Array (TEBGA). The pinout top and bottom views are shown below, followed by the pin assignment table:

Figure 1 • TR25202 Pinout (Top View)

| 9010734 | 0000066 | 85T |  |

|---------|---------|-----|--|

|         |         |     |  |

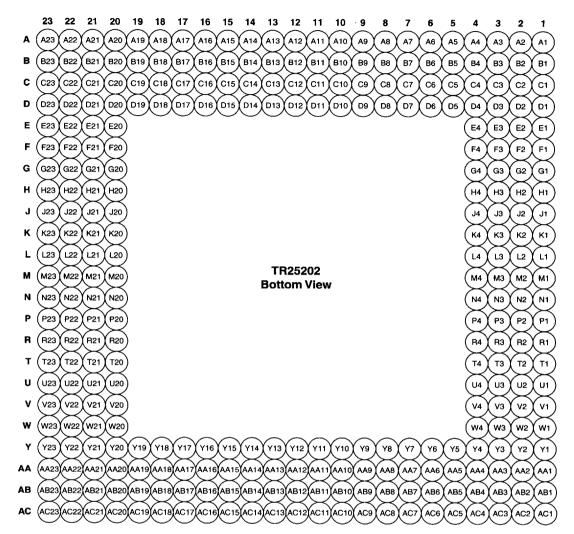

# Pin Configuration (continued)

Figure 2 • TR25202 Pinout (Bottom View)

| = | 9010734 | 0000067 | 796 |  |

|---|---------|---------|-----|--|

|   |         |         |     |  |

# Pin Assignments

|            | 1/0  |           |             |

|------------|------|-----------|-------------|

| Pin        | Туре | Category  | Name        |

| A1         | out  | B-memory  | BCS[3]      |

| A2         | GND  |           |             |

| <b>A</b> 3 | 1/0  | video     | VREF        |

| A4         | 1    | clock gen | XTAL_IN     |

| <b>A</b> 5 | VDD  | 5V        |             |

| A6         | GND  |           |             |

| <b>A</b> 7 | 1    | clock gen | CLK_TST[1]  |

| A8         | ı    | clock gen | CLK_TST[0]  |

| A9         | 0    | video     | PCLK        |

| A10        | 0    | video     | VSYNC       |

| A11        | ı    | video     | VSYNC_IN    |

| A12        | 1/0  |           | USER_IO[2]  |

| A13        | 1/0  |           | USE_ROMB    |

| A14        | 0    | video     | G[5]        |

| A15        | 0    | video     | G[2]        |

| A16        | 0    | video     | R[7]        |

| A17        | 0    | video     | R[4]        |

| A18        | 0    | video     | R[2]        |

| A19        | 0    | video     | R[0]        |

| A20        | 0    | video     | B[5]        |

| A21        | 0    | video     | B[2]        |

| A22        | 0    | video     | B[1]        |

| A23        | 0    | video     | B[0]        |

| B1         | 0    | B-memory  | BCS[2]      |

| B2         | 0    | video     | IBLUE       |

| В3         | 0    | video     | IGREEN      |

| B4         | GND  |           |             |

| B5         |      | clock gen | FILTER_PROS |

| B6         | GND  |           |             |

| B7         | 1/0  | clock gen | VIDEO_CLK   |

| B8         | 0    | video     | CSYNC       |

| B9         | 0    |           | HBLANK      |

| B10        | 0    |           | CBLANK      |

| B11        | 1    | video     | HSYNC_IN    |

| B12        | 1/0  | video     | USER_IO[3]  |

| B13        | 1/0  | video     | USER_IO[0]  |

| B14        | 0    | video     | G[6]        |

| Pin | I/O<br>Type | Category  | Name         |

|-----|-------------|-----------|--------------|

| B15 | 0           | video     | G[3]         |

| B16 | 0           | video     | G[0]         |

| B17 | 0           | video     | R[5]         |

| B18 | 0           | video     | R[3]         |

| B19 | 0           | video     | R[1]         |

| B20 | 0           | video     | B[6]         |

| B21 | 0           | video     | B[3]         |

| B22 | 0           | A-memory  | ACS[1]       |

| B23 | 0           | A-memory  | ACS[0]       |

| C1  | 1/0         | B-memory  | BDQ[2]       |

| C2  | 1/0         | B-memory  | BDQ[1]       |

| СЗ  | 1/0         | B-memory  | BDQ[0]       |

| C4  | VDD         | 5V        |              |

| C5  | 0           | video     | IRED         |

| C6  | 0           | clock gen | XTAL_OUT     |

| C7  |             | clock gen | FILTER_VIDEO |

| C8  | 0           | video     | HSYNC        |

| C9  | VDD         | 5V        |              |

| C10 | 0           |           | VBLANK       |

| C11 | GND         |           |              |

| C12 | 1/0         |           | USER_IO[4]   |

| C13 | 1/0         |           | USER_IO[1]   |

| C14 | 0           | video     | G[7]         |

| C15 | 0           | video     | G[4]         |

| C16 | 0           | video     | G[1]         |

| C17 | 0           | video     | R[6]         |

| C18 | GND         |           |              |

| C19 | VDD         | 5V        |              |

| C20 | 0           | video     | B[7]         |

| C21 | 0           | video     | B[4]         |

| C22 | 1/0         | A-memory  | ADQ[30]      |

| C23 | 1/0         | A-memory  | ADQ[31]      |

| D1  | I/O         | B-memory  | BDQ[4]       |

| D2  | 1/0         | B-memory  | BDQ[3]       |

| D3  | GND         |           |              |

| D4  | VDD         | 5V        |              |

| D5  | GND         |           |              |

**=** 9010734 0000068 622 **==** :

| Pin | I/O<br>Type | Category  | Name     |

|-----|-------------|-----------|----------|

| D6  | 1/0         | video     | RREF     |

| D7  | VDD         | 5V        |          |

| D8  | I/O         | clock gen | PROS_CLK |

| D9  | GND         |           |          |

| D10 | VDD         | 5V        |          |

| D11 | VDD         | 5V        |          |

| D12 | VDD         | 5V        |          |

| D13 | VDD         | 5V        |          |

| D14 | GND         |           |          |

| D15 | VDD         | 5V        |          |

| D16 | GND         |           |          |

| D17 | VDD         | 5V        |          |

| D18 | GND         |           |          |

| D19 | VDD         | 5V        |          |

| D20 | 1/0         | A-memory  | ADQ[26]  |

| D21 | 1/0         | A-memory  | ADQ[27]  |

| D22 | 1/0         | A-memory  | ADQ[28]  |

| D23 | 1/0         | A-memory  | ADQ[29]  |

| E1  | 1/0         | B-memory  | BDQ[7]   |

| E2  | 1/0         | B-memory  | BDQ[6]   |

| E3  | I/O         | B-memory  | BDQ[5]   |

| E4  | VDD         | memory    |          |

| E20 | GND         |           |          |

| E21 | I/O         | A-memory  | ADQ[23]  |

| E22 | 1/0         | A-memory  | ADQ[24]  |

| E23 | I/O         | A-memory  | ADQ[25]  |

| F1  | I/O         | B-memory  | BDQ[10]  |

| F2  | I/O         | B-memory  | BDQ[9]   |

| F3  | I/O         | B-memory  | BDQ[8]   |

| F4  | GND         |           |          |

| F20 | VDD         | memory    |          |

| F21 | I/O         | A-memory  | ADQ[20]  |

| F22 | 1/0         | A-memory  | ADQ[21]  |

| F23 | 1/0         | A-memory  | ADQ[22]  |

| G1  | 1/0         | B-memory  | BDQ[13]  |

| G2  | 1/0         | B_memory  | BDQ[12]  |

| G3  | I/O         | B-memory  | BDQ[11]  |

| Pin | I/O<br>Type | Category | Name      |

|-----|-------------|----------|-----------|

| G4  | VDD         | memory   | -         |

| G21 | I/O         | A-memory | ADQ[17]   |

| G22 | 1/0         | A-memory | ADQ[18]   |

| G23 | 1/0         | A-memory | ADQ[19]   |

| H1  | 0           | B-memory | BDQM[3]   |

| H2  | 1/0         | B-memory | BDQ[15]   |

| H3  | I/O         | B-memory | BDQ[14]   |

| H4  | VDD         | memory   |           |

| H20 | VDD         | memory   |           |

| H21 | 1           | A-memory | AMEMCLKIN |

| H22 | 0           | A-memory | AMEMCLK   |

| H23 | 1/0         | A-memory | ADQ[16]   |

| J1  | 0           | B-memory | BA[11]    |

| J2  | 0           | B-memory | BDQM[2]   |

| J3  | GND         |          |           |

| J4  | VDD         | 5V       |           |

| J20 | GND         |          |           |

| J21 | GND         |          |           |

| J22 | 0           | A-memory | ARAS      |

| J23 | 0           | A-memory | AWE       |

| K1  | 0           | B-memory | BA[8]     |

| K2  | 0           | B-memory | BA[9]     |

| КЗ  | 0           | B-memory | BA[10]    |

| K4  | GND         |          |           |

| k20 | VDD         | 5V       |           |

| K21 | 0           | A-memory | ACAS      |

| K22 | 0           | A-memory | ADQM[1]   |

| K23 | 0           | A-memory | ADQM[0]   |

| L1  | 0           | B-memory | BA[6]     |

| L2  | 0           | B-memory | BA[7]     |

| L3  | VDD         | memory   |           |

| L4  | VDD         | memory   |           |

| L20 | VDD         | memory   |           |

| L21 | 0           | A-memory | AA[2]     |

| L22 | 0           | A-memory | AA[1]     |

| L23 | 0           | A-memory | AA[0]     |

| M1  | 0           | B-memory | BA[3]     |

- 📟 9010734 0000069 569 📟 --

| Pin | I/O<br>Type | Category | Name      |

|-----|-------------|----------|-----------|

|     |             |          |           |

| M2  | 0           | B-memory | BA[4]     |

| M3  | 0           | B-memory | BA[5]     |

| M4  | GND         |          |           |

| M20 | GND         |          |           |

| M21 | 0           | A-memory | AA[5]     |

| M22 | 0           | A-memory | AA[4]     |

| M23 | 0           | A-memory | AA[3]     |

| N1  | 0           | B-memory | BA[0]     |

| N2  | 0           | B-memory | BA[1]     |

| N3  | 0           | B-memory | BA[2]     |

| N4  | VDD         | memory   |           |

| N20 | VDD         | memory   |           |

| N21 | VDD         | memory   |           |

| N22 | 0           | A-memory | AA[7]     |

| N23 | 0           | A-memory | AA[6]     |

| P1  | 0           | B-memory | BDQM[0]   |

| P2  | 0           | B-memory | BDQM[1]   |

| P3  | 0           | B-memory | BCAS      |

| P4  | VDD         | 5V       |           |

| P20 | GND         |          |           |

| P21 | 0           | A-memory | AA[10]    |

| P22 | 0           | A-memory | AA[9]     |

| P23 | 0           | A-memory | AA[8]     |

| R1  | 0           | B-memory | BWE       |

| R2  | 0           | B-memory | BRAS      |

| R3  | GND         |          |           |

| R4  | GND         |          |           |

| R20 | VDD         | 5V       |           |

| R21 | GND         |          |           |

| R22 | 0           | A-memory | ADQM[2]   |

| R23 | 0           | A-memory | AA[11]    |

| T1  | I/O         | B-memory | BDQ[16]   |

| T2  | 0           | B-memory | BMEMCLK   |

| Т3  | 1           | B-memory | BMEMCLKIN |

| T4  | VDD         | memory   |           |

| T20 | VDD         | memory   |           |

| T21 | 1/0         | A-memory | ADQ[14]   |

| Pin | I/O<br>Type | Category | Name    |

|-----|-------------|----------|---------|

| T22 | 1/0         | A-memory | ADQ[15] |

| T23 | 0           | A-memory | ADQM[3] |

| U1  | 1/0         | B-memory | BDQ[19] |

| U2  | 1/0         | B-memory | BDQ[18] |

| U3  | 1/0         | B-memory | BDQ[17] |

| U4  | GND         |          |         |

| U20 | VDD         | memory   |         |

| U21 | 1/0         | A-memory | ADQ[11] |

| U22 | 1/0         | A-memory | ADQ[12] |

| U23 | 1/0         | A-memory | ADQ[13] |

| V1  | I/O         | B-memory | BDQ[22] |

| V2  | 1/0         | B-memory | BDQ[21] |

| V3  | 1/0         | B-memory | BDQ[20] |

| V4  | VDD         | memory   |         |

| V20 | GND         |          |         |

| V21 | 1/0         | A-memory | ADQ[8]  |

| V22 | 1/0         | A-memory | ADQ[9]  |

| V23 | 1/0         | A-memory | ADQ[10] |

| W1  | 1/0         | B-memory | BDQ[25] |

| W2  | 1/0         | B-memory | BDQ[24] |

| W3  | 1/0         | B-memory | BDQ[23] |

| W4  | GND         |          |         |

| W20 | VDD         | memory   |         |

| W21 | 1/0         | A-memory | ADQ[5]  |

| W22 | 1/0         | A-memory | ADQ[6]  |

| W23 | 1/0         | A-memory | ADQ[7]  |

| Y1  | I/O         | B-memory | BDQ[29] |

| Y2  | 1/0         | B-memory | BDQ[28] |

| Y3  | I/O         | B-memory | BDQ[27] |

| Y4  | 1/0         | B-memory | BDQ[26] |

| Y5  | VDD         | PCI      |         |

| Y6  | GND         |          |         |

| Y7  | VDD         | PCI      |         |

| Y8  | GND         |          |         |

| Y9  | VDD         | PCI      |         |

| Y10 | GND         |          |         |

| Y11 | VDD         | PCI      |         |

· 🖿 9010734 0000070 280 🖿 -

| Pin  | I/O<br>Type | Category      | Name         |

|------|-------------|---------------|--------------|

| Y12  | VDD         | 5V            |              |

| Y13  | GND         |               |              |

| Y14  | VDD         | PCI           |              |

| Y15  | GND         |               |              |

| Y16  | GND         |               |              |

| Y17  | VDD         | PCI           |              |

| Y18  | VDD         | 5V            |              |

| Y19  | GND         |               |              |

| Y20  | VDD         | PCI           |              |

| Y21  | GND         |               |              |

| Y22  | 1/0         | A-memory      | ADQ[3]       |

| Y23  | 1/0         | A-memory      | ADQ[4]       |

| AA1  | 1/0         | B-memory      | BDQ[31]      |

| AA2  | 1/0         | B-memory      | BDQ[30]      |

| AA3  | 1           | PCI interface | PCI_CLK      |

| AA4  | 1/0         | PCI interface | PCI_AD[29]   |

| AA5  | GND         |               |              |

| AA6  | GND         |               |              |

| AA7  | VDD         | pci           |              |

| AA8  | VDD         | 5V            |              |

| AA9  | 1/0         | PCI interface | PCI_AD[21]   |

| AA10 | 1/0         | PCI interface | PCI_AD[17]   |

| AA11 | VDD         | PCI           |              |

| AA12 | GND         |               |              |

| AA13 | GND         |               |              |

| AA14 | VDD         | 5V            |              |

| AA15 | I/O         | PCI interface | PCI_AD[15]   |

| AA16 | VDD         | PCI           |              |

| AA17 | I/O         | PCI interface | PCI_AD[11]   |

| AA18 | 1/0         | PCI interface | PCI_C_BEB[0] |

| AA19 | 1/0         | PCI interface | PCI_AD[6]    |

| AA20 | GND         |               |              |

| AA21 | I/O         | A-memory      | ADQ[0]       |

| AA22 | I/O         | A-memory      | ADQ[1]       |

| AA23 | 1/0         | A-memory      | ADQ[2]       |

| AB1  | 0           | B-memory      | BCS[0]       |

| AB2  | 0           | B-memory      | BCS[1]       |

| Pin  | I/O<br>Type | Category      | Name         |

|------|-------------|---------------|--------------|

| AB3  | ı           | PCI interface | PCI_GNTB     |

| AB4  | 1/0         | PCI interface | PCI_AD[30]   |

| AB5  | 1/0         | PCI interface | PCI_AD[27]   |

| AB6  | 1/0         | PCI interface | PCI_AD[25]   |

| AB7  | 1/0         | PCI interface | PCI_C_BEB[3] |

| AB8  | 1/0         | PCI interface | PCI_AD[23]   |

| AB9  | 1/0         | PCI interface | PCI_AD[20]   |

| AB10 | 1/0         | PCI interface | PCI_AD[18]   |

| AB11 | 1/0         | PCI interface | PCI_C_BEB[2] |

| AB12 | 1/0         | PCI interface | PCI_IRDYB    |

| AB13 | I/O         | PCI interface | PCI_DEVSELB  |

| AB14 | 1/0         | PCI interface | PCI_PERRB    |

| AB15 | 1/0         | PCI interface | PCI_PAR      |

| AB16 | 1/0         | PCI interface | PCI_AD[14]   |

| AB17 | 1/0         | PCI interface | PCI_AD[12]   |

| AB18 | 1/0         | PCI interface | PCI_AD[9]    |

| AB19 | 1/0         | PCI interface | PCI_AD[7]    |

| AB20 | 1/0         | PCI interface | PCI_AD[5]    |

| AB21 | 1/0         | PCI interface | PCI_AD[2]    |

| AB22 | 1/0         | PCI interface | PCI_AD[0]    |

| AB23 | 0           | A-memory      | ACS[2]       |

| AC1  | I           | PCI interface | PCI_INTAB    |

| AC2  | 1           | PCI interface | PCI_RSTB     |

| AC3  | I           | PCI interface | PCI_REQB     |

| AC4  | 1/0         | PCI interface | PCI_AD[31]   |

| AC5  | I/O         | PCI interface | PCI_AD[28]   |

| AC6  | I/O         | PCI interface | PCI_AD[26]   |

| AC7  | I/O         | PCI interface | PCI_AD[24]   |

| AC8  | ı           | PCI interface | PCI_IDSEL    |

| AC9  | 1/0         | PCI interface | PCI_AD[22]   |

| AC10 | I/O         | PCI interface | PCI_AD[19]   |

| AC11 | 1/0         | PCI interface | PCI_AD[16]   |

| AC12 | 1/0         | PCI interface | PCI_FRAMEB   |

| AC13 | 1/0         | PCI interface | PCI_TRDYB    |

| AC14 | I/O         | PCI interface | PCI_STOPB    |

| AC15 | 1/0         | PCI interface | PCI_SERRB    |

| AC16 | 1/0         | PCI interface | PCI_C_BEB[1] |

-**--** 9010734 0000071 117 **---**

7

| Pin  | I/O<br>Type | Category      | Name       |

|------|-------------|---------------|------------|

| AC17 | 1/0         | PCI interface | PCI_AD[13] |

| AC18 | 1/0         | PCI interface | PCI_AD[10] |

| AC19 | 1/0         | PCI interface | PCI_AD[8]  |

| AC20 | I/O         | PCI interface | PCI_AD[4]  |

| Pin  | I/O<br>Type | Category      | Name      |

|------|-------------|---------------|-----------|

| AC21 | I           | PCI interface | PCI_AD[3] |

| AC22 | 1/0         | PCI interface | PCI_AD[1] |

| AC23 | 0           | A-memory      | ACS[3]    |

## Pin Definitions

| Pin Name | I/O Type | Description         |  |

|----------|----------|---------------------|--|

| *RESET   | I        | System reset signal |  |

# Video, Analog and User I/O Pins

These pins include the pins related to video signal generation (both digital and analog). It also contains the pins which are related to the internal or external clock generator. Also included are four general purpose pins for application specific I/O. The TR25202 contains the required circuitry for clock generation (PLL) and for direct analog video out (current mode DAC). However, it is possible to replace these with external components, and in order to use the internal clock generator the clock generator outputs must be connected on the board level to the corresponding outputs.

| outpaid:            |               |                                                                                                                                                                                                                                                                                                                 |

|---------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROS_CLK            | I/O (NC)      | Processor Clock. Normally not connected, can be used either as a clock input or as a clock output depending on the CLK_TST signals.                                                                                                                                                                             |

| VIDEO_CLK           | I/O (NC)      | Video Clock. Normally not connected, can be used either as a clock input or as a clock output depending on the CLK_TST signals.                                                                                                                                                                                 |

| CHIP_LOOP_FILTER    | Analog<br>I/O | Chip Loop Filter Connection. The loop filter connection for the chip clock PLL. Typical loop filter component values are C=100nF, R=400 $\Omega$ .                                                                                                                                                              |

| VIDEO_LOOP_FILTER   | Analog<br>I/O | Video Loop Filter Connection. The loop filter connection for the video clock PLL. Typical loop filter component values are C=100nF, R=400 $\Omega$                                                                                                                                                              |

| XTAL_IN, XTAL_OUT   | Analog<br>I/O | Crystal In, Crystal Out. Connections for the external crystal for the internal clock generator. Typical crystal frequency is 14.3181818 MHz.                                                                                                                                                                    |

| VREF                | I/O           | Voltage Reference (for the Video DAC). This is the output of the TR25202 internal voltage reference (1.23 V). The output has relatively high impedance (10k $\Omega$ ), so it is possible to override it with an external voltage reference. It is recommended that a bypass capacitor be attached to this pin. |

| RREF                |               | Resistor Reference. A resistor of $1.1 k\Omega$ should be connected between this pin and the ground. The formula relating the DAC msb current, VREF, and RREF is:                                                                                                                                               |

|                     |               | $\frac{I_{msb}}{8} = \frac{V_{REF}}{R_{REF}}$                                                                                                                                                                                                                                                                   |

|                     |               | where I <sub>msb</sub> is the current change corresponding to the most significant bit in the color data. Typical value for the ratio is:                                                                                                                                                                       |

|                     |               | $\frac{V_{ref}}{R_{ref}} = 1.1 mA$                                                                                                                                                                                                                                                                              |

| IRED, IGREEN, IBLUE | Analog O      | Analog (current mode) red, green, and blue video output signals.                                                                                                                                                                                                                                                |

| CLK_TST[1:0]        | 1             | CLK_TST mode. Configures the direction of the VIDEO_CLK and PROS CLK.                                                                                                                                                                                                                                           |

**.** 9010734 0000072 053 **.** -

3

# Pin Definitions (continued)

| Pin Name                                                                           | I/O Type           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PCLK                                                                               | 0                  | Pixel Clock Out; for an external DAC. This clock is a delayed (bonding PAD delay) version of the internally used video clock.                                                                                                                                                                                                                                                                                                               |  |  |  |

| USER_IO[4:0]                                                                       | I/O                | User I/O. General purpose I/O connection pins. These pins can be read and written, and their direction changed using internal registers.                                                                                                                                                                                                                                                                                                    |  |  |  |

| USE_ROM#                                                                           | 0                  | Use ROM (active low). TR25202 can use a ROM which is connected to the digital RGB lines for boot configuration and as a BIOS ROM. The USE ROM# line is used to differentiate between normal digital video usage and ROM access usage. It should be connected to the ROM chip select and output enable lines. (Both signals should be active low, also the ROM used must set the data pins to high impedance state when it is not selected). |  |  |  |

| CBLANK                                                                             | 0                  | Composite Blank. The combined blank signal created from the horizontal and vertical blank signals.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| HBLANK                                                                             | 0                  | Horizontal Blank.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| VBLANK                                                                             | 0                  | Vertical Blank.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CSYNC                                                                              | 0                  | Composite Sync. The combined sync signal created from the horizontal and vertical sync signals.                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| HSYNC                                                                              | 0                  | Horizontal Sync.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| VSYNC                                                                              | 0                  | Vertical Sync.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HSYNC_IN                                                                           | ı                  | Horizontal Sync In. TR25202 will detect the transition from non-active to active state on this line, and synchronize TR25202's internal operation to it.                                                                                                                                                                                                                                                                                    |  |  |  |

| VSYNC_IN                                                                           | 1                  | Vertical Sync In. TR25202 will detect the transition from non-active to active state on this line, and synchronize TR25202's internal operation to it.                                                                                                                                                                                                                                                                                      |  |  |  |

| B[7:0]                                                                             | 1/0                | Blue (digital). This bus is also used as the data bus (input) when performing ROM accesses. It is also possible to utilize it as an extra digital input resource if the digital RGB output is not used.                                                                                                                                                                                                                                     |  |  |  |

| R[7:0]                                                                             | 0                  | Red (digital). This bus is also used as the high order address bits when performing ROM accesses. It is also possible to utilize it as an extra digital output resource if the digital RGB output is not used.                                                                                                                                                                                                                              |  |  |  |

| G[7:0]                                                                             | 0                  | Green (digital). This bus is also used as the low order address bits when performing ROM accesses. It is also possible to utilize it as an extra digital output resource if the digital RGB output is not used.                                                                                                                                                                                                                             |  |  |  |

| Memory Pins The memory pins are illar operations. For spen of the memory interface | ecific description | d referred to as A and B memory pins respectively. These pin groups have simof the operation of the memory control pins please refer to the documentation                                                                                                                                                                                                                                                                                   |  |  |  |

| AA[11:0]                                                                           | 0                  | A-Memory Address. When used with SDRAM or SGRAM the memory address bus is also used to transfer configuration data and to perform bank select operations, so it is essential that the relevant address pins are connected to the corresponding address pins of the memories (it is not ok to swap the address pins).                                                                                                                        |  |  |  |

| ACAS#                                                                              | 0                  | A-Memory Column Address Select. Used for synchronous memory configurations. For "normal" DRAM configurations the DRAM CAS lines should be connected to ADQM# lines.                                                                                                                                                                                                                                                                         |  |  |  |

| ורו ביטטטטט פביטעטר 🖚 |  |

|-----------------------|--|

|-----------------------|--|

# Pin Definitions (continued)

| Pin Name   | I/O Type | Description                                                                                                                                                                                                                                                                                                        |  |  |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ACS#       | 0        | A-Memory Chip Select. These lines are needed for large memory configurations. The chip selects are decoded so that the first memory device should be connected to ACS#[0], the second to ACS#[1] etc.                                                                                                              |  |  |

| ADQM#[3:0] | 0        | A-Memory Data Byte Enables. These are connected to the DQM lines for synchronous memory alternatives (SDRAM or SGRAM) and to the CAS lines for "normal" DRAMs.                                                                                                                                                     |  |  |

| ADQ[31:0]  | I/O      | A-Memory Data Bus. The normal configuration for the A data bus is 32 bits wide (+ 32 bits for the B data bus), but it is possible to create a system with 16-bit (+ 16) wide interface when using SDRAM as the basic element for the memory subsystem.                                                             |  |  |

| AMEMCLK    | 0        | A-Memory Clock. The clock signal used by the synchronous memories. If a non-synchronous memory structure is used this signal is not connected to the memories.                                                                                                                                                     |  |  |

| AMEMCLKIN  | I        | A-Memory Clock In. Used for controlling the latching-in of the external data. This pin must be connected to the AMEMCLK pin. (The connection must be made even in configurations with non-synchronous memories).                                                                                                   |  |  |

| ARAS#      | 0        | A-Memory Row Address Select. Connected to the corresponding pin in both synchronous and non-synchronous memories.                                                                                                                                                                                                  |  |  |

| AWE#       | 0        | A-Memory Write Enable. Connected to the corresponding pin in both synchronous and non-synchronous memories.                                                                                                                                                                                                        |  |  |

| BA[11:0]   | 0        | B-Memory Address. When used with SDRAM or SGRAM, the memory address bus is also used to transfer configuration data and perform bank select operations, so it is essential that the relevant address pins are connected to the corresponding address pins on the memories (it is not ok to swap the address pins). |  |  |

| BCAS#      | 0        | B-Memory Column Address Select. Used for synchronous memory configurations. For normal* "DRAM configurations the DRAM CAS lines should be connected to BDQM# lines.                                                                                                                                                |  |  |

| BCS#       | 0        | B-Memory Chip Select. These lines are needed on large memory configura-<br>tions. The chip selects are decoded so that that the first memory device<br>should be connected to BCS#[0] the second to BCS#[1] etc.                                                                                                   |  |  |

| BDQM#[3:0] | 0        | B-Memory Data Byte Enables. These are connected to the DQM lines for the synchronous memory alternatives (SDRAM or SGRAM) and to the CAS lines for "normal" DRAMs.                                                                                                                                                 |  |  |

| BDQ[31:0]  | I/O      | B-Memory Data Bus. The normal configuration for the B data bus is 32 bits wide (+ 32 bits for the A data bus), but it is possible to create a system with 16-bit (+ 16) wide interface when using SDRAM as the basic element for the memory subsystem.                                                             |  |  |

| BMEMCLK    | 0        | B-Memory Clock. The clock signal used by the synchronous memories. If a non-synchronous memory structure is used this signal is not connected to the memories.                                                                                                                                                     |  |  |

| BMEMCLKIN  | I        | B-Memory Clock In. Used for controlling the latching-in of the external data. This pin must be connected to the BMEMCLK pin. (The connection must be made even in configurations with non-synchronous memories).                                                                                                   |  |  |

.**==** 9010734 0000074 926 **==** ----

# Pin Definitions (continued)

| Pin Name                                               | I/O Type                                | Description                                                                                                                                                                                                                      |  |  |  |

|--------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BRAS#                                                  | 0                                       | B-Memory Row Address Select. Connected to the corresponding pin in bot synchronous and non-synchronous memories.                                                                                                                 |  |  |  |

| BWE#                                                   | 0                                       | B-Memory Write Enable. Connected to the corresponding pin in both synchronous and non-synchronous memories.                                                                                                                      |  |  |  |

| PCI Pins For a complete referen be obtained from PCI S | ce of the PCI rel<br>Special Interest ( | ated pins please refer to PCI Local Bus Specification Revision 2.1, which can Group.                                                                                                                                             |  |  |  |

| PCI_AD[31:0]                                           | 1/0                                     | The multiplexed address and databus.                                                                                                                                                                                             |  |  |  |

| PCI_C/BE#[3:0]                                         | I/O                                     | Bus Command and Byte Enables. Used to transmit the command on the first cycle of the transaction and the byte enables on the following cycles.                                                                                   |  |  |  |

| PCI_CLK                                                | 1                                       | PCI Clock. TR25202 supports PCI clock frequencies in the range 0-33 MHz.                                                                                                                                                         |  |  |  |

| PCI_DEVSEL#                                            | I/O                                     | Device Select. Used by the transaction target to indicate that it has decoded and recognized the address of the transaction.                                                                                                     |  |  |  |

| PCI_FRAME#                                             | I/O                                     | Cycle Frame. Driven by the transaction initiator to indicate the beginning and duration of an access.                                                                                                                            |  |  |  |

| PCI_GNT#                                               | 1                                       | Grant. Indicates the grant of the bus access when operating as a bus master.                                                                                                                                                     |  |  |  |

| PCI_IDSEL                                              | l                                       | Initialization Device Select. Used as a chip select during the configuration transactions. (Configuration transactions do not use the normal PCI addres decoding).                                                               |  |  |  |

| PCI_INTA#                                              | 0                                       | Interrupt A. Interrupt request. The wiring of this interrupt line to the CPU interrupts is motherboard and operating system dependent. The interrupt is reset by resetting the corresponding status register bit.                |  |  |  |

| PCI_IRDY#                                              | 1/0                                     | Initiator Ready, used on the PCI bus to indicate that the initiator is ready to transfer data on the current clock cycle. Pin direction depends whether TR25202 is participating to the transfer as a target or as an initiator. |  |  |  |

| PCI_PAR                                                | 1/0                                     | Parity.                                                                                                                                                                                                                          |  |  |  |

| PCI_PERR#                                              | 1/0                                     | Parity error.                                                                                                                                                                                                                    |  |  |  |

| PCI_REQ#                                               | 0                                       | Request for bus. Used when operating as the initiator, for requesting the bus ownership.                                                                                                                                         |  |  |  |

| PCI_RST#                                               | 1/0                                     | Reset.                                                                                                                                                                                                                           |  |  |  |

| PCI_SERR#                                              | 1/0                                     | System error.                                                                                                                                                                                                                    |  |  |  |

| PCI_STOP#                                              | 1/0                                     | Stop transaction, used by the target when it needs to stop a transaction. Typical usage does not indicate any kind of error condition.                                                                                           |  |  |  |

| PCI_TRDY#                                              | I/O                                     | Target Ready , used on the PCI bus to indicate that the target is ready to transfer data on the current clock cycle. pin direction depends whether TR25202 is participating to the transfer as a target or as an initiator.      |  |  |  |

| 4670414 | 0000075 | 964 |

|---------|---------|-----|

|---------|---------|-----|

## **TR25202 Architecture Overview**

TR25202 offers a single chip implementation of the rendering stage of a traditional 3-stage 3D graphics pipeline comprising tessellation, geometry, and rendering. Together with the host, the architecture performs all the required operations from the object oriented scene handling to per-pixel operations. The primitives are first initialized in the geometry stage by the host, then rasterized in TR25202's primitive processor. The resulting individual pixels are sent to TR25202's pixel processor, which finally writes them to the screen through TR25202's memory management unit. The device also contains a complete PCI bus master interface for communicating with the host, and a video interface comprising a clock synthesizer and a truecolor DAC.

#### Pixel Processor

The pixel processor handles visibility checking using the Z-buffer, performs texture data fetching, and blends colors for transparency and other effects. It receives as input a list of pixels along with their properties from the primitive processor; and as output writes the resulting colors to the local frame buffer memory. The process is described with a shading program, which can be provided by the user. For high picture quality, all operations are performed with true-color accuracy. In the calculation of the final color, it is possible to use multiple textures and special effects including fog, environment mapping and bump mapping.

#### **Primitive Processor**

The primitive processor, also known as the rasterizer, generates the individual pixels which form each primitive, and forwards them to the pixel processor. Primitives can be triangles, lines or 2D regions, and are defined by their edges. The primitive processor first determines which pixels are inside the primitive and then calculates a set of eight associated pixel properties. They can be used to control the color, transparency, fog intensity, specular intensity, primary texture, and secondary texture of the pixels. All properties, including colors, are interpolated with full perspective correction, without any performance penalties. This guarantees that lighting and texture will match perfectly and any undesired warping is avoided.

#### **PCI** Interface

The Pyramid3D can be directly connected to a PCI bus without any extra logic. The PCI interface pro-

vides the host with linear access to the frame buffer and memory mapped registers. The frame buffer can be accessed in both RGB and YUV format, making real-time video over the PCI very simple. In addition, bus mastering is supported so that textures, geometry and individual triangles can be read from the main memory without host processor overhead.

## **Texturing**

In order to maximize image quality without maximizing memory usage, a wide variety of texturing methods are supported. The textures can range from 32 x 32 pixels with 4-bit indexed color, up to 1024 x 1024 pixels; they can also be of full 32-bit true-color quality. For indexed textures, the pixel processor has an internal 256-color 32-bit palette. Textures can contain transparency information. The texturing quality can be further increased with texture filtering. For all texture formats, it is possible to use MIP-mapping, bilinear and trilinear filtering.

## **Perspective Correction**

Perspective correction is performed for both textures and shading without any performance penalty. This ensures that textures and lighting on all surfaces match perfectly. Full perspective correction also eliminates incorrect surface warping, which can otherwise be visible on nearby surfaces.

## **Complex Shading**

Complex shading is performed in a single pass. Multiple simultaneous textures can be used, and are all properly filtered for the highest quality. The textures are combined with interpolated colors and settings using programmable shading operations. Complex shading effects such as textured surfaces with environment mapping can be efficiently generated.

Phong shading is efficiently simulated by using environment mapping. Multiple colored lights can be combined with reflective surfaces. The Pyramid3D architecture makes it possible to combine these highlights with textures and diffuse lighting, so that the result is correctly rendered. All this is performed in a single pass.

# **Bump Mapping**

Bump mapping adds the final touch to surfaces. They can be made to look rough and detailed without any extra geometry. This also gives more control over the appearance of surfaces and makes

9010734 0000076 719 1

computation faster, since bump mapping is more efficient compared to adding the details with geometry.

Bump mapping adds surface detail without increasing geometric complexity. This operation requires multiple simultaneous texture channels provided by TR25202. The extra detail is specified by using a displacement map, defined like normal texture maps. It specifies the shape of the surface at each point.

## Programmability

Programmability is central to the Pyramid3D architecture. The full programmability of the pixel processor makes it possible to realize many shading models and create new ones to suit the application.

#### **Unified Buffer Architecture**

Unified buffer architecture is used to store all the data, including frame buffer, textures, and geometry. This adds flexibility and makes memory usage more efficient, since no memory is ever left unused because of being assigned the wrong function. As a result, less memory is needed to support a wide range of 3D applications.

# Functional Description<sup>1</sup>

#### **Memory Interface**

The preferred memory type for TR25202 is Synchronous DRAM (SDRAM) or Synchronous Graphics RAM (SGRAM). EDO DRAM and generic Fast Page Mode DRAM can also be used but with lower performance.

There are 3 commonly used memory configurations with TR25202:

- Type 1: Full performance can be achieved by connecting TR25202 with four 1Mx16 SDRAMs (a total of 8MBytes).

- Type 2: A version with lower performance can be created by using two 1Mx16 SDRAMs (a total of 4MBytes).

Type 3: A further cost sensitive version can be created easily with two 256Kx32 SGRAMs or EDO DRAMs (a total of 2MBytes).

The performance drop between Type 1 and Type 2 is mostly significant when high resolution and/or true-color modes are used. Type 3 offers high polygon rendering rates comparable to Type 1 (SGRAM only), through a wide 64-bit memory interface, but with reduced local graphics memory depth for frame buffer, Z-buffer, and texture storage.

#### **PCI Interface**

TR25202 has a PCI bus master interface which conforms to PCI Local Bus Specification Revision 2.1. The PCI interface of TR25202 contains two base address registers. One register is used to map the internal registers and user controllable internal memories of TR25202 to the PCI bus. The other register is used for mapping the local graphics memory to the PCI bus.

## **PCI Bus Interface Feature Summary**

Conforms to PCI Local Bus Specification Revision 2.1.

- · Fast DEVSEL# assertion.

- When acting as a PCI target for write operations, it does not generate wait states.

- Memory on the graphics card is accessible using two independent apertures as suggested by PCI Multimedia Design Guide rev 1.0.

- Memory apertures can be configured to perform automatically the color space conversions needed, for example, for video streaming applications. TR25202 supports the conversions required for the pixel formats (RGB15+α, RGB24+α, and YUV 4:2:2) defined as the Full Interoperability Level in PCI Multimedia Design Guide rev 1.0.

9010734 0000077 635 📟

Representation of numbers: decimal numbers are represented with no special suffix or prefix (e.g. 256); hexadecimal numbers are represented with suffix "h" (e.g. 7Fh); binary numbers are represented with suffix "b" (e.g. 00111010b).

# **PCI Configuration Space**

TR25202 implements the PCI configuration space registers shown in Table 1.

Table 1. PCI Configuration Space Registers

|         |                                          | Reg                                    | gister    |           |          |  |

|---------|------------------------------------------|----------------------------------------|-----------|-----------|----------|--|

| Address | 25 25 25 25 25 25 25 25 25 25 25 25 25 2 | 20000000000000000000000000000000000000 |           |           |          |  |

| 0       | devi                                     | device_id vendor_id                    |           |           |          |  |

| 4       | sta                                      | atus                                   |           | comma     | nd       |  |

| 8       |                                          | class_code                             |           |           | aa       |  |

| 12      |                                          | ab                                     | ac        |           | ad       |  |

| 16      |                                          | graphics                               | s_ram_BAR | <u> </u>  |          |  |

| 20      |                                          | control_re                             | gisters_B | AR        |          |  |

| 24      |                                          | Not in use                             | (reserve  | d)        |          |  |

| 28      |                                          | Not in use                             | (reserve  | d)        |          |  |

| 32      |                                          | Not in use                             | (reserve  | d)        |          |  |

| 36      |                                          | Not in use                             | (reserve  | d)        |          |  |

| 40      |                                          | Not in use                             | (reserve  | d)        |          |  |

| 44      | subsys                                   | stem_ID                                | subs      | system_ve | endor_ID |  |

| 48      | expansio                                 | n_ROM_BAR                              |           |           | ****     |  |

| 52      |                                          | Not in use                             | (reserved | 1)        |          |  |

| 56      |                                          | Not in use                             | (reserved | d)        |          |  |

| 60      | Max_Lat                                  | Min_Gnt                                | ae        |           | af       |  |

| 64      |                                          | Core Clo                               | ck Config |           |          |  |

| 04      | a                                        | -                                      |           | coef      | N_coef   |  |

| 68      |                                          | Memory Cor                             | figuratio | n         |          |  |

|         |                                          | ah ai b c                              |           |           | •        |  |

| 72      |                                          | Video Clo                              | ck Config |           |          |  |

|         |                                          |                                        |           | coef      | N_coef   |  |

| 76      | R                                        | egister access                         |           |           |          |  |

| 80      |                                          | Register acces                         |           |           |          |  |

| 84      |                                          | Not in use                             |           |           |          |  |

| 88      |                                          | Not in use                             |           |           |          |  |

| 92      |                                          |                                        | (reserved | ·         |          |  |

| 96      |                                          | Not in use                             | (reserved | 1)        |          |  |

| 100     |                                          | Not in use                             | (reserved | 1)        |          |  |

| 104     |                                          | Not in use                             | (reserved | l)        |          |  |

| 108     |                                          | Not in use                             | (reserved | l)        |          |  |

| 112     |                                          | Not in use                             | (reserved | 1)        |          |  |

| 116     |                                          | Not in use                             | (reserved | l)        |          |  |

| 120     |                                          | Not in use                             | (reserved | 1)        |          |  |

| 124     |                                          | Not in use                             | (reserved | 1)        | 133.     |  |

| _= | 9010734 | 0000078 | 571 |  |

|----|---------|---------|-----|--|

| Abbreviation | Name            |

|--------------|-----------------|

| а            | non-overlap ·   |

| aa           | revision_id     |

| ab           | header_type     |

| ac           | latency_timer   |

| ad           | cache_line_size |

| ae           | Interrupt Pin   |

| af           | Interrupt Line  |

| ag           | R_coef          |

| ah           | refresh_rate    |

| ai           | mm_1_2_4_depth  |

| aj           | R_coef          |

| b            | mm_16_32_width  |

| С            | mm_8_16_chips   |

- (register:0)

- device id (bits:31-16)

- vendor\_id (bits:15-0)

- (register:4)

- status (bits:31-16)

- command (bits:15-0)

- (register:8)

- class\_code (bits:31-8)

- revision\_id (bits:7-0)

- (register:12)

- header\_type (bits:23-16)

- latency\_timer (bits:15-8)

- cache\_line\_size (bits:7-0)

- (register:16)

- graphics\_ram\_BAR (bits:31-0)

- (register:20)

- control\_registers\_BAR (bits:31-0)

- (register:44)

- subsystem\_ID (bits:31-16)

- subsystem\_vendor\_ID (bits:15-0)

- (register:48)

- expansion\_ROM\_BAR (bits:31-16)

- (register:60)

- Max\_Lat (bits:31-24)

- Min\_Gnt (bits:23-16)

- Interrupt Pin (bits:15-8)

- Interrupt Line (bits:7-0)

Core Clock Config (register:64)

The clock frequency can be calculated from the formula

$$F_{out} = \frac{M+2}{(N+2)\times 2^R} \times F_{Xtal}$$

Caution: Unsuitable clock frequency parameters can make the board containing the circuit non-operational, and possibly damage the components.

- non-overlap (bit:31)

- Control the internal clock buffer non-overlap time; 0 for short non-overlap time; 1 for longer non-overlap time.

- R\_coef (bits:15-14)

- M\_coef (bits:13-7)

- N\_coef (bits:6-0)

- Memory Configuration (register:68)

Caution: Incorrect memory configuration can make the board containing the circuit non operational, and may damage the devices on the board

- refresh\_rate (bits:22-20)

- mm\_1\_2\_4\_depth (bits:19-18)

- mm\_16\_32\_width (bit:17)

- mm\_8\_16\_chips (bit:16)

- Video Clock Config (register:72)

The clock frequency can be calculated from the formula

$$F_{out} = \frac{M+2}{(N+2)\times 2^{R}} \times F_{Xtal}$$

Caution: Unsuitable clock frequency parameters can make the board containing the circuit non operational, and possibly damage the components, or the video display

- R\_coef (bits:15-14)

- M\_coef (bits:13-7)

- N\_coef (bits:6-0)

- Register Access Address Register (register:76)

- Register Access Data Register (register:80)

The register access register provide an alternative method for accessing TR25202 internal registers in situations where the normal memory mapped register access is not

9010734 0000079 408 📟 -

available. Using this method is slow. For using the access registers, the target register address is written to the address register, and the value is written to the data register. The actual register write happens when the most significant byte of the data access register is written. This can be done with 8, 16, or 32-bit configuration register write.

## Accessing TR25202 Internal Registers

The following internal register ranges are available for access through the PCI interface. The registers are mapped to the PCI memory starting from the specified memory location by the control\_registers\_BAR. For example if the PCI **BIOS** has configured the TR25202 control\_registers\_BAR to the value 00010000h (65536) then the cr\_init register is mapped to address 65536 + 64 × 4.

| Range   | Function            |  |

|---------|---------------------|--|

| 0-16    | pixel processor     |  |

| 33-40   | video refresh       |  |

| 42-55   | system control      |  |

| 64-116  | primitive processor |  |

| 128-159 | ppu_code            |  |

| 256-511 | texture_palette     |  |

## **Memory Apertures**

The PCI interface maps the graphics card memory to the PCI-bus. Different translations including native mode and linear frame buffer mode are available.

In order to implement interfaces to other PCI multimedia devices TR25202 provides simultaneous apertures to the memory (as suggested by the PCI Multimedia Design Guide rev 1.0). It is possible to configure the apertures to provide different views and color space translations for the apertures.

The graphics memory is accessible through a 32 Mbyte memory window which is located as specified by the *graphics\_ram\_BAR*. The uppermost bit of the address in the memory window selects the memory aperture which is used.

If the aperture which is selected is in the *raw* mode then the address is used to access the on-board graphics memory, in order to support memory configurations larger than 16 Mbytes the value of *aperture\_start\_addr* × 2048 is first added to it.

If the aperture which is selected is in the *linear frame buffer* mode then the address is first split to x-coordinate and y-coordinate values for the frame buffer (or texture map) memory. The splitting to coordinates is based on the *aperture\_width* parameter.

The x-coordinate and y-coordinate are combined with the aperture\_start\_addr and aperture\_height parameters to form the actual address which is used.

## **PCI Master Functions**

The TR25202 can perform the following operations independently as a PCI master.

- Read sequences of triangle parameters for the rendering engine

- Upload data for textures and other images to the graphics memory

- Synchronize its operation to the operation of the rendering engine

#### **System Control Registers**

The system control registers contain registers which are used to control the PCI master functionality. Also some system debugging and state analysis registers are placed into this category.

PCI master control registers were originally placed to the PCI configuration space, but this placement offers a more portable high performance interface for accessing them.

This register set also contains the "extra io" registers which can be used to control the general purpose I/O pins of TR25202. These pins are used in a system dependent way.

# **System Control Register Definition**

| Address | Register                        |

|---------|---------------------------------|

| 42      | PCI Master Command Address      |

| 43      | PCI Master State                |

| 44      | PCI Master Internal Address     |

| 45      | PCI Master External Address     |

| 48      | status_reg                      |

| 49      | ref_reg                         |

| 50      | debug_reg                       |

| 51      | io_reg                          |

| 52      | extra_io_reg                    |

| 54      | Memory Aperture-0 Configuration |

| 55      | Memory Aperture-1 Configuration |

# System Control Register Map

|         | Register                                |  |  |  |

|---------|-----------------------------------------|--|--|--|

| Address | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |  |  |  |

| 42      | PCI Master Command Address              |  |  |  |

| 43      | PCI Master State                        |  |  |  |

|         | aa master_counter                       |  |  |  |

| 44      | PCI Master Internal Address             |  |  |  |

| 45      | PCI Master External Address             |  |  |  |

| 46      | Not in use (reserved)                   |  |  |  |

| 47      | Not in use (reserved)                   |  |  |  |

| 48      | status_reg                              |  |  |  |

|         | - video_y_coord a b c defgh             |  |  |  |

| 49      | ref_reg                                 |  |  |  |

|         | - i video_y_ref                         |  |  |  |

| 50      | debug_reg                               |  |  |  |

| 51      | io_reg                                  |  |  |  |

| 52      | extra_io_reg                            |  |  |  |

| 53      | Not in use (reserved)                   |  |  |  |

| 54      | Memory Aperture-0 Configuration         |  |  |  |

| 34      | j k - ab - ac - ad                      |  |  |  |

| 55      | Memory Aperture-1 Configuration         |  |  |  |

|         | 1 m ae - af - ag - ah                   |  |  |  |

| Abbreviation | Name                        |

|--------------|-----------------------------|

| а            | pci_master_interrupt_active |

| aa           | master_state                |

| ab           | aperture_width              |

| ac           | aperture_height             |

| ad           | aperture_start_addr         |

| ae           | aperture_data_swap          |

| af           | aperture_width              |

| ag           | aperture_height             |

| ah           | aperture_start_addr         |

| b            | pixel_visible .             |

| С            | pci_video_interrupt_active  |

| d            | video_compare               |

| е            | rasterizer_idle             |

| f            | ppu_idle                    |

| g            | rasterizer_init_ok          |

| h            | ppu_init_ok                 |

| i            | video_irq                   |

| j            | aperture_raw_linear         |

| k            | aperture_16_32_bits         |

| 1            | aperture_raw_linear         |

| m            | aperture_16_32_bits         |

## System Control Register Description

- PCI Master Command Address (register:42)

- PCI Master State (register:43)

- master\_state (bits:31-24)

When read this register provides debugging information about the current state of the PCI master unit. If written with value 00000000 halts the pci master non zero value starts the PCI master (assuming master enable bit is 1 and other)

- master\_counter (bits:23-0)

- PCI Master Internal Address (register:44)

- PCI Master External Address (register:45)

- status\_reg (register:48)

- video v coord (bits:26-16)

- pci\_master\_interrupt\_active (bit:15)

This bit is set to one when the circuit has interrupt request active, if the interrupt has originated from the pci\_master block. Interrupt can be caused either by the PCI master command control command or by the *video\_y\_ref* register. The interrupt is active until the device driver resets the interrupt. The interrupt is reset by writing value 1 into this register bit.

- pixel\_visible (bit:14)

This bit is set to one when a visible pixel has been detected by the pixel processor in the Z-read operation. The bit is reset by writing value 1 into this register bit.

- pci\_video\_interrupt\_active (bit:13)

This bit is set to one when the device has interrupt request active, if the interrupt has originated from the video\_y comparator The interrupt is active until the device driver resets the interrupt. The interrupt is reset by writing value 1 into this register bit.

- video compare (bit:4)

- rasterizer\_idle (bit:3)

- ppu\_idle (bit:2)

- rasterizer\_init\_ok (bit:1)

- ppu\_init\_ok (bit:0)

- ref\_reg (register:49)video\_irg(bit:11)

- If this bit is set to one the device will generate an interrupt request when the video\_y value reaches the video\_y\_ref value.

- video\_y\_ref (bits:10-0)

- debug reg (register:50)

- io\_reg (register:51)

- extra\_io\_reg (register:52)

- Memory Aperture-0 Configuration (register:54)

- aperture\_raw\_linear (bit:31)0: the aperture is in raw mode.

- 1: the aperture is in linear frame buffer mode.

|   | 9010734 | 2800000 | TTZ |  |

|---|---------|---------|-----|--|

| _ |         |         | –   |  |

aperture\_16\_32\_bits, aperture\_width and aperture\_height are only used when the aperture is in the linear frame buffer mode.

- aperture\_16\_32\_bits (bits:30)

- 0: 16-bit mode (or packed YUV)

- 1: 32-bit mode (RGB24+α pixel mode)

- aperture\_width (bits:26-24)

Used in splitting the X and Y coordinates from the memory address in linear mode. The value isthe number of bits in X coordinate. Values are translated as:

| value | texture/screen width (pixels) |

|-------|-------------------------------|

| 0     | 32                            |

| 1     | 64                            |

| 2     | 128                           |

| 3     | 256                           |

| 4     | 512                           |

| 5     | 1024                          |

| 6     | 2048                          |

| 7     | reserved                      |

- aperture\_height (bits:21-16)

- aperture\_start\_addr (bits:13-0)

- Memory Aperture-1 Configuration (register:55)

- aperture\_raw\_linear (bit:31)

- 0: the aperture is in raw mode

- 1: the aperture is in linear frame buffer mode aperture\_16\_32\_bits, aperture\_width and aperture\_height are only used when the aperture is in the linear frame buffer mode.

- aperture\_16\_32\_bits (bits:30)

- 0: 16-bit mode (or packed YUV)

- 1: 32-bit mode (RGB24+ $\alpha$  pixel mode)

- aperture\_data\_swap (bits:29-28)

Bits for supporting access from a big endian host to 8 or 16-bit pixels.

- aperture\_width (bits:26-24)

Used in splitting the X and Y coordinates from the memory address in linear mode.

The value is the number of bits in X coordinate, Values are translated as:

| value | texture/screen width (pixels) |

|-------|-------------------------------|

| 0     | 32                            |

| 1     | 64                            |

| 2     | 128                           |

| 3     | 256                           |

| 4     | 512                           |

| 5     | 1024                          |

| 6     | 2048                          |

| 7     | reserved                      |

|       |                               |

- aperture\_height (bits:21-16)

- aperture\_start\_addr (bits:13-0)

#### Video Interface

The current video interface unit contains the following registers:

| Address | Register            |

|---------|---------------------|

| 33      | video_width_height  |

| 34      | screen_width_height |

| 35      | video_vblank        |

| 36      | video_hblank        |

| 37      | video_vsync         |

| 38      | video_hsync         |

| 39      | video_base_conf     |

| 40      | video_bit_config    |

## Video Interface Register Map

|            |                                                    | Register           |                  |

|------------|----------------------------------------------------|--------------------|------------------|

| Address    | 24 25 28 33 25 25 25 25 25 25 25 25 25 25 25 25 25 | 123456748          | 0-08-98-88-0     |

| 33         |                                                    | video_width_height |                  |

| 33         | <u>-</u>                                           | video_height       | video_width      |

| 34         |                                                    | screen_width_heigh | t                |

| <b>3</b> 4 | _                                                  | screen_height      | screen_width     |

| 35         |                                                    | video_vblank       |                  |

| 33         |                                                    | vblank_start       | vblank_end       |

| 36         |                                                    | video_hblank       |                  |

| 30         | -                                                  | hblank_start       | hblank_end       |

| 37         | video_vsync                                        |                    |                  |

| 37         | -                                                  | vsync_start        | vsync_end        |

| 38         | video_hsync                                        |                    |                  |