**PRODUCT DEVELOPMENT PACKAGE**

### SPC8108F<sub>0B</sub> LCD VGA CONTROLLER

Release 0.0 Issue Date: May 1993

S-MOS Systems, Inc. • 2460 North First Street • San Jose, California 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238

THIS PAGE INTENTIONALLY BLANK

#### TABLE OF CONTENTS

#### SPC8108Fob Data Sheet

#### SPC8108FOB Hardware Manual

#### Introduction

| SPC8108Foв Product Brief | HWI-1-1 |

|--------------------------|---------|

|--------------------------|---------|

#### Specification

| Power Save Modes            | HWS-1-1 |

|-----------------------------|---------|

| Video Buffer Memory Options | HWS-2-1 |

| A.C. Characteristics        |         |

| LCD Panel Options           |         |

|                             |         |

#### Registers

| I/O Register Descriptions           | HWR-1-1 |

|-------------------------------------|---------|

| Proprietary Register Implementation |         |

#### SPC8108Fob Software Manual

#### Utilities

| SWU-1-1 |

|---------|

| SWU-2-1 |

| SWU-3-1 |

| SWU-4-1 |

| SWU-5-1 |

| SWU-6-1 |

| SWU-7-1 |

|         |

#### **Programmer's Reference**

| BIOS Summar    | /                | SWP-1-1 |

|----------------|------------------|---------|

| BIOS Functiona | al Specification | SWP-2-1 |

### SPC8108Fob Application Notes Evaluation

| JATION                        |         |

|-------------------------------|---------|

| Current Consumption           | ANE-1-1 |

| SDU8108Вов R2.0 User's Manual |         |

| Design                                         |         |

|------------------------------------------------|---------|

| BIOS Configuration Information                 | AND-1-1 |

| PI Bus Symmetrical Implementation Schematics   | AND-2-1 |

| PI Bus Asymmetrical Implementation Schematics  | AND-3-1 |

| ISA Bus Symmetrical Implementation Schematics  |         |

| ISA Bus Asymmetrical Implementation Schematics | AND-5-1 |

#### THIS PAGE INTENTIONALLY BLANK

# SPC8108F<sub>0B</sub> LCD VGA Controller Power Save Modes

Drawing Office No.

**Revised: 4/8/93**

Copyright © 1993 S-MOS Systems, Inc. All rights reserved.

#### **POWER SAVE MODES**

#### **1.0 POWER SAVE MODES**

To accommodate the important need for power reduction in sub-notebook and palmtop computers, one hardware-controlled and five-software controlled Power Save Modes have been incorporated into the SPC8108. Additional options for these Power Save Modes can be enabled by setting bits in various Auxiliary registers, allowing flexibility in tailoring the power reduction scheme to any particular system implementation.

#### **1.1 Software Power Save Modes**

The Power Save Mode bits in the Power Save Register, Aux[03] select one of the five software Power Save Modes as shown below. Note that if hardware Suspend mode is activated, the software power save mode setting in this register is ignored (i.e. hardware Suspend mode overrides the software power save modes). If these bits are set to a values 110 or 111, then the chip will remain in normal active mode. The following descriptions outline the major functions of each power save mode. Some differences in power save mode operation exist between LCD and CRT display modes - see the following tables and notes for more information.

| Power | Power Save Mode Select |       | Mode Activated                              |  |  |  |  |  |  |

|-------|------------------------|-------|---------------------------------------------|--|--|--|--|--|--|

| bit 2 | bit 1                  | bit 0 |                                             |  |  |  |  |  |  |

| 0     | 0                      | 0     | Normal Operation                            |  |  |  |  |  |  |

| 0     | 0                      | 1     | Power Save Mode 1 enable                    |  |  |  |  |  |  |

| 0     | 1                      | 0     | Power Save Mode 2 enable                    |  |  |  |  |  |  |

|       |                        |       | (toggle between states 1 & 2, see below)    |  |  |  |  |  |  |

| 0     | 1                      | 1     | Power Save Mode 3 enable                    |  |  |  |  |  |  |

| 1     | 0                      | 0     | Power Save Mode 4 enable                    |  |  |  |  |  |  |

| 1     | 0                      | 1     | Power Save Mode 5 enable (n/a for CRT mode) |  |  |  |  |  |  |

#### Software Power Save Mode 1

- No video display accesses to display memory.

- Sequencer is dedicated to CPU accesses to/from display memory.

- Display memory refresh is maintained and is generated from active CLKI input (28MHz for LCD, 25MHz or 28MHz for CRT). Refresh rate can be selected: 64 kHz or 8 kHz, (for 256 cycle/4 msec, or 256 cycle/32 msec DRAM, respectively).

- I/O read/write of all registers is allowed.

- /LCDPWR and IREFCNT signals forced high.

- LCD interface output signals tri-stated or forced low, depending on the state of the LCD Signal PS Mode bit in LCD Support Register 1, Aux[02] bit 1.

- if CRT display enabled, CRT and RAMDAC interface signals forced low (except /DACRD and /DACWR which remain active).

#### Software Power Save Mode 2

Power Save Mode 2 has two states. Initially when Power Save Mode 2 is set, the chip enters State 1. If no display memory read or write is detected for about two horizontal lines (approx. 63.5 us), the chip enters State 2. If a display memory read or write is requested while in State 2, the chip returns to State 1 to service the display memory access within 3 - 7 clock periods of the active CLKI input clock.

#### State 1

- No video display accesses to display memory.

- Sequencer is dedicated to CPU accesses to/from display memory.

- Display memory refresh is maintained and is generated from the active CLKI input (28MHz for LCD, 25MHz or 28MHz for CRT). Refresh rate can be selected: 64 kHz or 8 kHz, (for 256 cycle/4 msec, or 256 cycle/32 msec DRAM, respectively).

- I/O read/write of all registers is allowed.

- /LCDPWR and IREFCNT signals forced high.

- LCD interface output signals tri-stated or forced low, depending on the state of the LCD Signal PS Mode bit in LCD Support Register 1, Aux[02] bit 1.

- if CRT display enabled, CRT and RAMDAC interface signals forced low (except /DACRD and /DACWR which remain active).

#### State 2

- No video display accesses to display memory.

- No CPU accesses to/from display memory.

- Sequencer is halted.

- Display memory refresh is maintained and is generated from the active CLKI input (28MHz for LCD, 25MHz or 28MHz for CRT). Refresh rate can be selected: 64 kHz or 8 kHz, (for 256 cycle/4 msec, or 256 cycle/32 msec DRAM, respectively).

- I/O read/write of all registers is allowed.

- /LCDPWR and IREFCNT signals forced high.

- LCD interface output signals tri-stated or forced low, depending on the state of the LCD Signal PS Mode bit in LCD Support Register 1, Aux[02] bit 1.

- if CRT display enabled, CRT and RAMDAC interface signals forced low (except /DACRD and /DACWR which remain active).

#### Software Power Save Mode 3

- No video display accesses to display memory.

- No CPU accesses to/from display memory.

- Sequencer is halted.

- No display memory refresh.

- I/O read/write of all registers is allowed (except LUT and RAMDAC registers).

- /LCDPWR and IREFCNT signals forced high.

- LCD interface output signals tri-stated or forced low, depending on the state of the LCD Signal PS Mode bit in LCD Support Register 1, Aux[02] bit 1.

- if CRT display enabled, CRT and RAMDAC interface signals forced low (except /DACRD and /DACWR which are forced high).

#### Options

- I/O read/write to all registers except Auxiliary Registers can be disabled.

- the active internal clock oscillator cell can be disabled if a 2-terminal crystal is used. Note that the non-selected internal clock oscillator is automatically disabled in all active and power-save modes.

#### Software Power Save Mode 4

- No video display accesses to display memory.

- No CPU accesses to/from display memory.

- Sequencer is halted.

- Display memory refresh is maintained and is generated from one of 3 selectable sources: 1) from the active CLKI input (28MHz for LCD, 25MHz or 28MHz for CRT), 2) from the PDCLK pin (32kHz 50% duty cycle, or 64kHz with short low pulse duration), 3) or from a clock source connected to pin MEMEN.

- Refresh rate generated from CLKI can be selected: 64 kHz or 8 kHz, (for 256 cycle/4 msec, or 256 cycle/32 msec DRAM, respectively).

- Refresh rate generated from MEMEN or PDCLK can also be selected: 64 kHz or 8 kHz, (for 256 cycle/4 msec, or 256 cycle/32 msec DRAM, respectively).

- I/O read/write of all registers is allowed (except LUT and RAMDAC registers).

- /LCDPWR and IREFCNT signals forced high.

- LCD interface output signals tri-stated or forced low, depending on the state of the LCD Signal PS Mode bit in LCD Support Register 1, Aux[02] bit 1.

- if CRT display enabled, CRT and RAMDAC interface signals forced low (except /DACRD and /DACWR which are forced high).

#### Options

- I/O read/write to all registers except Auxiliary Registers can be disabled.

- Select MEMEN input pin, PDCLK input pin, or internally divided down CLKI as the clock source for display memory refresh generation.

- select self-refresh mode, for DRAMs that support self-refresh.

- the active internal clock oscillator cell can be disabled if a 2-terminal crystal is used. Note that the non-selected internal clock oscillator is automatically disabled in all active and power-save modes.

#### Software Power Save Mode 5 (LCD mode only)

- video display accesses to display memory allowed.

- CPU accesses to/from display memory allowed.

- Display memory refresh as in normal active mode.

- I/O read/write of all registers is allowed.

- /LCDPWR signal remains low (i.e. panel power enabled) and video display remains visible on LCD.

- internal LUT disabled.

• this power save mode not available when CRT display active.

#### Options

• internal clock can be slowed to 4/5 of normal rate.

#### Hardware Power Save Mode (Suspend Mode)

- No video display accesses to display memory.

- No CPU accesses to/from display memory.

- Sequencer is halted.

- Display memory refresh is maintained and is generated from one of 3 selectable sources: 1) from the active CLKI input (28MHz for LCD, 25MHz or 28MHz for CRT), 2) from the PDCLK pin (32kHz 50% duty cycle, or 64kHz with short low pulse duration), 3) or from a clock source connected to pin MEMEN.

- Refresh rate generated from CLKI can be selected: 64 kHz or 8 kHz, (for 256 cycle/4 msec, or 256 cycle/32 msec DRAM, respectively).

- Refresh rate generated from MEMEN or PDCLK can also be selected: 64 kHz or 8 kHz, (for 256 cycle/4 msec, or 256 cycle/32 msec DRAM, respectively).

- No I/O register or memory accesses allowed (including LUT and RAMDAC).

- /LCDPWR and IREFCNT signal forced high.

- LCD interface output signals tri-stated or forced low, depending on the state of the LCD Signal PS Mode bit in LCD Support Register 1, Aux[02] bit 1.

- if CRT display enabled, CRT and RAMDAC interface signals forced low (except /DACRD and /DACWR)

- All CPU interface input signals are internally masked off (i.e. ignored). All CPU interface output signals are inactive (except MEMEN).

- active internal clock oscillator will be automatically disabled unless CLKI is selected as the clock source for display memory refresh generation.

#### **Options**

- Select MEMEN input pin, PDCLK input pin, or internally divided down CLKI as the clock source for display memory refresh generation.

- select self-refresh mode, for DRAMs that support self-refresh.

#### **1.2 Power Save Mode Function Summary**

#### LCD Only (no CRT attached, RAMDAC powered off by system)

| Power Save<br>Mode (PSM)                     | Normal<br>(Active) | SPSM1 | SPSM2 s1 | SPSM2 s2 | SPSM3                 | SPSM4                 | SPSM5 | H-PSM<br>Suspend |

|----------------------------------------------|--------------------|-------|----------|----------|-----------------------|-----------------------|-------|------------------|

| Function                                     |                    |       |          |          |                       |                       |       |                  |

| LCD Display<br>Active?                       | On                 | Off   | Off      | Off      | Off                   | Off                   | On    | Off              |

| CRT Display<br>Active?                       | n/a                | n/a   | n/a      | n/a      | n/a                   | n/a                   | n/a   | n/a              |

| I/O access<br>possible?                      | Yes                | Yes   | Yes      | Yes      | Yes,<br>except<br>LUT | Yes,<br>except<br>LUT | Yes   | No               |

| Memory access possible?                      | Yes                | Yes   | Yes      | No       | No                    | No                    | Yes   | No               |

| Memory refresh maintained?                   | Yes                | Yes   | Yes      | Yes      | No                    | Yes                   | Yes   | Yes              |

| Internal LUT active?                         | Yes                | Yes   | Yes      | Yes      | No                    | No                    | Yes   | No               |

| External<br>RAMDAC<br>active?                | n/a                | n/a   | n/a      | n/a      | n/a                   | n/a                   | n/a   | n/a              |

| Sequencer<br>running?                        | Yes                | Yes   | Yes      | No       | No                    | No                    | Yes   | No               |

| Refresh<br>generated from<br>CLKI            | Yes                | Yes   | Yes      | n/a      | n/a                   | n/a                   | Yes   | n/a              |

| (Sequencer<br>running)                       |                    |       |          |          |                       |                       |       |                  |

| Refresh<br>generated from<br>CLKI            | n/a                | n/a   | n/a      | Yes      | n/a                   | option                | n/a   | option           |

| (Sequencer stopped)                          |                    |       |          |          |                       |                       |       |                  |

| Refresh<br>generated from<br>MEMEN           | No                 | No    | No       | No       | n/a                   | option<br>note 1      | No    | option<br>note 1 |

| Refresh<br>generated from<br>PDCLK           | No                 | No    | No       | No       | n/a                   | option<br>note 2      | No    | option<br>note 2 |

| Self-refresh                                 | No                 | No    | No       | No       | n/a                   | option<br>note 3      | No    | option<br>note 3 |

| 256cycle/4ms,<br>/32ms refresh<br>selectable | Yes                | Yes   | Yes      | Yes      | n/a                   | Yes<br>note 1, 2      | Yes   | Yes<br>note 1, 2 |

#### **LCD** Signals

| UD[3:0],<br>LD[3:0] | Active | L/HiZ<br>note 13 | Active | L/HiZ<br>note 13 |

|---------------------|--------|------------------|------------------|------------------|------------------|------------------|--------|------------------|

| YD, LP, XSCL,<br>WF | Active | L/HiZ<br>note 13 | Active | L/HiZ<br>note 13 |

| /LCDPWR             | L      | Н                | Н                | Н                | Н                | Н                | L      | Н                |

#### **RAMDAC Signals**

| IREFCNT                | Н   | Н   | Н   | Н   | Н   | Н   | Н   | Н   |

|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| PD[7:0], PCLK          | HiZ |

| /DACRD,<br>/DACWR      | HiZ |

| RS2, OL0,<br>OL1, OL23 | HiZ |

| D477                   | HiZ |

| /BLANK                 | HiZ |

#### **CRT** Signals

| /HSYNC,<br>/VSYNC | HiZ |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| MS[2:0]           | n/c |

#### **CPU Signals**

| LA[23:20],<br>A[19:0],<br>D[15:0], /IOR,<br>/IOW, /IOEN,<br>/BHE, ALE,<br>RESET | active | active | active | active | active | active            | active | masked            |

|---------------------------------------------------------------------------------|--------|--------|--------|--------|--------|-------------------|--------|-------------------|

| /MEMR,<br>/MEMW,<br>MEMEN                                                       | active | active | active | active | masked | masked<br>note 15 | active | masked<br>note 15 |

Clocks

| 25MHz | disabled | disabled | disabled | disabled | disabled                     | disabled                     | disabled | disabled                                 |

|-------|----------|----------|----------|----------|------------------------------|------------------------------|----------|------------------------------------------|

| 28MHz | Active   | Active   | Active   | Active   | can be<br>disabled<br>note 4 | can be<br>disabled<br>note 4 | Active   | can be<br>disabled<br>note 5, 6,<br>7, 8 |

See "Implementation Notes" following for further details.

#### **CRT Only** (LCD off)

| Power Save<br>Mode (PSM)                     | Normal<br>(Active) | SPSM1              | SPSM2 s1           | SPSM2 s2           | SPSM3                 | SPSM4                 | SPSM5<br>n/a CRT | H-PSM<br>Suspend |

|----------------------------------------------|--------------------|--------------------|--------------------|--------------------|-----------------------|-----------------------|------------------|------------------|

| Function                                     |                    |                    |                    |                    |                       |                       |                  |                  |

| LCD Display<br>Active?                       | Off                | Off                | Off                | Off                | Off                   | Off                   | n/a              | Off              |

| CRT Display<br>Active?                       | Active             | Off                | Off                | Off                | Off                   | Off                   | n/a              | Off              |

| I/O access<br>possible?                      | Yes                | Yes                | Yes                | Yes                | Yes,<br>except<br>LUT | Yes,<br>except<br>LUT | n/a              | No               |

| Memory access possible?                      | Yes                | Yes                | Yes                | No                 | No                    | No                    | n/a              | No               |

| Memory refresh maintained?                   | Yes                | Yes                | Yes                | Yes                | No                    | Yes                   | n/a              | Yes              |

| Internal LUT active?                         | WR only<br>note 16 | WR only<br>note 16 | WR only<br>note 16 | WR only<br>note 16 | disabled              | disabled              | n/a              | disabled         |

| External<br>RAMDAC<br>active?                | Active             | Active             | Active             | Active             | disabled              | disabled              | n/a              | disabled         |

| Sequencer<br>running?                        | Yes                | Yes                | Yes                | No                 | No                    | No                    | n/a              | No               |

| Refresh<br>generated from<br>CLKI            | Yes                | Yes                | Yes                | n/a                | n/a                   | n/a                   | n/a              | n/a              |

| (Sequencer running)                          |                    |                    |                    |                    |                       |                       |                  |                  |

| Refresh<br>generated from<br>CLKI            | n/a                | n/a                | n/a                | Yes                | n/a                   | option                | n/a              | option           |

| (Sequencer stopped)                          |                    |                    |                    |                    |                       |                       |                  |                  |

| Refresh<br>generated from<br>MEMEN           | No                 | No                 | No                 | No                 | n/a                   | option<br>note 1      | n/a              | option<br>note 1 |

| Refresh<br>generated from<br>PDCLK           | No                 | No                 | No                 | No                 | n/a                   | option<br>note 2      | n/a              | option<br>note 2 |

| Self-refresh                                 | No                 | No                 | No                 | No                 | n/a                   | option<br>note 3      | n/a              | option<br>note 3 |

| 256cycle/4ms,<br>/32ms refresh<br>selectable | Yes                | Yes                | Yes                | Yes                | n/a                   | Yes<br>note 1, 2      | n/a              | Yes<br>note 1, 2 |

#### **LCD** Signals

| UD[3:0],      | L/HiZ   | L/HiZ   | L/HiZ   | L/HiZ   | L/HiZ   | L/HiZ   | n/a | L/HiZ   |

|---------------|---------|---------|---------|---------|---------|---------|-----|---------|

| LD[3:0]       | note 13 |     | note 13 |

| YD, LP, XSCL, | L/HiZ   | L/HiZ   | L/HiZ   | L/HiZ   | L/HiZ   | L/HiZ   | n/a | L/HiZ   |

| WF            | note 13 |     | note 13 |

| /LCDPWR       | Н       | Н       | Н       | Н       | Н       | Н       | n/a | Н       |

#### **RAMDAC Signals**

| IREFCNT                | L      | Н       | Н       | Н       | Н       | Н       | n/a | Н       |

|------------------------|--------|---------|---------|---------|---------|---------|-----|---------|

| PD[7:0], PCLK          | Active | Active  | Active  | Active  | L       | L       | n/a | L       |

| /DACRD,<br>/DACWR      | Active | Active  | Active  | Active  | Н       | Н       | n/a | Н       |

| RS2, OL0,<br>OL1, OL23 | Active | L       | L       | L       | L       | L       | n/a | L       |

| D477                   | L      | Н       | Н       | Н       | Н       | Н       | n/a | Н       |

|                        |        | note 18 |     | note 18 |

| /BLANK                 | Active | L       | L       | L       | L       | L       | n/a | L       |

#### **CRT** Signals

| /HSYNC,<br>/VSYNC | Active    | L         | L         | L         | L         | L         | n/a | L         |

|-------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| MS[2:0]           | connected | connected | connected | connected | connected | connected | n/a | connected |

#### **CPU Signals**

| LA[23:20],<br>A[19:0],<br>D[15:0], /IOR,<br>/IOW, /IOEN,<br>/BHE, ALE,<br>RESET | active | active | active | active | active | active            | n/a | masked            |

|---------------------------------------------------------------------------------|--------|--------|--------|--------|--------|-------------------|-----|-------------------|

| /MEMR,<br>/MEMW                                                                 | active | active | active | active | masked | masked<br>note 15 | n/a | masked<br>note 15 |

#### Clocks

| 25MHz | Active<br>/disabled<br>if not<br>selected | Active<br>/disabled<br>if not<br>selected | Active<br>/disabled<br>if not<br>selected | Active<br>/disabled<br>if not<br>selected | can be<br>disabled<br>note 4 | can be<br>disabled<br>note 4 | n/a | can be<br>disabled<br>note 5, 6,<br>7, 8 |

|-------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|------------------------------|------------------------------|-----|------------------------------------------|

| 28MHz | Active<br>/disabled<br>if not<br>selected | Active<br>/disabled<br>if not<br>selected | Active<br>/disabled<br>if not<br>selected | Active<br>/disabled<br>if not<br>selected | can be<br>disabled<br>note 4 | can be<br>disabled<br>note 4 | n/a | can be<br>disabled<br>note 5, 6,<br>7, 8 |

See "Implementation Notes" following for further details.

#### **1.3 Implementation Notes**

- 1. For Software Power Save Mode 4 and the Hardware Power Save Mode (Suspend mode), the clock source from MEMEN should be running at a frequency of 64 kHz. MEMEN's active low pulse width should be as short as possible (but greater than the min. DRAM RAS pulse width requirement). The use of a 64 kHz clock source is required for meeting the 256 cycles/4 msec DRAM refresh specification. Optionally, an 8 kHz clock source may be connected to MEMEN for DRAMs supporting 256 cycles/32 msec, or the 64 kHz input can be internally divided down to 8 kHz by setting the 32/4msecRefresh Select bit (Aux[02] bit 0 = 1).

- 2. For Software Power Save Mode 4 and the Hardware Power Save Mode (Suspend mode), the clock source connected to the PDCLK input can be either a 32 kHz 50% duty cycle clock, or a 64 kHz clock with duty cycle similar to the requirement for MEMEN described above. In the case of a 32 kHz input clock, an external RC circuit is required and must be attached to pins 38, 39 with MD[13] = 1 at RESET (see pinout descriptions) in order to create an ~100ns delayed clock. This is used internally to generate a 64 kHz clock from the 32 kHz source with the appropriate duty cycle, as required by the 64 kHz refresh rate for 256cycles/4ms DRAM. If PDCLK is a 64 kHz clock with the appropriate duty cycle, then pins 38, 39 are not required and MD[13] can be set to 0 at RESET to permit usage of these pins for the sprite function on CRT display. For either type of PDCLK source input, the resulting internal 64 kHz refresh rate can be internally divided down to 8 kHz to support 256cycle/32msec DRAM by setting the 32/4msec Refresh Select bit (Aux[02] bit 0 = 1).

- 3. The self-refresh mode option available in Power Save Mode 4 and the Hardware Power Save Mode (Suspend mode) must only be enabled if the DRAM installed supports self-refresh operation.

- 4. In Software Power Save Modes 3 and 4, software may set an Auxiliary Register bit to disable the active internal clock oscillator. This can be used to further reduce system power consumption. The active clock is defined as either the 28 MHz clock (CLK2I) for LCD mode, or for CRT modes the clock selected by the Clock Select bits in Misc. Output Register 3C2H bits 3,2. In all modes, the unselected clock oscillator is automatically disabled.

- 5. In Hardware Power Save Mode (Suspend mode), the active internal clock oscillator is automatically turned off by hardware if the self-refresh option is enabled.

- 6. In Hardware Power Save Mode (Suspend), if MEMEN is selected as the refresh clock source, then the active internal clock oscillator is automatically turned off by hardware.

- 7. In Hardware Power Save Mode (Suspend), if PDCLK is selected as the refresh clock source, then the active internal clock oscillator is automatically turned off by hardware.

- 8. In Hardware Power Save Mode (Suspend), if the internal active clock is used as the refresh clock source, then the active internal clock oscillator cannot be turned off by hardware.

- 9. The output pin /LCDPWR should be used to control the LCD panel's power supply via external circuitry. When /LCDPWR is high, the external panel power supply should be turned off. When /LCDPWR is low, the power supply should be enabled.

- 10. After RESET is asserted, /LCDPWR is held high until the CRTC is programmed and running (i.e. LCD interface signals are active).

- 11. Circuitry in the chip will ensure that upon entering a power save mode, /LCDPWR will be driven high (panel power shut off) *before* the interface signals are tri-stated or forced low. Upon exiting a power save mode, /LCDPWR will be driven low (panel power turned on) *after* the interface

S-MOS Systems, Inc. • 2460 North First Street • San Jose, California 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238

signals are returned to their active driving states. This sequencing of the /LCDPWR and interface signals is done to protect the panel from being damaged from DC signals applied to the interface while it is powered up.

- 12. Similarly, if the Sequencer is stopped, (Sequencer Reset Register bit 1 or bit 0 = 0), then /LCDPWR will be driven high (panel power shut off) *before* the Sequencer is shut down and the LCD interface signals are halted. Upon restarting the Sequencer (by setting Sequencer Reset Register bit 1 and bit 0 to 1), /LCDPWR will be driven low (panel power turned on) *after* the Sequencer is has started running and the LCD interface signals are returned to their active driving states. This sequencing of the /LCDPWR and interface signals is done to protect the panel from being damaged from DC signals applied to the interface while the Sequencer is stopped and all chip output signals are inactive.

- 13. A control bit in Auxiliary Register 1 allows selecting the power save mode state of the LCD interface signals. In power save modes, the LCD interface signals can all be driven low, or can be put into a high-impedance state, as selected by this option.

- 14. The output pin IREFCNT should be used to control the current reference source for the external RAMDAC. When IREFCNT is high, the current reference should be shut off this will ensure that the DAC analog circuitry is not active. When IREFCNT is low, the current reference should be enabled. If a voltage reference is used for the RAMDAC, then IREFCNT is not required and may be left unconnected.

- 15. When the MEMEN pin is selected as the refresh clock source, this input will not be masked during Power Save Mode 4 or Suspend mode.

- 16. If Aux[0B] bit 2 = 1, then reads to the I/O address range 3C6H 3C9H will be decoded as external RAMDAC reads. If Aux[0B] bit 2 = 0, then reads to this I/O address range will access the internal LUT registers. For CRT modes, this bit should be set to 1. If CRT mode is enabled, and the chip is in Active mode, Power Save Mode 1 or Power Save Mode 2, then writes to this I/O address range will result in data being written to both the internal LUT registers and the external RAMDAC registers.

- 17. In Active mode if the CRT is enabled, the logic value on the D477 pin is determined by Aux[0B] bit 4.

- 18. In order to properly make use of SLEEP mode of the RAMDAC, software is required to program the sleep bit in the external RAMDAC control register on system initialization. When the SPC8108 forces the D477 pin high in power save modes, the RAMDAC will enter sleep mode if this bit has been programmed correctly.

#### 2.0 TARGET POWER CONSUMPTION IN POWER SAVE MODES

Conditions:  $f_{clkin} = 28MHz$ , LCD mode, no load.

| Power Save Mode (PSM) | Normal<br>(Active) | S-PSM1 | S-PSM2<br>s1/s2 | S-PSM3 | S-PSM4 | S-PSM5 | H-PSM<br>(Suspend) |

|-----------------------|--------------------|--------|-----------------|--------|--------|--------|--------------------|

| I <sub>op</sub> (mA)  | tbd                | tbd    | tbd             | tbd    | tbd    | tbd    | tbd                |

| no load               |                    |        |                 |        |        |        |                    |

# **SPC8108F**<sub>0B</sub> LCD VGA Controller A.C. Characteristics

Drawing Office No.

**Revised: 4/8/93**

Copyright © 1993 S-MOS Systems, Inc. All rights reserved.

#### A.C. CHARACTERISTICS

$\begin{array}{ll} \hline Conditions: & V_{cc} = 5.0V \pm 10\% & T_a = 0^{\circ}C \text{ to } 70^{\circ}C \\ & T_r, \, T_f \text{ for all inputs must be} \leq 5 \text{ nsec } (10\% \sim 90\%) \\ & C_L = 100 \text{ pF (CPU, RAMDAC Interface, LCD Panel Interface)} \\ & C_L = 20 \text{ pF (Video Memory Interface)} \end{array}$

CLK Signal Dependant Input Timing:

$$T_{S} = \left[\frac{1}{f_{CLK}}\right], \quad T_{S \text{ Min}} = \left[\frac{1}{f_{CLK \text{ Max}}}\right] = \left[\frac{1}{28 \text{ MHz}}\right] = 36 \text{ ns}$$

Propagation Delay Time:

The following are tables of timing parameters and min/max values. These tables are followed by waveforms defining these parameters.

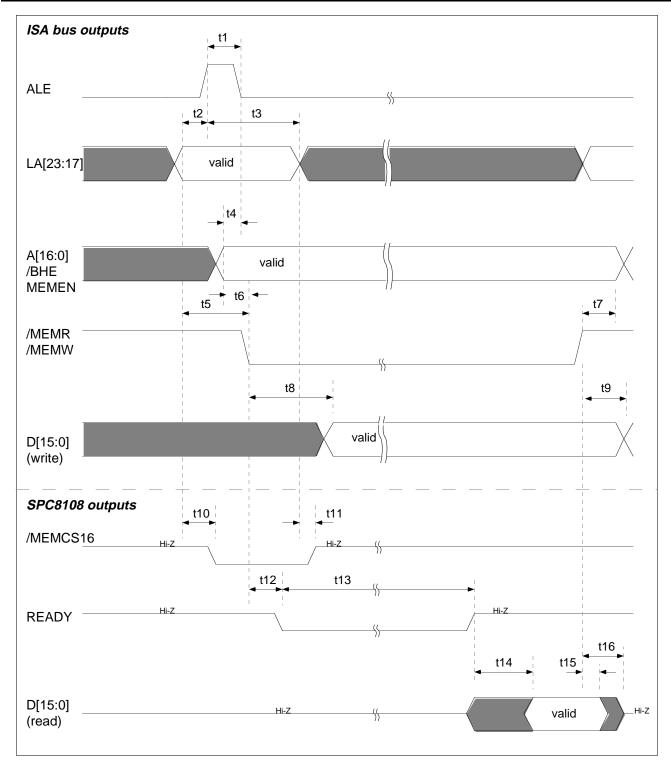

#### 1. CPU BUS CYCLE TIMING - 16 BIT MEMORY

| Symbol | Parameter                                            | Min | Тур | Max    | Units |

|--------|------------------------------------------------------|-----|-----|--------|-------|

| t1     | ALE pulse width                                      | 30  |     |        | ns    |

| t2     | LA[23:17] valid setup to ALE asserted                | 20  |     |        | ns    |

| t3     | LA[23:17] valid hold from ALE asserted               | 40  |     |        | ns    |

| t4     | A[16:0], /BHE setup to ALE negated                   | 10  |     |        | ns    |

| t5     | LA[23:17] valid setup to memory command asserted     | 10  |     |        | ns    |

| t6     | A[16:0], /BHE valid setup to memory command asserted | 10  |     |        | ns    |

| t7     | A[16:0], /BHE hold from memory command negated       | 10  |     |        | ns    |

| t8     | valid write data delay from /MEMW asserted           |     |     | 3Ts-10 | ns    |

| t9     | valid write data hold from /MEMW negated             | 10  |     |        | ns    |

| t10    | /MEMCS16 asserted from valid LA[23:17]               |     |     | 30     | ns    |

| t11    | /MEMCS16 hold from LA[23:17] invalid                 | 0   |     |        | ns    |

| t12    | READY negated from memory command asserted           |     |     | 50     | ns    |

| t13    | READY negated pulse width                            | 8Ts |     | 102Ts  | ns    |

| t14    | valid read data from READY released                  |     |     | 40     | ns    |

| t15    | read data hold from memory command negated           | 0   |     |        | ns    |

| t16    | read command negated to D[15:0] high-impedance       |     |     | 30     | ns    |

This table refers to standard ISA CPU bus timing . When configuration input MD[5] = 1 on the falling edge of RESET, refer to section 7.3 for modified address timing.

Parameter t13 max only occurs when a refresh cycle is pending during dual panel, fast dot, text modes. Max for single panel is 70Ts. Typical values are much shorter.

S-MOS Systems, Inc. • 2460 North First Street • San Jose, California 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238

Figure 3. CPU Bus Cycle Timing - 16 Bit Memory

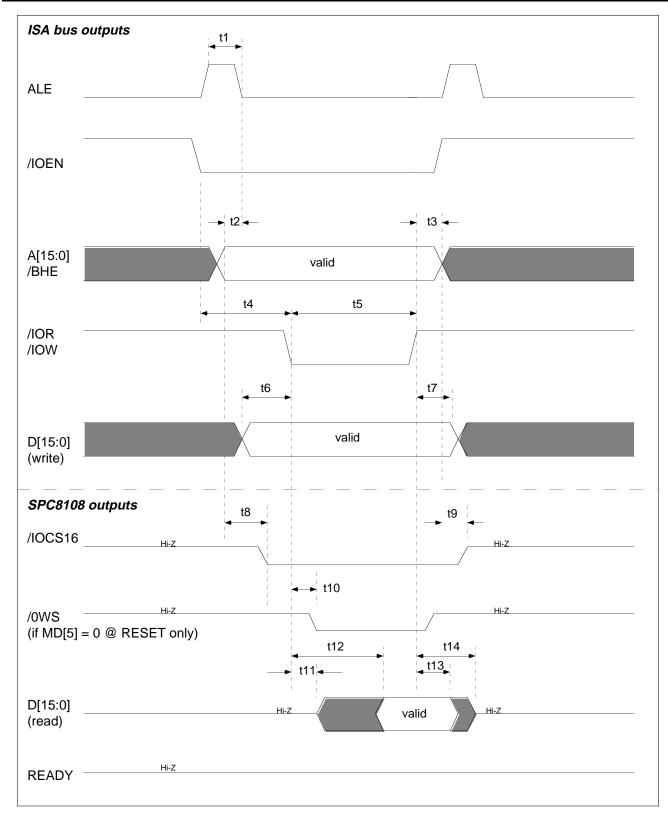

#### 2. CPU BUS CYCLE TIMING - 16 BIT I/O

| Symbol | Parameter                                                         | Min | Тур | Max | Units |

|--------|-------------------------------------------------------------------|-----|-----|-----|-------|

| t1     | ALE pulse width                                                   | 30  |     |     | ns    |

| t2     | A[15:0], /BHE valid setup to I/O command negated                  | 25  |     |     | ns    |

| t3     | A[15:0], /BHE valid hold from ALE negated                         | 10  |     |     | ns    |

| t4     | /IOEN setup to I/O command asserted                               | 10  |     |     | ns    |

| t5     | /IOW command pulse width                                          | 120 |     |     | ns    |

| t5     | /IOR command pulse width                                          | 180 |     |     | ns    |

| t6     | valid write data setup to I/O command asserted                    | 10  |     |     | ns    |

| t7     | valid write data hold from I/O command negated                    | 10  |     |     | ns    |

| t8     | /IOCS16 asserted from A[15:0], /BHE valid                         |     |     | 30  | ns    |

| t9     | /IOCS16 hold from A[15:0], /BHE invalid                           | 0   |     |     | ns    |

| t10    | /0WS asserted from I/O command asserted<br>(MD[5]=0 @ RESET only) |     |     | 30  | ns    |

| t11    | read data driven delay from read command asserted                 | 10  |     |     | ns    |

| t12    | valid read data from I/O read command asserted                    |     |     | 150 | ns    |

| t13    | read data hold from I/O command negated                           | 5   |     |     | ns    |

| t14    | read command negated to D[15:0] high-impedance                    |     |     | 30  | ns    |

This table refers to standard ISA CPU bus timing. When configuration input MD[5] = 1 on the falling edge of RESET, refer to section 4 for modified address timing.

Figure 4. CPU Bus Cycle Timing - 16 Bit I/O

S-MOS Systems, Inc. • 2460 North First Street • San Jose, California 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238

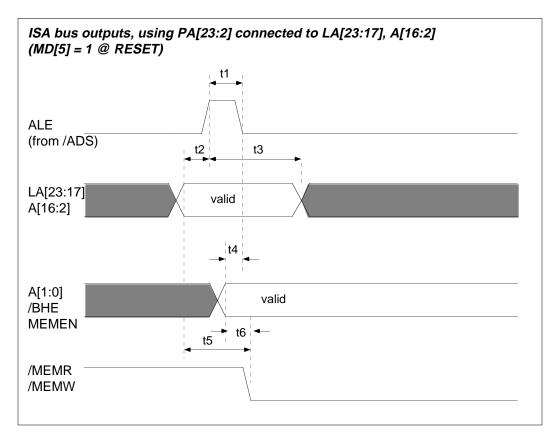

#### 3. CPU BUS CYCLE TIMING-16 BIT MEMORY, MODIFIED ADDRESS TIMING

| Symbol | Parameter                                                 | Min | Тур | Max | Units |

|--------|-----------------------------------------------------------|-----|-----|-----|-------|

| t1     | ALE pulse width                                           | 30  |     |     | ns    |

| t2     | LA[23:17], A[16:2] valid setup to ALE asserted            | 0   |     |     | ns    |

| t3     | LA[23:17], A[16:2] valid hold from ALE asserted           | 40  |     |     | ns    |

| t4     | A[1:0], /BHE valid setup to ALE negated                   | 10  |     |     | ns    |

| t5     | LA[23:17], A[16:2] valid setup to memory command asserted | 10  |     |     | ns    |

| t6     | A[1:0], /BHE valid setup to memory command asserted       | 10  |     |     | ns    |

This table refers to CPU bus timing when configuration input MD[5] = 1 on the falling edge of RESET. In this case, processor address lines PA[23:2] may be connected to address inputs LA[23:17] and A[16:2]. These inputs will be latched by the SPC8108 on the falling edge of ALE. Address inputs A[1:0] should be connected to the ISA bus address outputs A[1:0].

Figure 5. CPU Bus Cycle Timing - 16 Bit Memory, Modified Address Timing

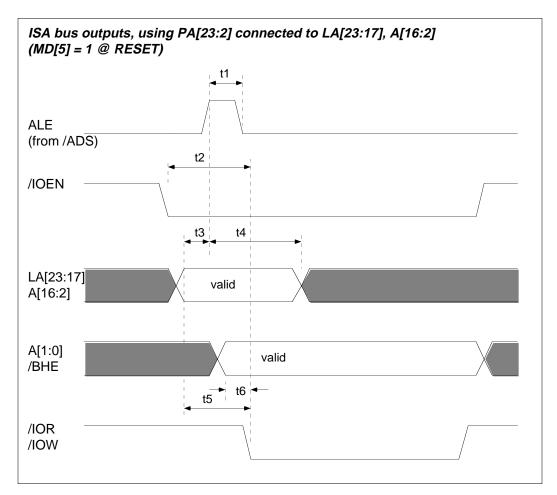

#### 4. CPU BUS CYCLE TIMING - 16 BIT I/O, MODIFIED ADDRESS TIMING

| Symbol | Parameter                                              | Min | Тур | Max | Units |

|--------|--------------------------------------------------------|-----|-----|-----|-------|

| t1     | ALE pulse width                                        | 30  |     |     | ns    |

| t2     | /IOEN active setup I/O command asserted                | 10  |     |     | ns    |

| t3     | LA[23:17], A[16:2] valid setup to ALE asserted         | 0   |     |     | ns    |

| t4     | LA[23:17], A[16:2] valid hold from ALE asserted        | 40  |     |     | ns    |

| t5     | LA[23:17], A[16:2] valid setup to I/O command asserted | 10  |     |     | ns    |

| t6     | A[1:0], /BHE valid setup to I/O command asserted       | 10  |     |     | ns    |

This table refers to CPU bus timing when configuration input MD[5] = 1 on the falling edge of RESET. In this case, processor address lines PA[23:2] may be connected to address inputs LA[23:17] and A[16:2]. These inputs will be latched by the SPC8108 on the falling edge of ALE. Address inputs A[1:0] should be connected to the ISA bus address outputs A[1:0].

Figure 6. CPU Bus Cycle Timing - 16 Bit I/O - Modified Address Timing

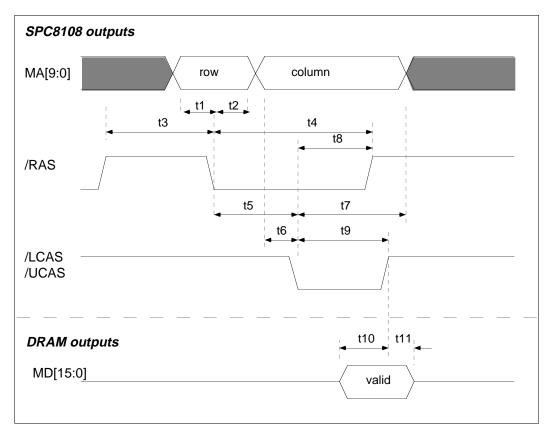

#### 5. DRAM READ CYCLE TIMING - NON-PAGE MODE

| Symbol | Parameter                                              | Min | Тур | Max | Units |

|--------|--------------------------------------------------------|-----|-----|-----|-------|

| t1     | MA[9:0] row address setup to /RAS asserted             |     |     |     | ns    |

| t2     | MA[9:0] row address hold from /RAS asserted            |     |     |     | ns    |

| t3     | /RAS precharge                                         |     |     |     | ns    |

| t4     | /RAS pulse width                                       |     |     |     | ns    |

| t5     | /RAS asserted to /LCAS, /UCAS asserted                 |     |     |     | ns    |

| t6     | MA[9:0] column address setup to /LCAS, /UCAS asserted  |     |     |     | ns    |

| t7     | MA[9:0] column address hold from /LCAS, /UCAS asserted |     |     |     | ns    |

| t8     | /LCAS, /UCAS asserted to /RAS negated                  |     |     |     | ns    |

| t9     | /LCAS, /UCAS pulse width                               |     |     |     | ns    |

| t10    | MD[15:0] read data setup to /LCAS, /UCAS negated       |     |     |     | ns    |

| t11    | MD[15:0] read data hold from /LCAS, /UCAS negated      |     |     |     | ns    |

Figure 7. DRAM Read Cycle Timing - Non-Page Mode

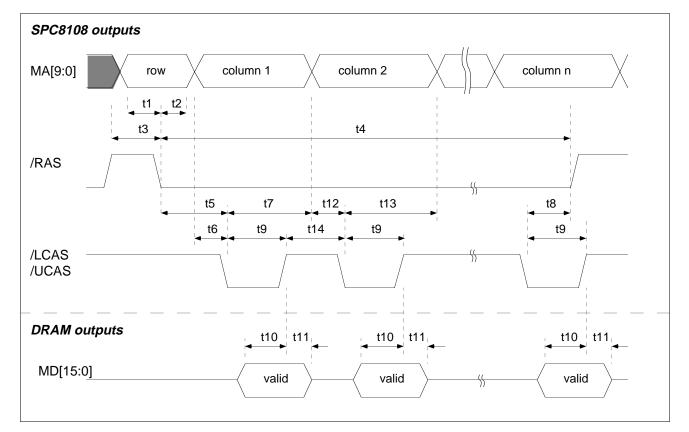

#### 6. DRAM READ CYCLE TIMING - PAGE MODE

| Symbol | Parameter                                                                                              | Min | Тур | Max | Units |

|--------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| t1     | MA[9:0] row address setup to /RAS asserted                                                             |     |     |     | ns    |

| t2     | MA[9:0] row address hold from /RAS asserted                                                            |     |     |     | ns    |

| t3     | /RAS precharge                                                                                         |     |     |     | ns    |

| t4     | /RAS pulse width                                                                                       |     |     |     | ns    |

| t5     | /RAS asserted to /LCAS, /UCAS asserted                                                                 |     |     |     | ns    |

| t6     | MA[9:0] col addr setup to /LCAS, /UCAS asserted (1st)                                                  |     |     |     | ns    |

| t7     | MA[9:0] col addr hold from /LCAS, /UCAS asserted(1st)                                                  |     |     |     | ns    |

| t8     | /LCAS, /UCAS asserted to /RAS negated                                                                  |     |     |     | ns    |

| t9     | /LCAS, /UCAS pulse width                                                                               |     |     |     | ns    |

| t10    | MD[15:0] read data setup to /LCAS, /UCAS negated                                                       |     |     |     | ns    |

| t11    | MD[15:0] read data hold from /LCAS, /UCAS negated                                                      |     |     |     | ns    |

| t12    | MA[9:0] column address setup to /LCAS, /UCAS asserted (2 <sup>nd</sup> - n <sup>th</sup> page access)  |     |     |     | ns    |

| t13    | MA[9:0] column address hold from /LCAS, /UCAS asserted (2 <sup>nd</sup> - n <sup>th</sup> page access) |     |     |     | ns    |

| t14    | /LCAS, /UCAS precharge                                                                                 |     |     |     | ns    |

#### Figure 8. DRAM Read Cycle Timing - Page Mode

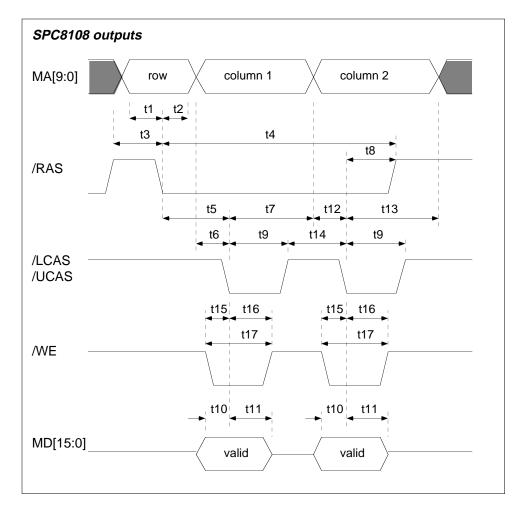

#### 7. DRAM WRITE CYCLE TIMING

| Symbol | Parameter                                                          | Min | Тур | Max | Units |

|--------|--------------------------------------------------------------------|-----|-----|-----|-------|

| t1     | MA[9:0] row address setup to /RAS asserted                         |     |     |     | ns    |

| t2     | MA[9:0] row address hold from /RAS asserted                        |     |     |     | ns    |

| t3     | /RAS precharge                                                     |     |     |     | ns    |

| t4     | /RAS pulse width                                                   |     |     |     | ns    |

| t5     | /RAS asserted to /LCAS, /UCAS asserted                             |     |     |     | ns    |

| t6     | MA[9:0] col addr setup to /LCAS, /UCAS asserted (1st)              |     |     |     | ns    |

| t7     | MA[9:0] col addr hold from /LCAS, /UCAS asserted(1st)              |     |     |     | ns    |

| t8     | /LCAS, /UCAS asserted to /RAS negated                              |     |     |     | ns    |

| t9     | /LCAS, /UCAS pulse width                                           |     |     |     | ns    |

| t10    | MD[15:0] write data setup to /LCAS, /UCAS asserted                 |     |     |     | ns    |

| t11    | MD[15:0] write data hold from /LCAS, /UCAS asserted                |     |     |     | ns    |

| t12    | MA[9:0] col addr setup to /LCAS, /UCAS asserted (2 <sup>nd</sup> ) |     |     |     | ns    |

| t13    | MA[9:0] col addr hld from /LCAS, /UCAS asserted (2nd)              |     |     |     | ns    |

| t14    | /LCAS, /UCAS precharge                                             |     |     |     | ns    |

| t15    | /WE setup to /LCAS, /UCAS asserted                                 |     |     |     | ns    |

| t16    | /WE hold from /LCAS, /UCAS asserted                                |     |     |     | ns    |

| t17    | /WE pulse width                                                    |     |     |     | ns    |

Figure 9. DRAM Write Cycle Timing

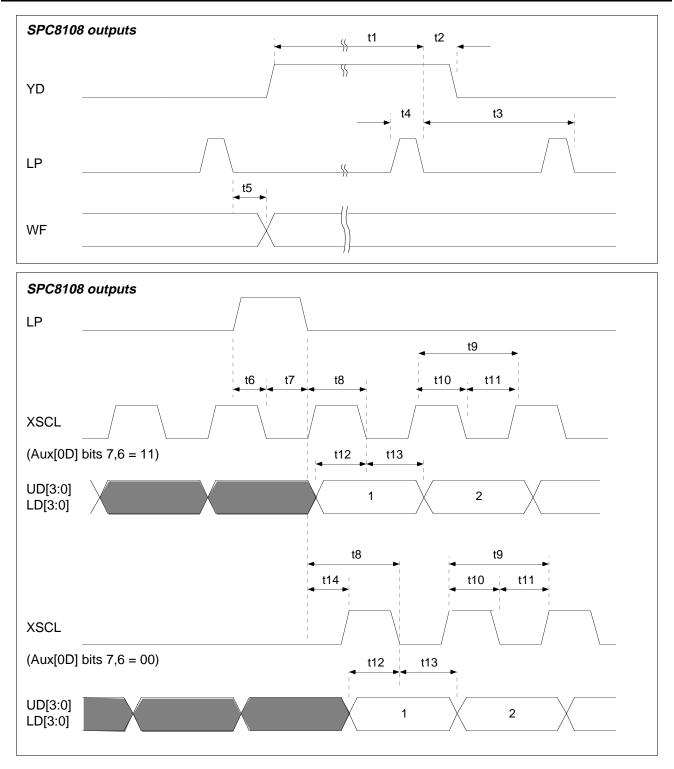

#### **13. LCD INTERFACE TIMING**

| Symbol | Parameter                                               | Min            | Тур      | Max | Units |

|--------|---------------------------------------------------------|----------------|----------|-----|-------|

| t1     | YD setup to LP negated (single panel mode)              | 739Ts-24       |          |     | ns    |

| t1     | YD setup to LP negated (dual panel mode)                | 1478Ts -<br>24 |          |     | ns    |

| t2     | YD hold from LP negated (single panel mode)             | 13Ts-24        |          |     | ns    |

| t2     | YD hold from LP negated (dual panel mode)               | 26Ts-24        |          |     | ns    |

| t3     | LP period                                               |                | 752Ts-24 |     | ns    |

| t4     | LP pulse width (Aux[0D] bit 6 =0)                       | 5Ts-24         | -        |     | ns    |

| t4     | LP pulse width (Aux[0D] bit 6 =1)                       | 6Ts-24         |          |     | ns    |

| t5     | WF delay from LP negated                                | 0              |          | 1   | ns    |

| t6     | LP setup to XSCL falling edge (Aux[0D] bit 7 =0)        | n/a            | n/a      | n/a | ns    |

| t6     | LP setup to XSCL falling edge (Aux[0D] bit 7 =1)        | 2Ts-24         |          |     | ns    |

| t7     | LP hold from XSCL falling edge (Aux[0D] bit 7 =0)       | n/a            | n/a      | n/a | ns    |

| t7     | LP hold from XSCL falling edge (Aux[0D] bit 7 =1)       | 4Ts-24         |          |     | ns    |

| t7*    | XSCL falling edge to LP falling edge                    | 103Ts-24       |          |     | ns    |

|        | (Aux[0D] bit 7 = 0 only)                                |                |          |     |       |

| t8     | LP negated to XSCL falling edge (Aux[0D] bits 7,6 = 00) | 9Ts-24         |          |     | ns    |

| t8     | LP negated to XSCL falling edge (Aux[0D] bits 7,6 =11)  | 4Ts-24         |          |     | ns    |

| t9     | XSCL period                                             | 8Ts-24         |          |     | ns    |

| t10    | XSCL low pulse width                                    | 4Ts-24         |          |     | ns    |

| t11    | XSCL high pulse width                                   | 4Ts-24         |          |     | ns    |

| t12    | UD[3:0], LD[3:0] setup to XSCL falling edge             | 4Ts-24         |          |     | ns    |

| t13    | UD[3:0], LD[3:0] hold from XSCL falling edge            | 4Ts-24         |          |     | ns    |

| t14    | LP negated to XSCL rising edge (Aux[0D] bits 7,6 = 00)  | 5Ts-24         |          |     | ns    |

| t14    | LP negated to XSCL rising edge (Aux[0D] bits 7,6 = 11)  | 0              |          |     | ns    |

Figure 15. LCD Interface Timing

# SPC8108F<sub>0B</sub> LCD VGA Controller I/O Register Summary

Drawing Office No.

**Revised: 4/8/93**

Copyright © 1993 S-MOS Systems, Inc. All rights reserved.

### 3.0 I/O REGISTER SUMMARY

This section summarizes the I/O registers of SPC8108 - only those register bits supported by the chip are shown. Note that the functionality of a subset of the IBM VGA standard registers is supported, with an additional set of Auxiliary Registers containing SPC8108 specific functions. Only details of the register functions which are not part of the VGA standard definition are given below.

- Note: Unless otherwise noted, all read/write register bits are cleared to 0 after a RESET.

- All register bits marked as "n/a" are undefined. There is no effect if they are written to, and reading these bits will return an undefined value.

#### 3.1 AUXILIARY REGISTERS

| Auxiliary Index/Data Register |        |     |     |                    |                    |                    |                    |  |  |

|-------------------------------|--------|-----|-----|--------------------|--------------------|--------------------|--------------------|--|--|

| 3DE RW                        | 3DF RW |     |     |                    |                    |                    |                    |  |  |

| n/a                           | n/a    | n/a | n/a | Auxiliary<br>Index | Auxiliary<br>Index | Auxiliary<br>Index | Auxiliary<br>Index |  |  |

|                               |        |     |     | Bit 3              | Bit 2              | Bit 1              | Bit 0              |  |  |

| 00 Extended Function Register 0 RW |                                    |                   |                      |                      |                                |  |  |  |  |

|------------------------------------|------------------------------------|-------------------|----------------------|----------------------|--------------------------------|--|--|--|--|

|                                    | Test Mode<br>Enable<br>(must be 0) | n/a<br>(reserved) | IRQ Output<br>Enable | Multi-Font<br>Enable | LCD B Reg<br>Program<br>Enable |  |  |  |  |

#### Test Mode Enable

The Test Mode Enable bit must be set to 0 for normal operation. When set to 1, the chip is placed into device test mode and the test input and test output selector bits in Auxiliary Register 04H are enabled.

#### IRQ Output Enable

When the IRQ Output Enable bit is set to 0, the IRQ output is held in a high impedance state. When this bit is set to 1, the IRQ output pin is enabled and will be driven to indicate the Vertical Retrace interrupt status.

#### **Multi-Font Enable**

When the Multi-Font Enable bit is set to 0, normal text mode font selection is enabled. When this bit is 1, it allows bits 0 to 2 of the attribute byte (foreground color) to select one of eight simultaneously displayable fonts. In this case the attribute byte foreground color bits (normally bits 0 to 2) are forced to 1, the font selection bit (bit 3) is not used, and the blink/intensity bit (bit 7) functions normally.

#### LCD B Registers Program Enable

This bit is used to access the hidden LCD Panel Size and Vertical Panel Size registers (LCD B Registers), which reside in the same address space as their CRT mode conterparts. These hidden timing registers only have an effect when the LCD is the active display. When this bit is set to 0, accesses to CRTC Register

[01] affect the normal Horizontal Total Register, and accesses to CRTC Register [12] affect the normal Vertical Display Enable End Register. When this bit is set to 1, then the "B set" registers are enabled, and accesses to CRTC Register [01] affect the Horizontal Panel Size Register, and accesses to CRTC Register [12] affect the Vertical Panel Size Register. These "B Set" registers are used only for LCD only mode (Aux[0B] bits 1,0 = 01).

| 01 LCD Sup        | port Register 0      | RW                |                                    |                   |                               |                              |                       |

|-------------------|----------------------|-------------------|------------------------------------|-------------------|-------------------------------|------------------------------|-----------------------|

| n/a<br>(reserved) | Slow Blink<br>Select | n/a<br>(reserved) | Grn-only /<br>NTSC GS<br>Weighting | n/a<br>(reserved) | Reverse/<br>Normal<br>Display | Auto-<br>Centering<br>Enable | Single/ Dual<br>Panel |

# Slow Blink Select

This bit is used to select the blink rate of the cursor and text in text modes and graphics pixels in graphics modes, if blink is enabled. If this bit is set to 0, the cursor, text or graphics pixels blink at their normal rates. If this bit is set to 1, then everything blinks at half their respective normal rates. This option may be used to make the blinking cursor more visible on some LCD panels. Note that in both normal and slow settings, the text mode cursor always blinks at twice the frequency of any blinking characters (i.e. cursor blink frequency = 2 x blink frequency of text).

# **Green-only / NTSC GS Weighting Select**

This bit is used to select one of two possible gray scale weighting functions to be applied to RGB data as it is written to the internal 256x6 LCD gray scale lookup table. When this bit is set to 0, RGB data values are mapped to gray values using NTSC weighting. When this bit is set to 1, the green component of the RGB data is used as the gray value. See section on LCD gray scale lookup table for details.

# **Reverse/Normal Display**

When the Reverse/Normal Display bit is 0, then normal display attributes are enabled. When this bit is 1, then inverse video is displayed on the LCD display. This bit also affects the overscan color as set in bit 5 of this register. This bit has no effect on the image displayed on the CRT display.

# **Auto-Centering Enable**

This bit is used to control the auto-centering function which allows display modes with less than 480 lines to be vertically centered on the LCD panel, provided that vertical expansion is not enabled (see Auxiliary Register 07). If vertical expansion is not enabled and the Auto-Centering Enable bit is 0, then all modes will be displayed with the first line at the top of the panel. If this bit is set to 1 and vertical expansion is not enabled, then for all modes hardware will adjust the vertical position of the first line of the display so that the image is centered vertically on the panel. If vertical expansion is active (i.e. all conditions for a vertical expansion mode are met; see appropriate bit description in Auxiliary Register 7), then the setting of this bit is ignored and auto-centering is disabled. If CRT mode is enabled (Aux[0B] bit 1 = 1) then auto-centering is disabled and this bit has no effect.

# Single/Dual Panel

The Single/Dual Panel bit is used to configure the chip timing for the correct LCD panel type. When this bit is 0, then dual panel mode is enabled. When this bit is 1, then single panel mode is enabled.

| 02 LCD Supp          | ort Register 1 I | RW  |                               |                                   |                                   |                                |                                |

|----------------------|------------------|-----|-------------------------------|-----------------------------------|-----------------------------------|--------------------------------|--------------------------------|

| CRT Sprite<br>Enable | n/a              | n/a | 4/8 Bit<br>Panel<br>Interface | PSM4/S<br>Refresh Clk<br>Select 1 | PSM4/S<br>Refresh Clk<br>Select 0 | LCD Signal<br>PS Mode<br>State | 32/4 msec<br>Refresh<br>Select |

# **CRT Sprite Enable**

The CRT Sprite Enable bit is used to enable or disable the sprite display on the CRT monitor. When this bit is set to 0, the sprite will not be displayed on the CRT monitor. When this bit is set to 1, the sprite circuitry for the CRT display is enabled and it will be possible to display the sprite on the CRT monitor, provided that the value on MD[13] = 0 at RESET to allow use of the OL1 and OL0 output pins.

#### 4/8 Bit Panel Interface

The 4/8 Bit Panel Interface bit configures the LCD output data for either 4 bit or 8 bit single panels. When this bit is set to 0, then in LCD mode, an 8 bit single panel interface is provided with 8 bit pixel data output on UD[3:0] (msbits) and on LD[3:0] (lsbits). When this bit is set to 1, then in LCD mode a 4 bit single panel interface is provided, where 4 bit pixel data is output only on UD[3:0], and the LD[3:0] outputs are held low. Note that this bit must be set to 0 for all dual panel modes.

#### PSM4/S Refresh Clock Select 1-0

These bits are used to select the refresh clock source during Power Save Mode 4 or Suspend mode, according to the following table:

| PSM4/S Refresh Clock Select<br>1 | PSM4/S Refresh Clock Select<br>0 | Refresh Clock Source<br>in Power Save Mode 4 and Suspend |  |  |

|----------------------------------|----------------------------------|----------------------------------------------------------|--|--|

| 0                                | 0                                | CLK1I, CLK2I                                             |  |  |

| 0                                | 1                                | MEMEN                                                    |  |  |

| 1                                | 0                                | Self Refresh                                             |  |  |

| 1                                | 1                                | PDCLK                                                    |  |  |

# CLK1I, CLK2I

When this option is selected, then the active pixel input clock (CLK1I or CLK2I) is used to generate all Power Save mode refresh timing. The active pixel clock is determined by the Clock Select bits in Misc Output Register (3C2), and by the LCD Enable and CRT Enable bits in Auxiliary Register [0B].

#### <u>MEMEN</u>

When this option is selected, then the MEMEN input pin is used as the clock source in Power Save Mode 4 and Suspend.

# Self Refresh

This option may only be used when the DRAMs installed are capable of self-refresh. When this option is selected, during Power Save Mode 4 and Suspend mode, the DRAM control lines are driven in such a manner to cause the DRAM to enter self-refresh mode. When not in self refresh mode, then CAS-before-RAS refresh cycles are used during Power Save Mode 4 or Suspend mode. Note that regardless of the setting of these bits, CAS-before-RAS refresh cycles are used during active mode and Power Save Modes 1, 2 and 5.

# <u>PDCLK</u>

When this option is selected, the PDCLK input pin is used as the clock source in Power Save Mode 4 and Suspend. For lowest possible DRAM power consumption, this input clock should have as short as possible low duration (but > min RAS pulse width). For normal refresh rate DRAM (256cycle/4ms), this input should be a 64kHz clock source. It is possible to use a 32 kHz 50% duty cycle clock for PDCLK - see pinout section for details.

# LCD Signal PS Mode State

The LCD Signal PS Mode State bit controls the states of the LCD interface signals (UD[3:0], LD[3:0], XSCL, LP, YD, WF) when the chip goes into a power save mode. When this bit is 0, the LCD signals are put into a high-impedance state when a power save mode is entered. When this bit is set to 1, then when the chip is in a power save mode, the LCD interface signals will be forced low. On RESET, this bit is set to 1.

# 32/4 msec Refresh Select

The 32/4msc Refresh Select bit is used to select 256 cycle/4 msec or 256 cycle/32msec DRAM refresh timing in all modes of operation. When this bit is 0, then 4 msec refresh timing is generated. When this bit is 1, then 32msec refresh timing is generated. In active mode and Power Save Modes 1, 2 and 5, this 4 or 32 msec refresh timing is generated from the selected CLKI source (28MHz for LCD modes, 25MHz or 28MHz for CRT modes as selected by Clock Select bits in Misc Output Register 3C2H). For Power Save Mode 4 and Suspend, this 4 or 32 msec refresh timing is generated from the active CLKI, from MEMEN input, or the PDCLK input, as selected by Aux[02] bits 3,2.

| 03 Power Sa | 03 Power Save Register RW |                    |                       |  |  |                                    |  |  |  |  |  |

|-------------|---------------------------|--------------------|-----------------------|--|--|------------------------------------|--|--|--|--|--|

| n/a         | n/a                       | Clock Slow<br>Down | Oscillator<br>Disable |  |  | Power Save<br>Mode Select<br>Bit 1 |  |  |  |  |  |

# **Clock Slow Down**

The Clock Slow Down bit is used to provide additional power savings in some LCD modes. When this bit is set to 1, then the active internal clock rate is reduced by 20%. When this bit is set to 0, then the internal clock rate equals the input clock rate. This bit is intended for use in Power Save Mode 5. If CRT mode is enabled (Aux[0B] bit 1 = 1), then this bit is ignored and has no effect.

# **Oscillator Disable**

The Oscillator Disable bit is used to control the operation of the internal clock oscillator connected to the active selected external 2-terminal crystal. When this bit is 0, then the active oscillator is enabled. When this bit is 1, then the active oscillator is disabled and the corresponding CLKI input is masked off. The active clock is defined as either the 28 MHz clock (CLK2I) for LCD mode, or for CRT modes the clock selected by the Clock Select bits in Misc. Output Register 3C2H bits 3,2. In all modes, the unselected clock oscillator is automatically disabled.

# Aux Reg Only Decode

The Aux Reg Only Decode bit is intended for use by power save mode software. In power save modes, this bit may be set to 1 to disable all I/O access decoding except to the Auxiliary Registers. Note that setting this bit to 1 would normally be useful only when in Power Save Modes 3 or 4. At all other times this bit should be set to 0 to enable all I/O address decoding.

# Power Save Mode Select Bits 2-0

These bits are used to select 1 of 5 software power save modes. When these bits are set to 000, 110, or 111 then the chip operates in normal active mode. Binary values of 001, 010, 011, 100, or 101 written to these bits cause the chip to enter power save modes 1, 2, 3, 4 or 5 respectively. If the /SUSPEND input pin is low, then the power save mode setting in this register is ignored.

| 04 General St        | 04 General Storage and Test Register 0 RW |                      |                      |                       |                       |                       |                       |  |  |  |

|----------------------|-------------------------------------------|----------------------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| Test Input<br>Select | Test Input<br>Select                      | Test Input<br>Select | Test Input<br>Select | Test Output<br>Select | Test Output<br>Select | Test Output<br>Select | Test Output<br>Select |  |  |  |

| Bit 3                | Bit 2                                     | Bit 1                | Bit 0                | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 |  |  |  |

# **General Storage and Test Bits**

For normal operation, Auxiliary Register 00 bit 4 (Test Mode Enable) is set to 0, and then the General Storage and Test Register can be used to provide 8 bits of read/write temporary storage. In normal operation mode these bits have no effect on hardware.

When the Test Mode Enable bit is set to 1, then the chip is placed in a special test mode, and this register is used to select various internal test functions.

| 05 Extended Function Register 1 RW |     |                               |                   |                              |                                    |                                         |                                    |  |  |

|------------------------------------|-----|-------------------------------|-------------------|------------------------------|------------------------------------|-----------------------------------------|------------------------------------|--|--|

| n/a<br>(reserved)                  | n/a | Sprite/HW<br>Cursor<br>Enable | n/a<br>(reserved) | Start<br>Address Bit<br>SA16 | Extended<br>Display<br>Page Enable | Overlay /<br>Ext Display<br>Page Select | CPU Upper<br>256K Access<br>Enable |  |  |

# **Sprite / HW Cursor Enable**

This bit is used to enable the sprite and hardware cursor functions. When this bit is set to 0, the sprite / hardware cursor function is disabled. When this bit is set to 1, the sprite / hardware cursor is enabled - see Section on sprite / hw cursor registers for more information.

# Start Address Bit SA16

This bit is used to set the most significant diplay start address bit when utilizing the upper 256K bytes of display memory to provide the Extended Display Page function (see below). Along with the lower 16 bits of start address in CRTC registers 0C and 0D, this bit allows setting the start address of the image displayed to be anywhere in the 512K address space. For this bit to have an effect, the Extended Display Page Enable bit must be set to 1 and the Overlay/Extended Display Page Select bit must be set to 0.

# **Extended Display Page Enable**

This bit is used to enable the Extended Display Page function. This function allows the display memory to wrap into the upper 256K bytes, and for 256K bytes of memory to be displayed starting anywhere in the entire 512K byte extended display memory space. If this bit is set to 1 and the Overlay / Ext Display Page Select bit is set to 0, then the extended display page function is enabled. If this bit is set to 0 or if the Overlay / Ext Display Page Select bit is set to 1, then the extended display page function is disabled, and the Overlay Modulation function may be enabled.

# **Overlay / Ext Display Page Select**

This bit is used to select between the two options which utilize the upper 256K bytes of display memory available. When this bit is 0, if the Extended Display Page Enable bit is set to 1, then the Extended Display Page function is selected. If this bit is set to 1, then the Overlay function is enabled. Enabling the

S-MOS Systems, Inc. • 2460 North First Street • San Jose, California 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238

Overlay function causes the image stored in the upper 256K bytes of display memory to be overlayed with the primary image in the lower 256K bytes of memory, as controlled by the bits in the Overlay Modulation Register.

# CPU Upper 256K Access Enable

This bit is used to enable CPU accesses into the upper 256K bytes of display memory. When this bit is set to 1, the CPU can access the upper half of display memory through memory addresses B0000 - BFFFF. The lower 256K of video memory can still be accessed at addresses A0000 - AFFFF. When this bit is set to 0, only the lower 256K bytes of display memory can be accessed by the CPU. Note that the Upper Page Swap Enable bit can be used to swap the upper/lower page addresses. This function will only be useful in planar graphics modes.

| 06 Overlay Modulation Register RW |            |            |            |            |            |            |            |  |  |

|-----------------------------------|------------|------------|------------|------------|------------|------------|------------|--|--|

| Overlay                           | Overlay    | Overlay    | Overlay    | Overlay    | Overlay    | Overlay    | Overlay    |  |  |

| Modulation                        | Modulation | Modulation | Modulation | Modulation | Modulation | Modulation | Modulation |  |  |

| Bit 7                             | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      |  |  |

# **Overlay Modulation Bits 7-0**

The Overlay Modulation bits are used to control the Overlay function. This function allows the image stored in the upper 256K bytes of display memory to be overlayed with the primary image in the lower 256K bytes of memory. When the Overlay / Ext Display Page Select bit is set to 0, this register has no effect. When the Overlay / Ext Display Page Select bit is set to 1, the Overlay function is enabled and these bits will control the modulation of the two images from each half of the 512K bytes of display memory. An 8 vertical frame cycle used to modulate the overlay and primary image and the 8 bits in this register are each used to represent one frame in sequence of the 8 frame cycle. Each 1 in this register causes the overlay image to be displayed for the corresponding frame in the 8 frame cycle, and each 0 causes the primary image to be displayed for the corresponding frame. For example, the value 01010101 in this register are set to 0, then only the primary image will be displayed, and similarly if all bits in this register are set to 1, then only the overlay image will be displayed.

| 07 Extended                      | Function Regis       | ter 2 RW |                                    |                                    |                                    |                               |                           |

|----------------------------------|----------------------|----------|------------------------------------|------------------------------------|------------------------------------|-------------------------------|---------------------------|

| Mode 13H<br>32/64 Gray<br>Select | Dithering<br>Control | n/a      | Graphics<br>VExpand<br>Start Bit 2 | Graphics<br>VExpand<br>Start Bit 1 | Graphics<br>VExpand<br>Start Bit 0 | Graphics<br>VExpand<br>Enable | Text<br>VExpand<br>Enable |

# Mode 13H 32/64 Gray Select

This bit allows the selection of 32 or 64 gray shades on the LCD panel when in mode 13H (Graphics Controller Mode Register inded 05, bit 6 Mode13H Select = 1). When this bit is 0, 64 gray shades are displayed in mode 13H (16 gray levels by FRM + dithering). When this bit is 1, then 32 gray shades are displayed in mode 13H (16 gray levels by FRM + dithering). This bit has no effect on an image displayed on a CRT display.

# **Dithering Control**

This bit is used to control the dithering logic for the LCD display. When this bit is 0, dithering is enabled for mode 13H (Graphics Controller register 05 bit 6 = 1) and disabled for other modes - this is the normal setting to provide 64 gray shades in mode 13H. When this bit is set to 1, then dithering is disabled for mode 13H. This bit has no effect on an image displayed on a CRT display.

S-MOS Systems, Inc. • 2460 North First Street • San Jose, California 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238

# **Graphics VExpand Start Bits 2-0**

These bits allow some flexibility in the graphics mode vertical expansion function. If graphics vertical expansion is enabled (see below), then these bits determine the position (0-5) of the first duplicated line on the LCD display. Values of 6 or 7 programmed into this register are invalid and vertical expansion will not occur in these cases. If CRT mode is enabled (Aux[0B] bit 1 = 1) then vertical expansion is disabled and this bit has no effect. Note that although vertical expansion will not occur when these bits are programmed to values 6 or 7, autocentering will still be disabled.

# **Graphics VExpand Enable**

This bit is used to enable vertical expansion of 400 line graphics modes on the LCD display, using selective line duplication. If this bit is 0, then vertical expansion of graphics modes is disabled. If this bit is set to 1, then 400 line graphics modes are expanded vertically to fill the screen. All the following conditions must be true for graphics vertical expansion to occur:

- 1) Graphics VExpand Enable = 1

- 2) 400 line mode set, i.e. CRTC register 12H and associated overflow bits = 18FH

- 3) graphics mode set, i.e. Graphics Controller register 06H bit 0 = 1

- 4) Graphics VExpand Start Bits 2:0 must be programmed to a value from 0 to 5 inclusive

If a 400 line graphics mode is not set, then graphics expansion will not occur and this bit will have no effect. Note that if all conditions for graphics vertical expansion are met, then the Auto Centering Enable bit (Auxiliary Register 01 bit 1) is ignored and autocentering is disabled.

If CRT mode is enabled (Aux[0B] bit 1 = 1) then graphics vertical expansion is disabled and this bit has no effect.

# **Text VExpand Enable**

This bit is used to enable vertical expansion of 400 line text modes on the LCD display, using selective line duplication. If this bit is 0, then vertical expansion of text modes is disabled. If this bit is set to 1, then 400 line text modes are expanded vertically to fill the screen, provided the following conditions are true:

- 1) 16 point font is set, i.e. the 5 least significant bits of CRTC register 09H = 0FH

- 2) 400 line mode is set, i.e. CRTC register 12H and associated overflow bits = 18FH

- 3) text mode is set, i.e. Graphics Controller register 06H bit 0 = 0.

If these conditions are not all met, then text expansion will not occur and this bit will have no effect. Note that if this bit is set to 1, then the Auto Centering Enable bit (Auxiliary Register 01 bit 1) is ignored and autocentering is disabled.

If CRT mode is enabled (Aux[0B] bit 1 = 1) then text vertical expansion is disabled and this bit has no effect.

S-MOS Systems, Inc. • 2460 North First Street • San Jose, California 95131 • Tel: (408) 922-0200 • Fax: (408) 922-0238

| 08 Primary R           | evision Code R         | legister RO            |     |     |         |         |         |

|------------------------|------------------------|------------------------|-----|-----|---------|---------|---------|

| Primary                | Primary                | Primary                | n/a | n/a | Monitor | Monitor | Monitor |

| Revision<br>Code Bit 2 | Revision<br>Code Bit 1 | Revision<br>Code Bit 0 |     |     | ID      | ID      | ID      |

| Code Bit 2             | Code Bit I             | Code Bit 0             |     |     | Bit 2   | Bit 1   | Bit 0   |

#### Primary Revision Code Bits 2-0

The Primary Revision Code Bits 2 to 0 are read-only bits permanently set to 1. The current revision code of the chip is a combination of the primary and secondary revision code values. The secondary revision code bits are contained in register 0FH.

# Monitor ID Bits 2-0

The Monitor ID Bits allow software to read the status on the monitor sense input pins MS[2:0]. These inputs are not latched and have internal pullups, so if nothing is connected to them these register bits will read 111.

| 09 Sprite Wri | 09 Sprite Write Select Register RW |     |     |                       |                                |                           |                                |  |  |  |  |

|---------------|------------------------------------|-----|-----|-----------------------|--------------------------------|---------------------------|--------------------------------|--|--|--|--|

| n/a           | n/a                                | n/a | n/a | Sprite Page<br>Select | Sprite<br>Logical<br>Plane Sel | Upper Page<br>Swap Enable | Sprite Write<br>Mode<br>Enable |  |  |  |  |

#### **Sprite Page Select**

This bit is used to select the current sprite page (page 0 or 1) accessed at the A000H address segment when the sprite write mode is enabled. The mapping of the sprite pages to the Sprite Page Select bit and the Upper Page Swap Enable bit are given in the following table:

| Upper Page Swap Enable | Sprite Page Select | Addressable Sprites |

|------------------------|--------------------|---------------------|

| 0                      | 0                  | 0 to 127            |

| 0                      | 1                  | 128 to 255          |

| 1                      | 0                  | 256 to 383          |

| 1                      | 1                  | 384 to 511          |

Note: Sprites 0 to 255 reside in standard VGA display memory space and should not be used.

#### **Sprite Logical Plane Select**

This bit is used in sprite write mode to select which sprite bit plane is currently being written. When this bit is set to 1, logical bit plane 1 is selected, and when this bit is set to 0, logical bit plane 0 is selected.

# **Upper Page Swap Enable**

The Upper Page Swap Enable bit is used to swap access addresses for the upper and lower 256 sprites. When this bit is set to 1, the upper 256 sprites residing in the B000H address segment can be addressed at