# PRELIMINARY DATA November 1993

The WEITEK Power 9100 is a high-performance display controller for use with graphical user interfaces such as Microsoft Windows. It combines an extremely highspeed frame buffer controller with a workstation-style accelerated display controller and a local-bus host interface for maximum performance.

#### Contents

| 1. Technical Overview      | 1          |

|----------------------------|------------|

| 2. Quick Reference         | 11         |

| 3. Memory Map              | 15         |

| 4. Registers               | 29         |

| 5. Commands                | 59         |

| 6. Host Interface          | 67         |

| 7. Frame Buffer Interface  | 75         |

| 8. Video and RAMDAC Inter  | face 89    |

| 9. Coprocessor Interface   | 101        |

| 10. Auxiliary Chip Control | 107        |

| 11. SVGA Overview          | 109        |

| 12. SVGA Registers         | 113        |

| 13. Specifications         | 183        |

| Sales Offices              | back cover |

|                            |            |

Power 9100 Data Book (Preliminary Data) November 1993

Copyright © WEITEK Corporation 1993 All rights reserved

WEITEK Corporation 1060 East Arques Avenue Sunnyvale, California 94086 Telephone (408) 738–8400

WEITEK Corporation assumes no responsibility for errors in this document, and retains the right to make changes at any time, without notice. Please contact your sales office to obtain the latest specifications before placing your order.

WEITEK is a trademark of WEITEK Corporation.

Microsoft and MS-DOS are registered trademarks and Windows is a trademark of Microsoft Corporation. RAMDAC is a trademark of Brooktree Corporation.

Written by Claire-Marie Costanza Edited by Robert Plamondon Additional writing by Robert Plamondon, D.R. Sevedge, and Allen Samuels. Illustrated by Claire-Marie Costanza, Robert Plamondon, Allen Samuels, and D.R. Sevedge

Printed in the United States of America 93 94 6 5 4 3 2 1

4710-9302-00 Rev. A

# PRELIMINARY DATA

November 1993

# Contents

## Chapter 1. Technical Overview, 1

Single-Chip 2-D Graphics Accelerator, 1 High Bandwidth, 1 Full Software Support, 1 Powerful Graphics Features, 1

1.1. Architecture, 2

1.1.1. Frame Buffer Controller, 2

1.1.2. Parameter Engine, 2

1.1.3. Drawing Engine, 3

1.1.4. Host Bus Interface, 3

1.1.5. Video Controller, 4

1.1.6. SVGA Unit, 4

1.2. Major Differences Between the Power 9100 and the Power 9000, 4

1.2.1. Additional Features, 4

1.2.2. Addressing, 4

1.3. Details of Graphics Operation, 5

1.3.1. The Graphics Pipeline, 5

1.3.2. Drawing Quadrilaterals, 5

1.3.3. Drawing Bit Maps, 6

1.3.4. Bit Block Transfer, 6

1.3.5. Color Selection, 6

1.4. Host Bus Interface, 7

1.5. Frame Buffer and Video Interfaces, 8

1.5.1. Signal Descriptions, 9

1.6. Video Coprocessor Interface, 10

1.7. Related Documents, 10

Chapter 2. Quick Reference, 11

Chapter 3. Memory Map, 15

and the state of the Million Sta

3.1. Overview, 15

3.1.1. Big-endian and Little-endian Modes, 15

- 3.2. Conventions and Notation, 16

- 3.3. Configuration Registers, 173.3.1. Power-up Configuration, 173.3.2. CONFIG[0] Register, 182.2.2. CONFIG[1] Particular Statements

- 3.3.3. CONFIG[1] Register, 18 3.3.4. CONFIG[2] Register, 18

- 3.3.5. CONFIG[3] Register, 18

- $2.2 \leftarrow CONFIC[4] Project 1$

- 3.3.6. CONFIG[4] Register, 19

- 3.3.7. CONFIG[7] Register, 19

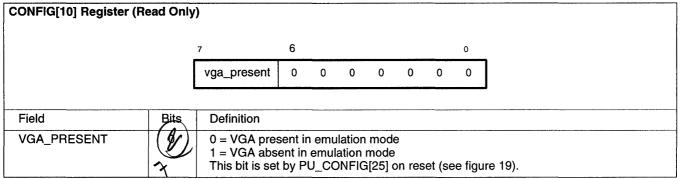

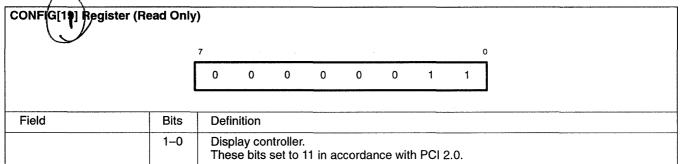

- 3.3.8. CONFIG[8] Register, 19 3.3.9. CONFIG[10] Register, 20

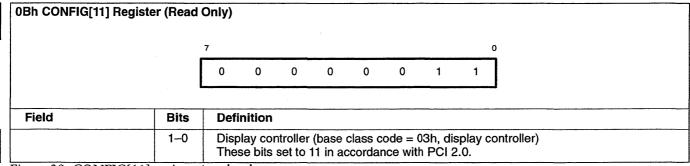

- 3.3.10. CONFIG[11] Register, 20

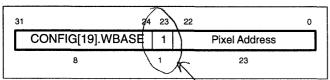

- 3.3.11. CONFIG[19] Register, 20

3.3.12. CONFIG[48] Register, 21

3.3.13. CONFIG[49] Register, 21

3.3.14. CONFIG[50] Register, 22

3.3.15. CONFIG[51] Register, 22

3.3.16. CONFIG[64] Register, 22

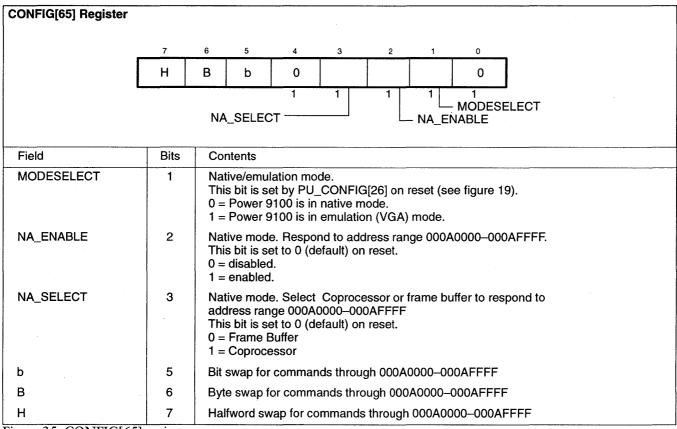

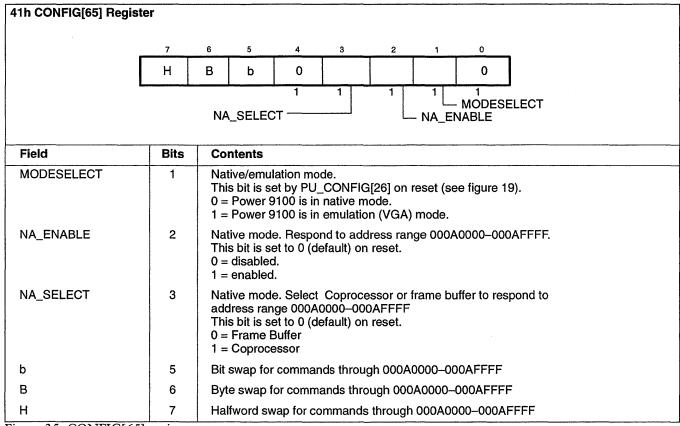

3.3.17. CONFIG[65] Register, 23

3.3.18. CONFIG[66] Register, 23

3.4. General Address Formats, 24

3.4.1. Linear Frame Buffer Addressing, 24

3.4.2. Alternate Frame Buffer Aperture Mapping, 24

3.4.3. ROM BIOS Access, 24

3.4.4. Coprocessor Access, 24

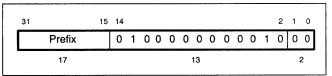

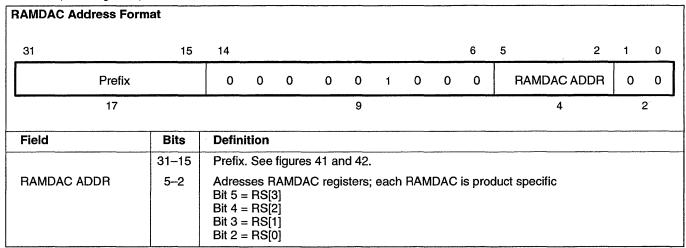

3.4.5. RAMDAC Address Format, 26

3.4.6. Video Coprocessor Interface, 26

i

## Chapter 4. Native Mode Registers, 29

- 4.1. Overview, 29

- 4.2. Register Summary, 30

- 4.3. System Control Registers, 33

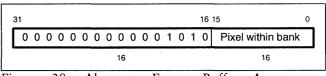

- 4.3.1. Alternate Read Bank Register, 34

- 4.3.2. Alternate Write Bank Register, 34

- 4.3.3. System Configuration Register, 34

- 4.3.4. Interrupt Register, 36

- 4.3.5. Interrupt Enable Register, 37

- 4.4. Parameter Engine Registers, 38

- 4.4.1. Device Coordinate Registers, 38

- 4.4.2. The Status Register, 39

- 4.4.3. Parameter Engine Control and Condition Registers, 40

- 4.5. Drawing Engine Registers, 46

4.5.1. Color Registers, 46

4.5.2. Plane Mask Register, 46

#### Chapter 5. Commands, 59

- 5.1. Load Coordinates Command, 60

- 5.2. Quad Command, 60

- 5.3. Blit Command, 61

- 5.4. Pixel8 Command, 62

- 5.5. Pixel1 Command, 63

- 5.5.1. Pixel1 Color Selection, 63

- 5.6. Next\_pixels Command, 64

Chapter 6. Host Interface, 67

6.1. Signal Description Conventions, 67

- 6.1.1. Input Signals, 67

- 6.1.2. Output Signals, 67

- 6.1.3. Tri-stated Signals, 67

- 6.1.4. Bidirectional Signals, 67

### 6.2. Host Bus Interface, 67

- 6.2.1. I/O Address decoding, 67

- 6.2.2. DAC Shadowing, 67

- 4.5.3. Draw\_mode Register, 47

- 4.5.4. Pattern Origin Registers, 47

- 4.5.5. Raster Register, 48

- 4.5.6. Pixel8 Register, 49

- 4.5.7. Window Minimum/Window Maximum Registers, 49

- 4.5.8. Pattern Registers, 49

- 4.5.9. Reserved For Software, 49

- 4.6. Video Control Registers, 51

- 4.7. VRAM Control Registers, 55

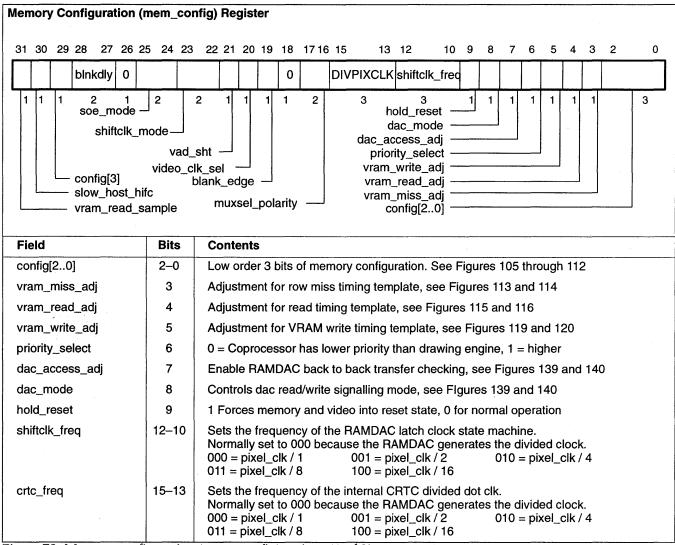

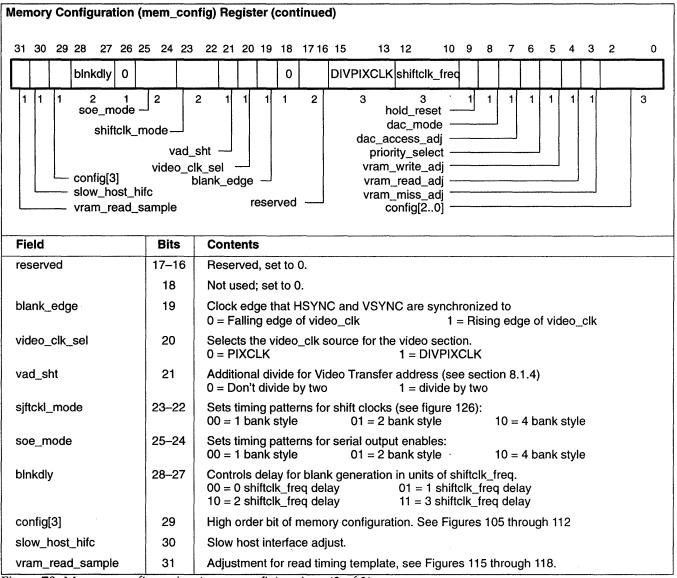

- 4.7.1. Memory Configuration Register, 55

- 4.7.2. Refresh Period Register, 55

- 4.7.3. Refresh Count Register, 55

- 4.7.4. RAS Low Register, 55

- 4.7.5. Low Current Register, 55

- 4.7.6. Power-up Configuration Register, 55

- 5.7. Drawing With the Power 9100, 65

- 5.7.1. Legal Quadrilaterals, 65

- 5.7.2. Drawing Modes, 65

- 5.7.3. Basic Quad Drawing Methods, 66

- 5.7.4. Negative Coordinates, 66

- 5.7.5. Flow Control, 66

- 5.7.6. Exception Handling, 66

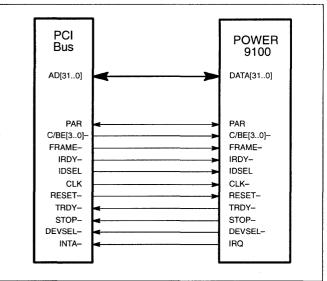

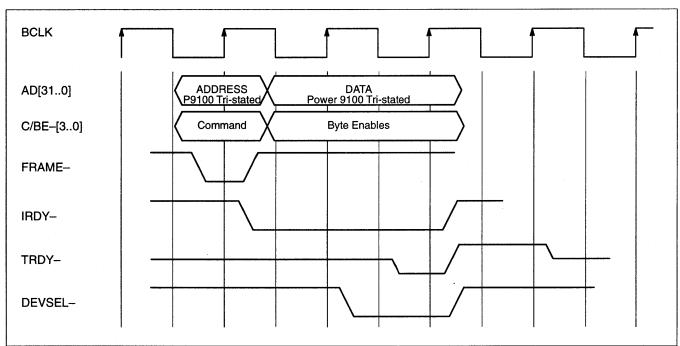

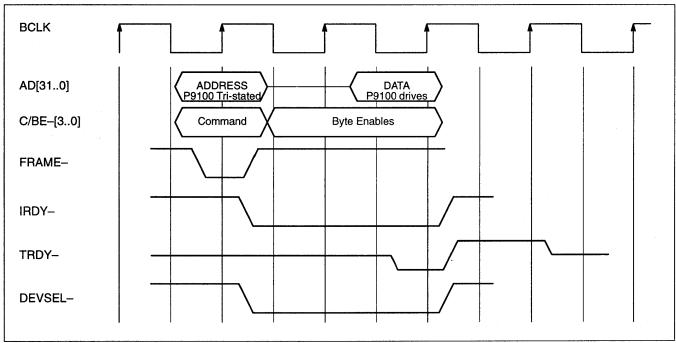

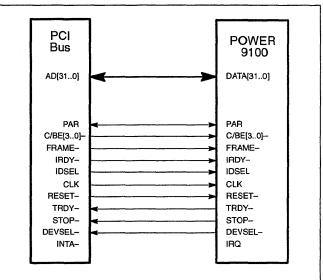

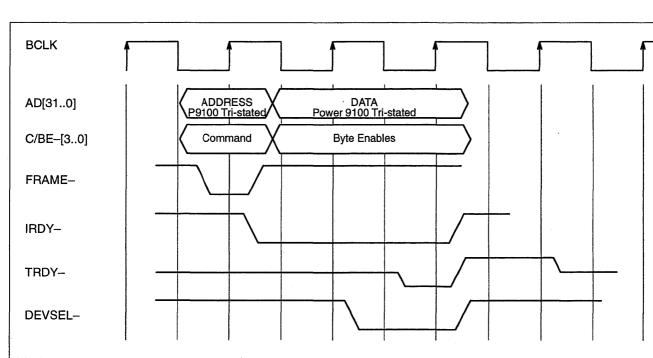

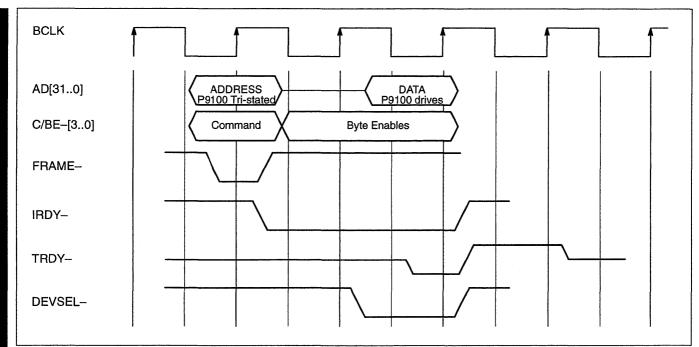

- 6.3. PCI Bus Operation, 68

- 6.3.1. PCI Bus Signal List, 68

- 6.3.2. PCI Bus Timings, 68

- 6.3.3. PCI Bus Configuration Registers, 68

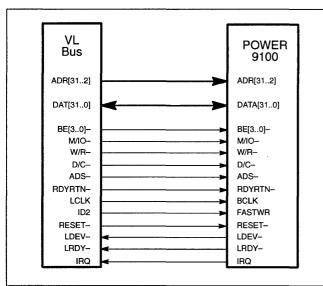

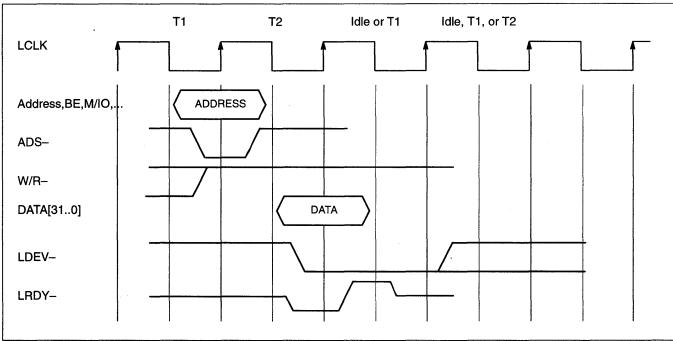

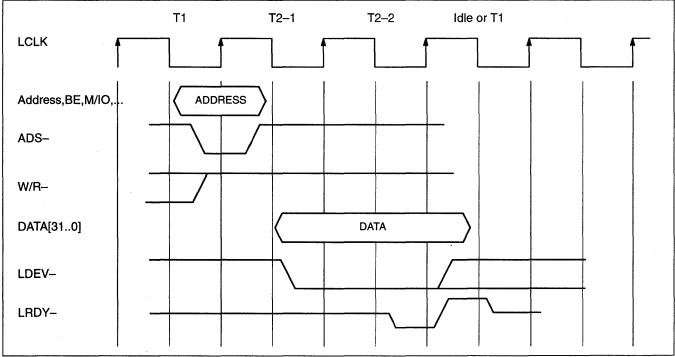

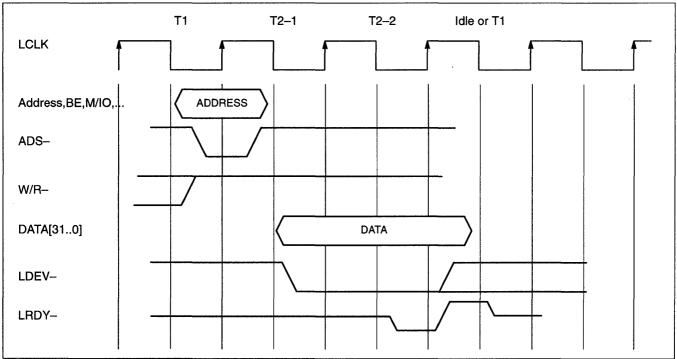

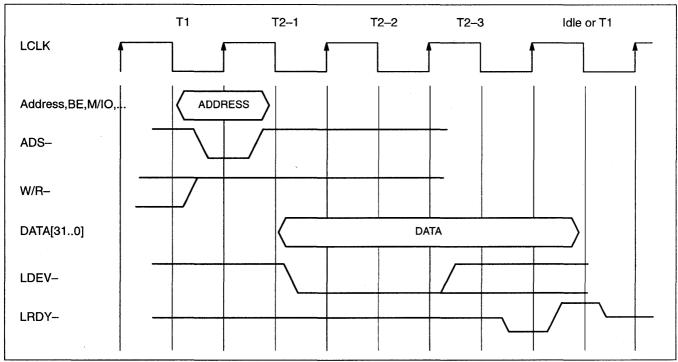

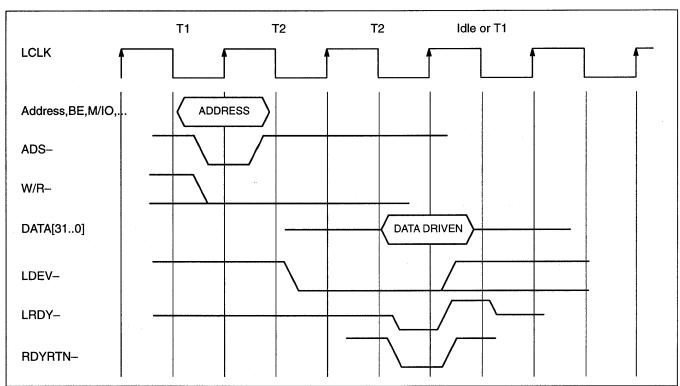

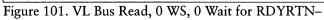

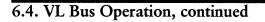

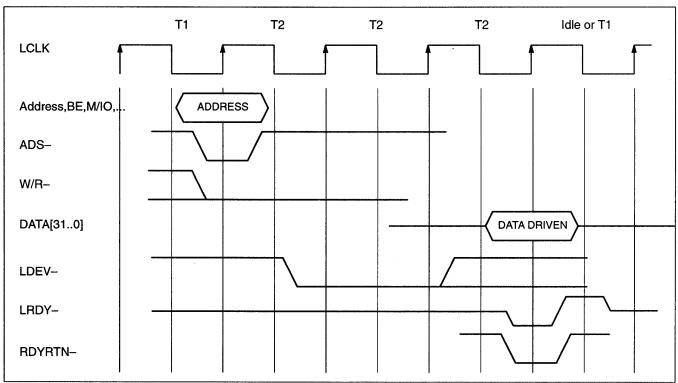

- 6.4. VL Bus Operation, 70

- 6.4.1. VL Bus Signal List, 70

- 6.4.2. VL Bus Timings, 70

- 6.4.3. VL Bus Operations Waveforms, 70

# PRELIMINARY DATA

November 1993

# Chapter 7. Frame Buffer Interface, 75

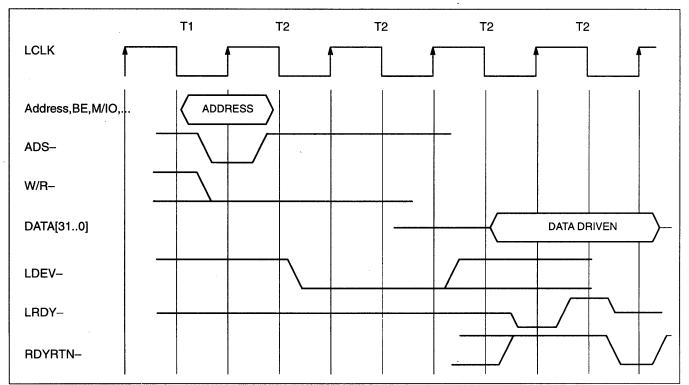

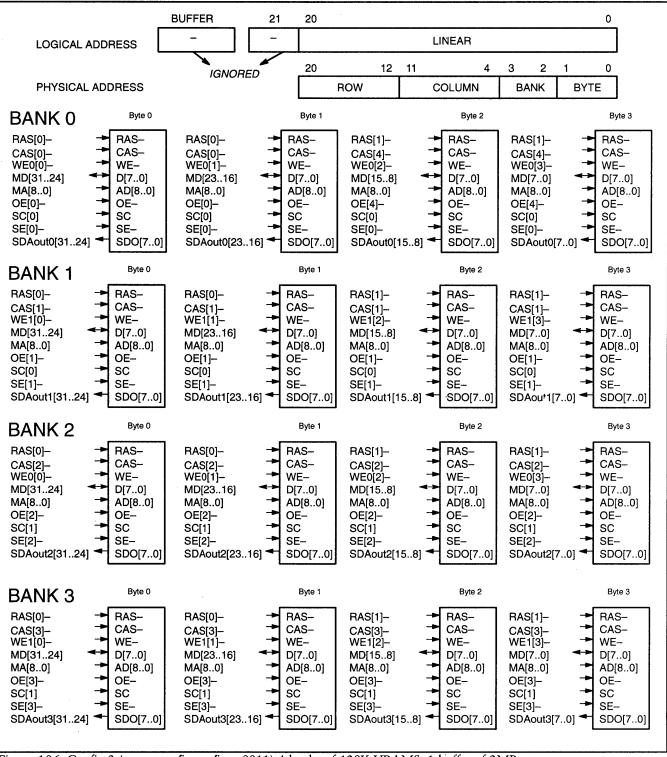

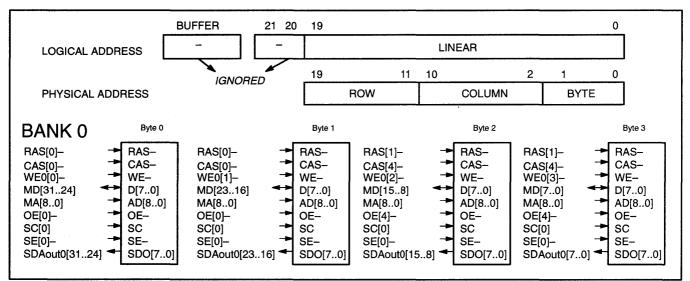

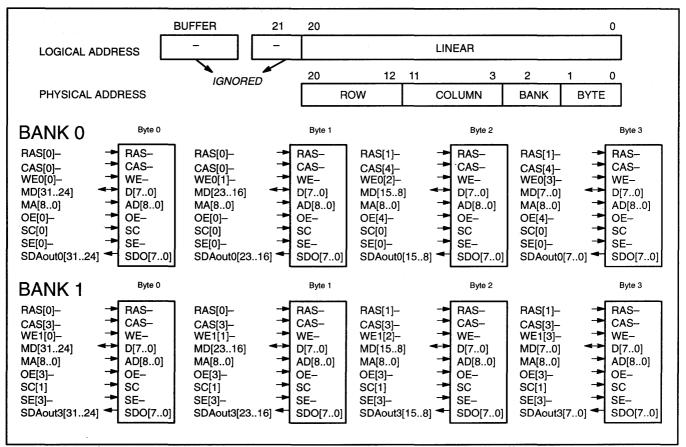

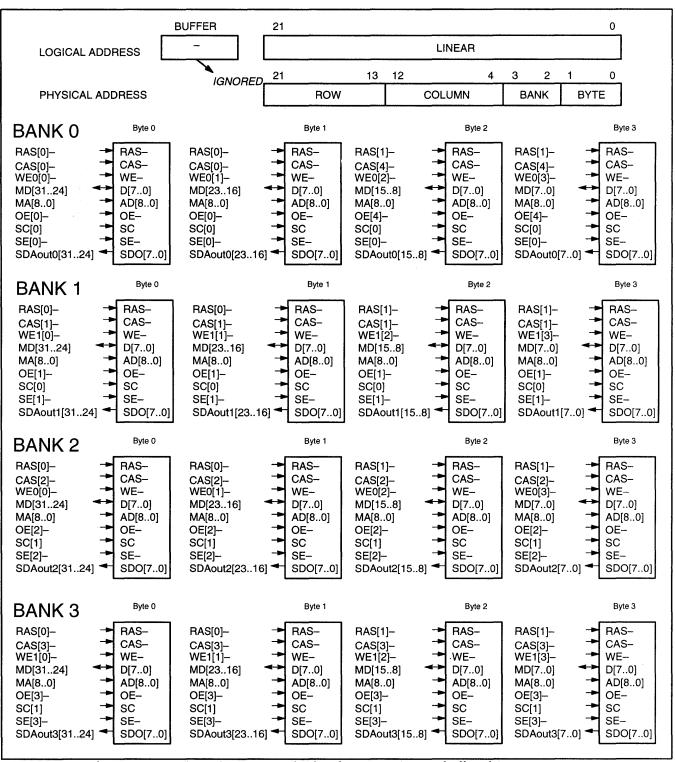

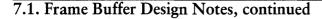

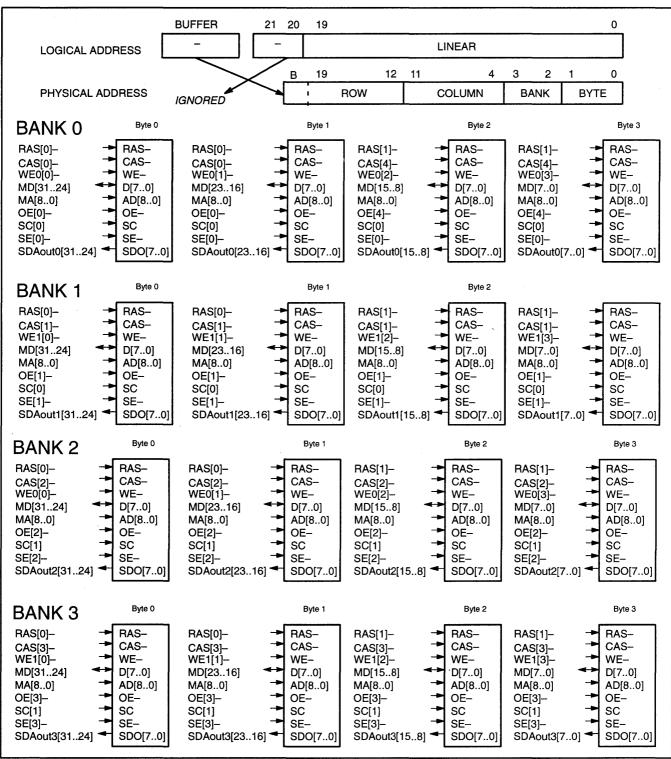

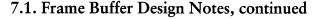

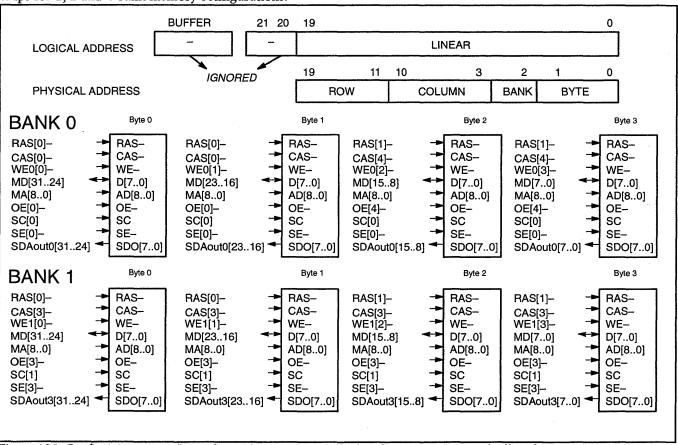

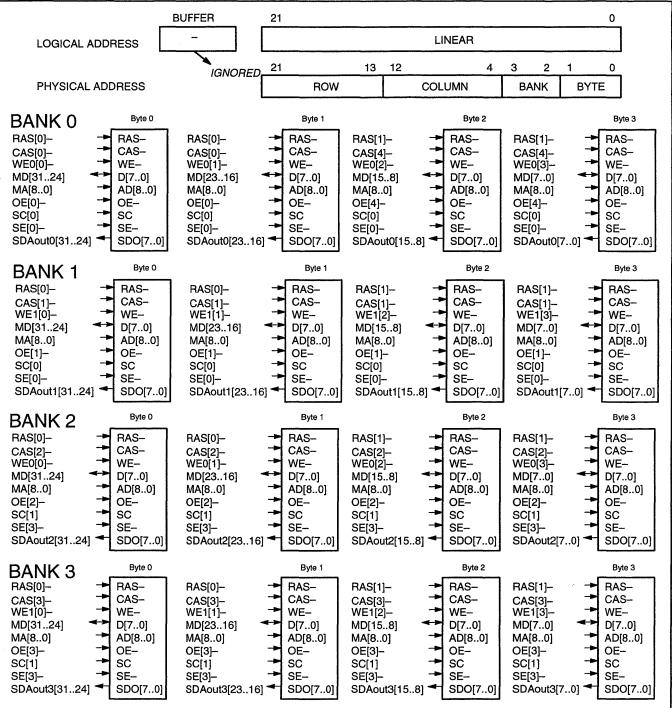

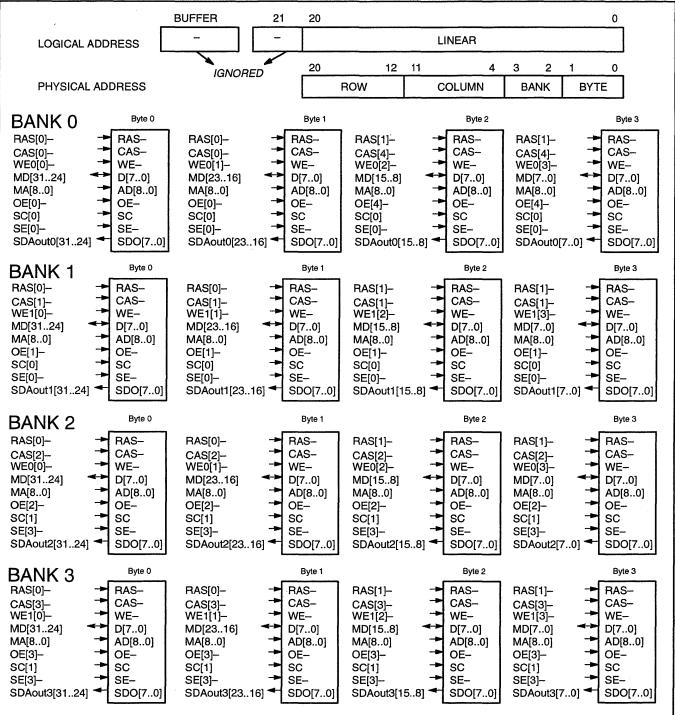

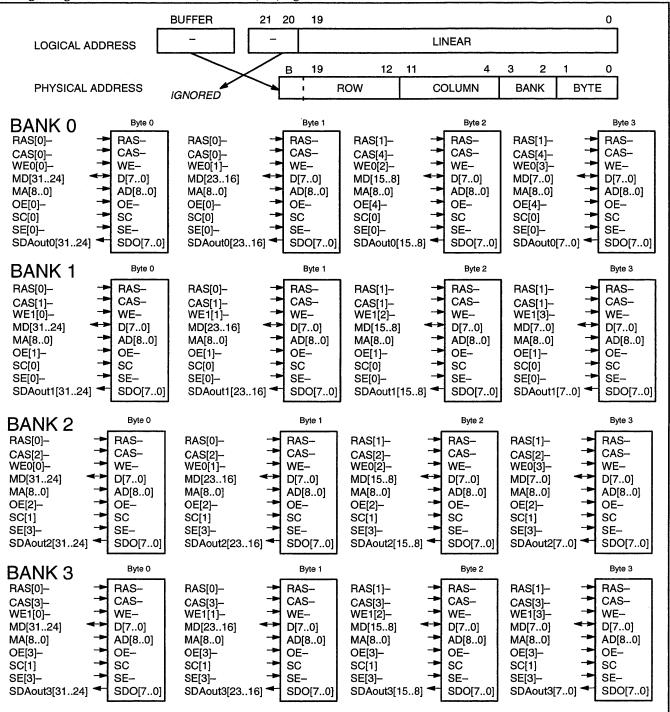

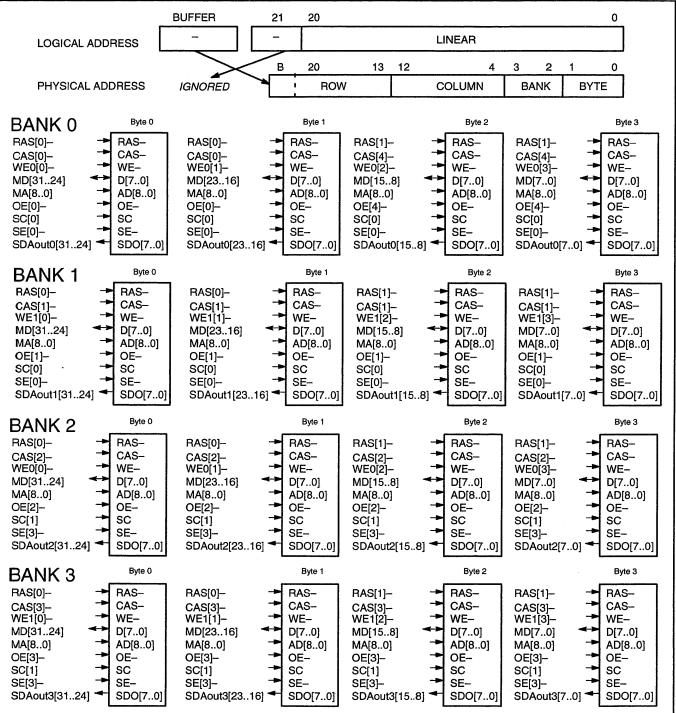

7.1. Frame Buffer Design Notes, 75

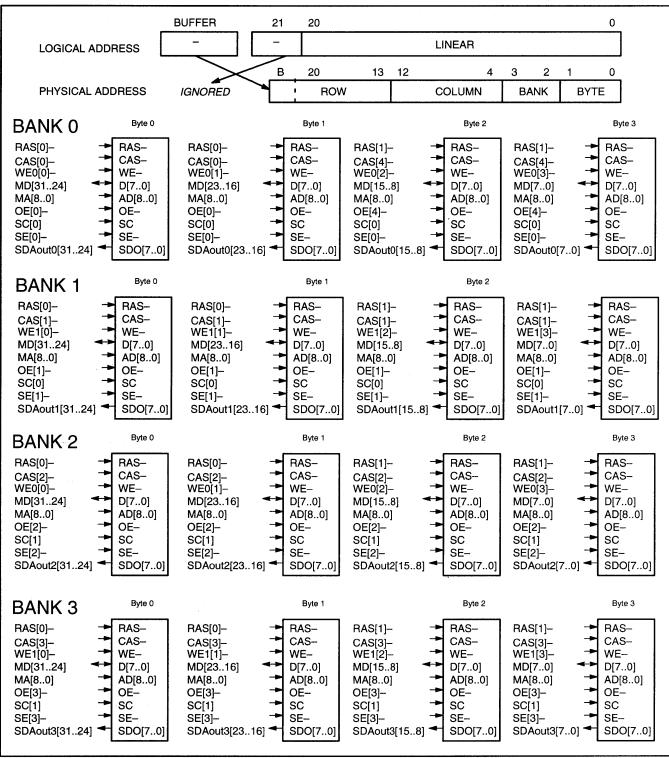

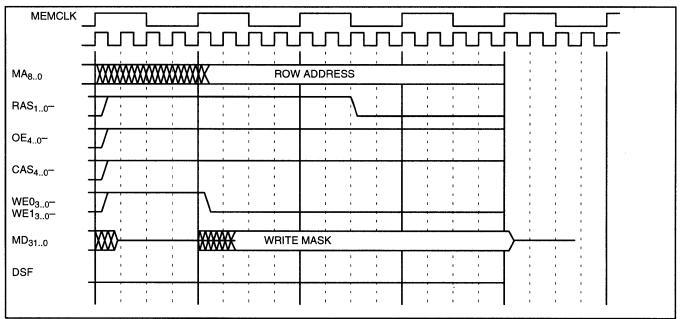

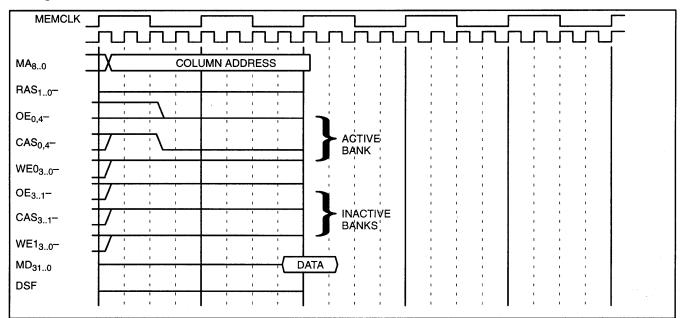

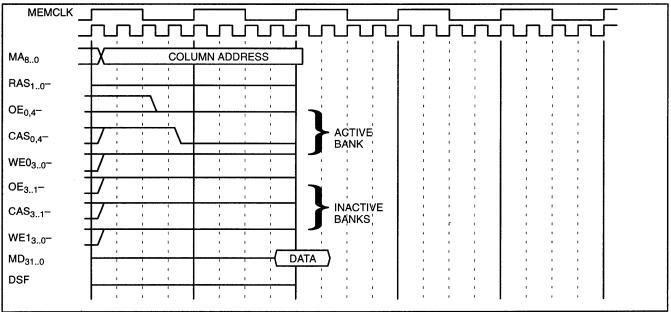

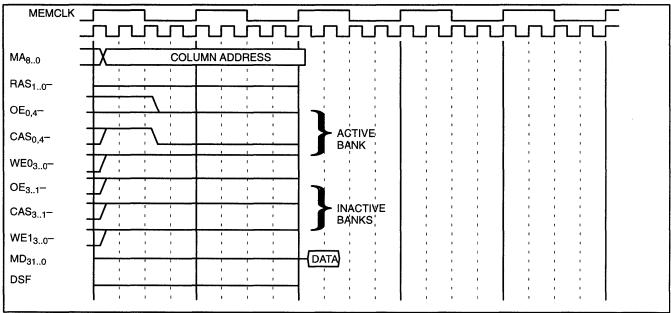

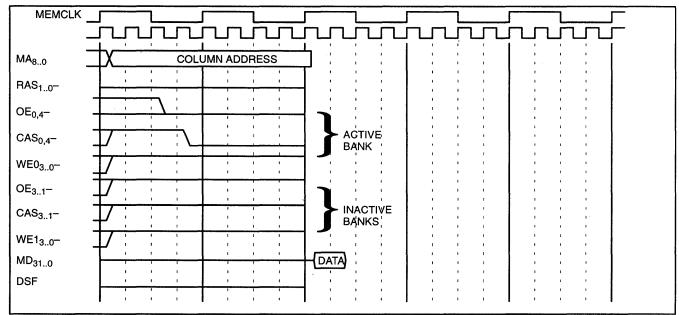

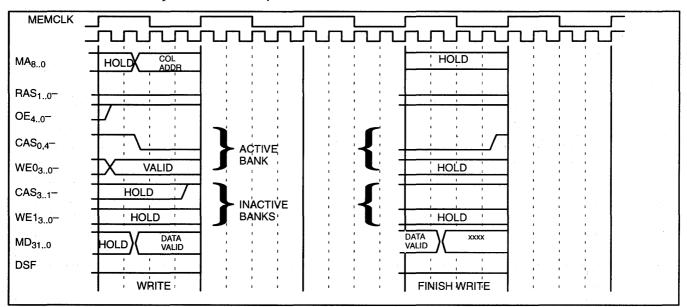

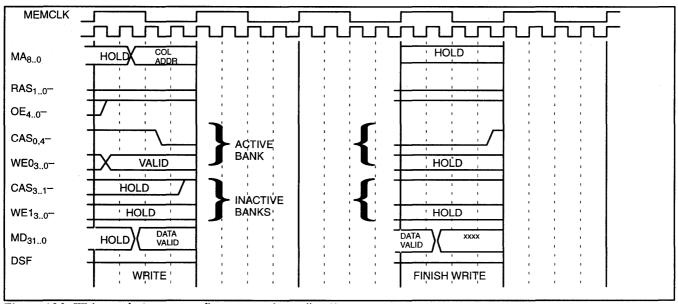

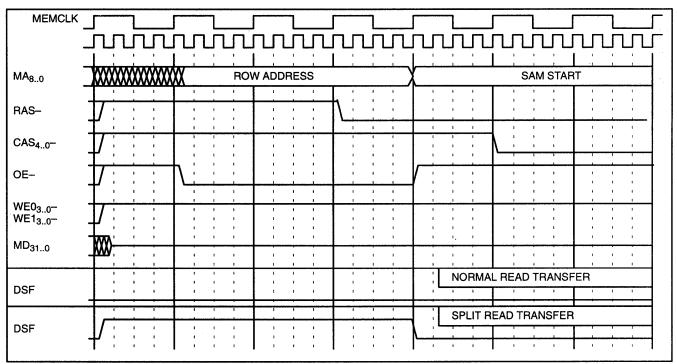

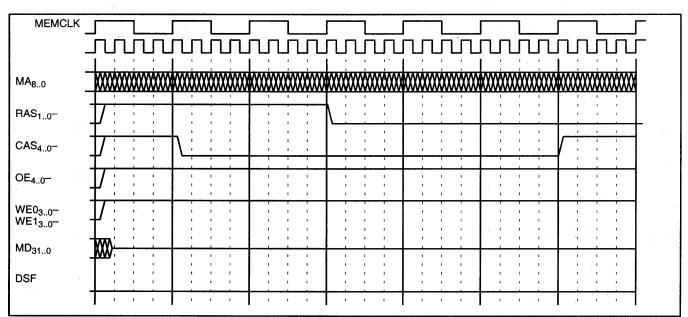

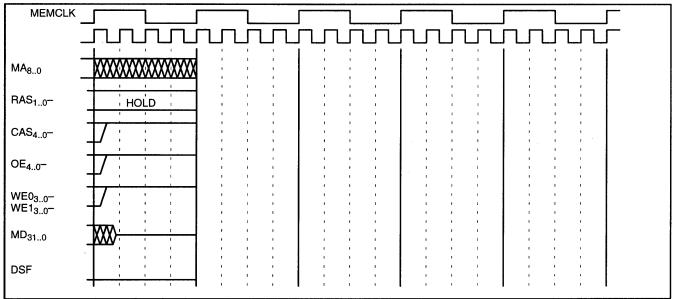

7.2. VRAM Access, 82

7.2.1. Row Miss, 82

7.2.2. Read, 83

7.2.3. Write, 85

Chapter 8. Video and RAMDAC Interface, 89

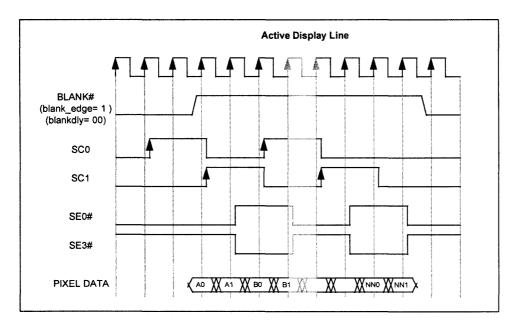

8.1. Video Control, 89

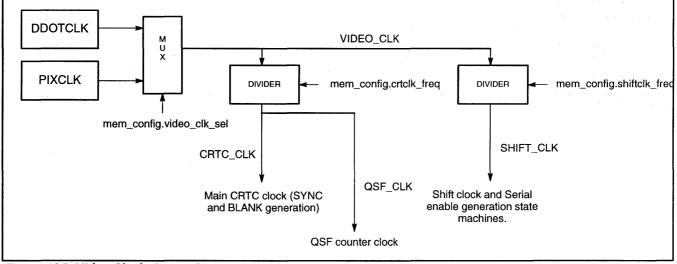

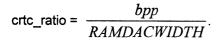

8.1.1. Video Clock generation, 89

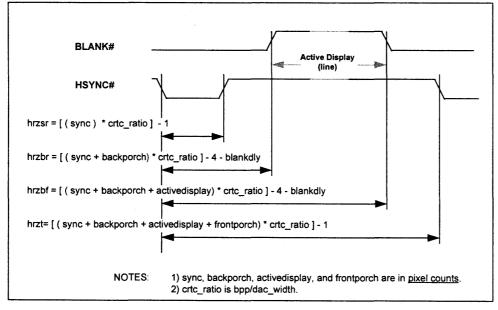

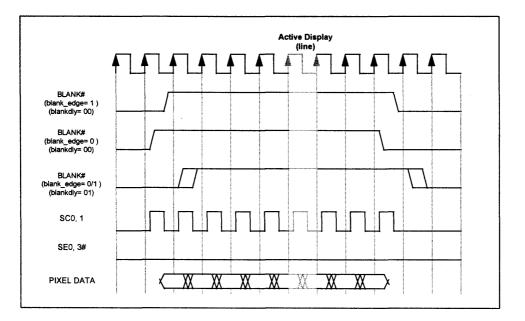

8.1.2. Video SHIFT Clock generation, 90

8.1.3. Video SERIAL ENABLE generation, 91

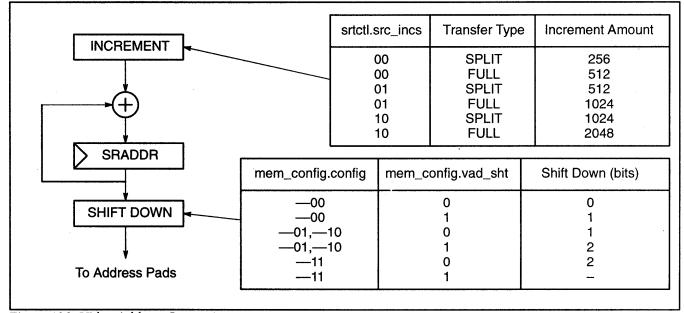

8.1.4. Video ADDRESS GENERATION, 92

8.1.5. Video Signals, 93

Chapter 9. Coprocessor Interface, 101

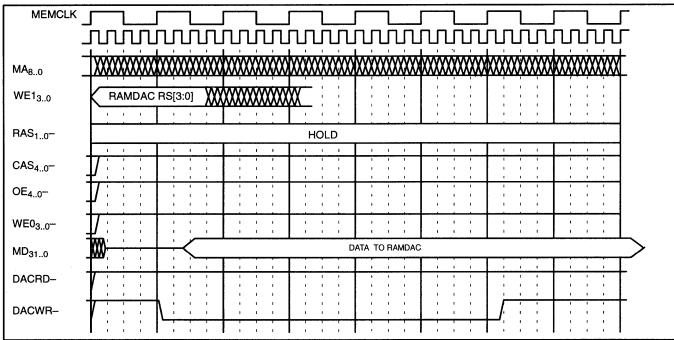

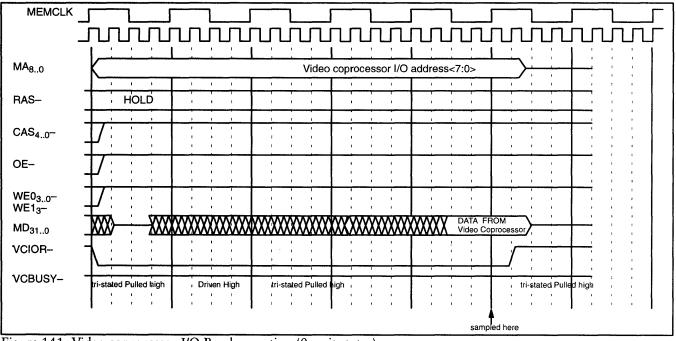

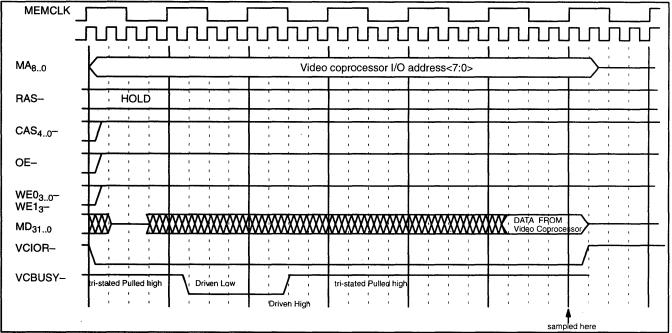

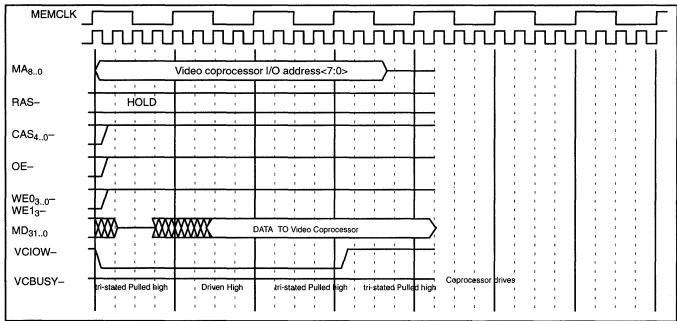

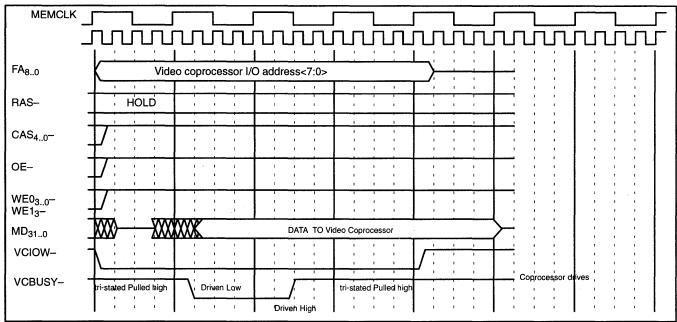

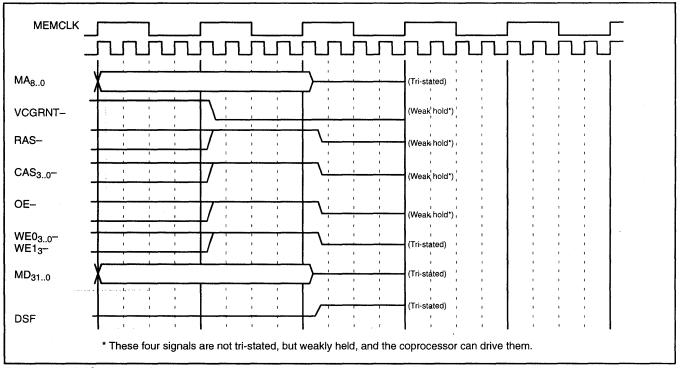

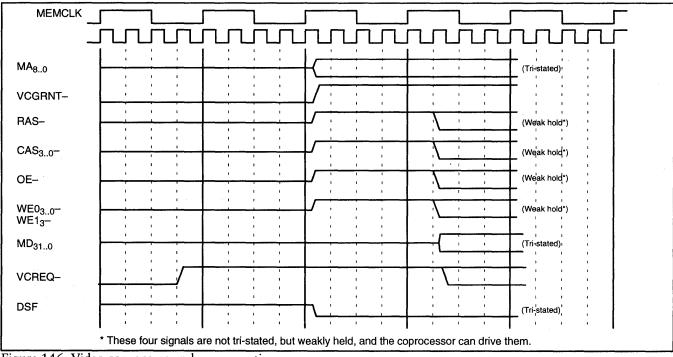

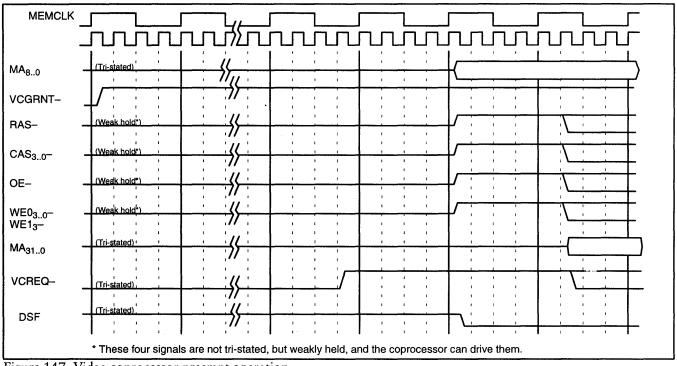

9.1. Video Coprocessor I/O Read, 1029.2. Video Coprocessor I/O Write, 1039.3. Video Coprocessor Grant, 104

Chapter 10. Auxiliary Chip Control, 107

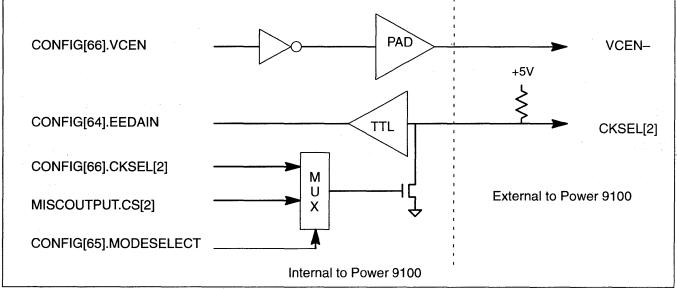

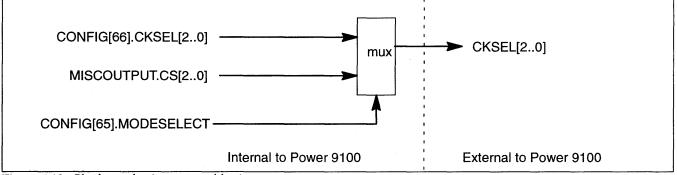

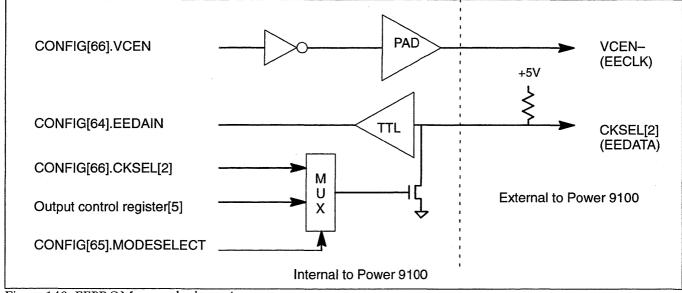

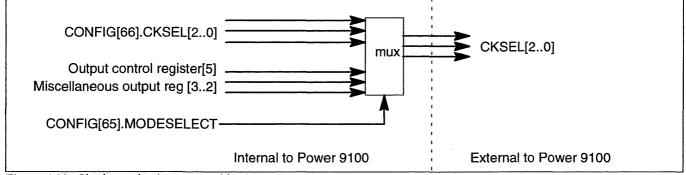

10.1. EEPROM Control, 10710.2. Clock Synthesizer Control, 107

Chapter 11. SVGA Overview, 109

11.1. SVGA Compatible Text/Graphics Engine, 109 11.2. Enhanced Display Modes, 110 7.2.4. Read Transfer, 867.2.5. Refresh, 877.2.6. Idle, 877.2.7. Reset State, 88

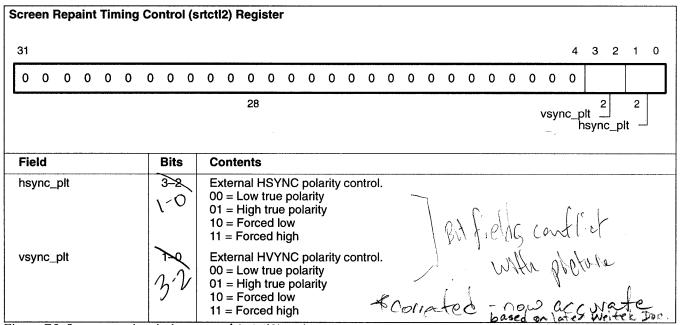

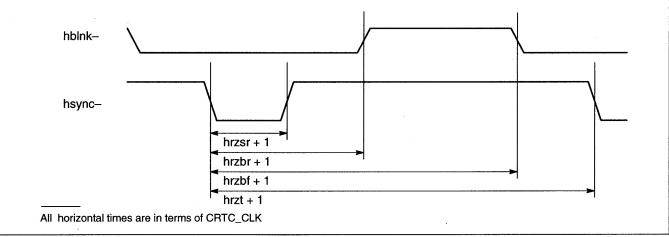

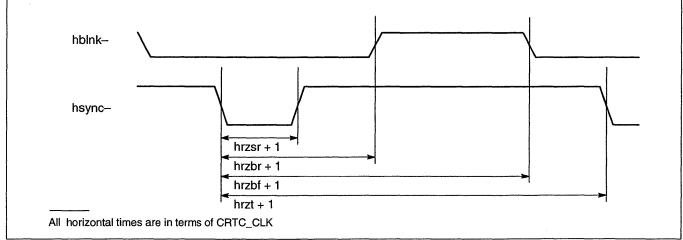

8.1.6. Video Control Registers, 93

8.1.7. Video Timing, 95

8.1.8. External Synchronization, 96

8.1.9. Screen Repaint Control, 96

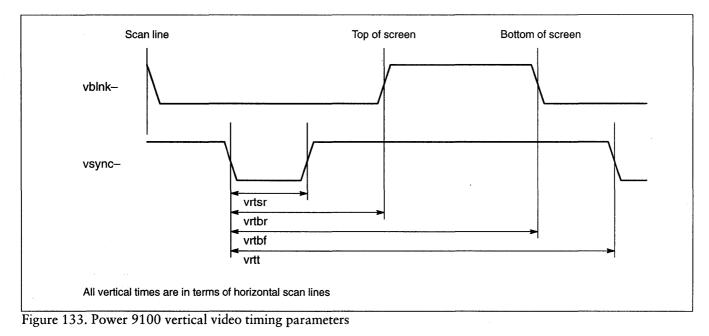

8.2. RAMDAC, 98

9.4. Video Coprocessor Release, 1059.5. Video Coprocessor Preempt, 106

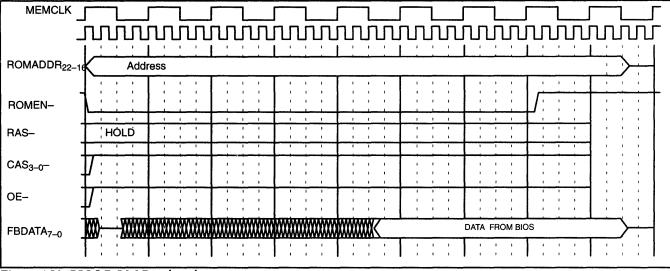

10.3. BIOS Access, 108

11.3. Signal Description, DRAM32 System, 111

## Chapter 12. SVGA Registers, 113

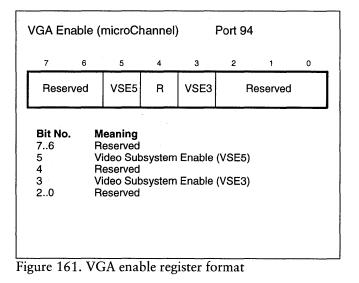

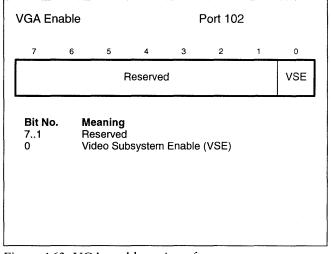

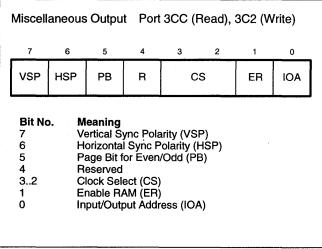

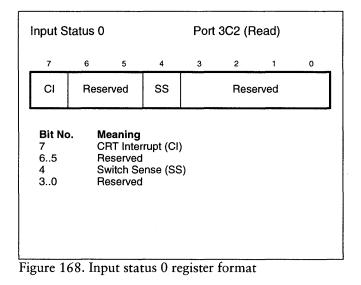

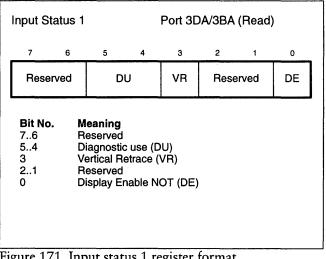

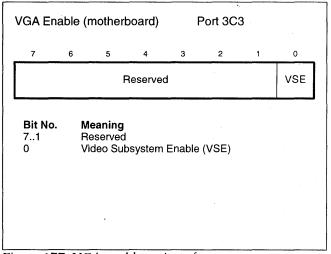

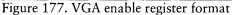

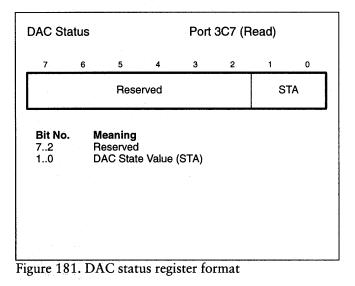

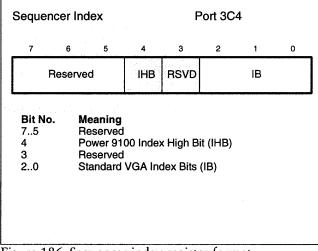

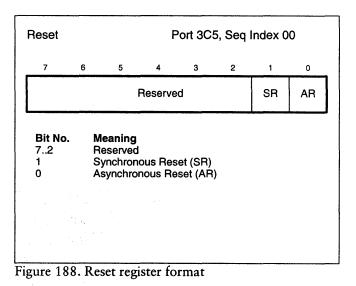

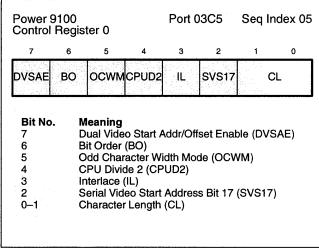

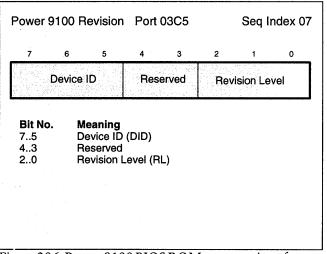

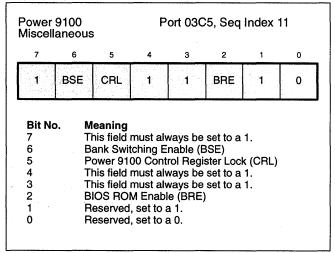

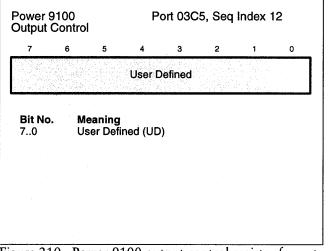

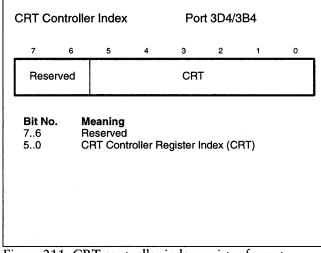

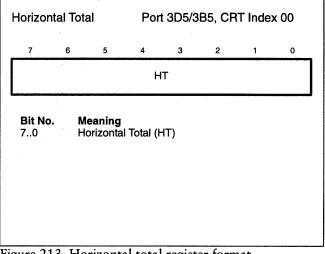

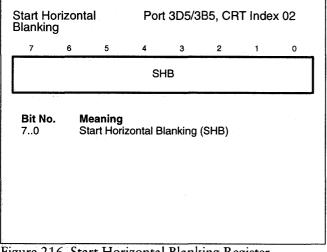

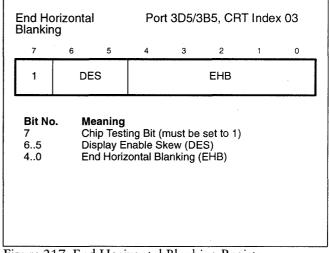

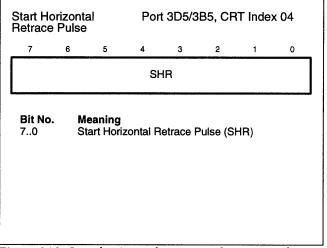

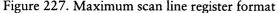

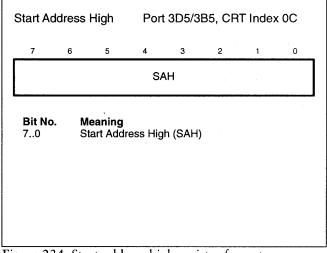

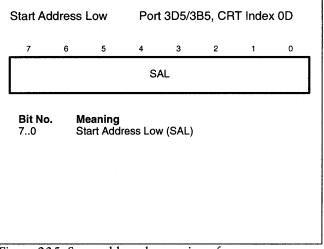

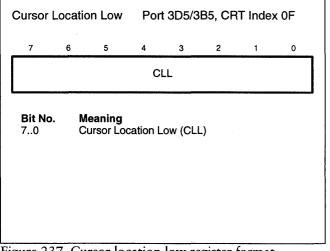

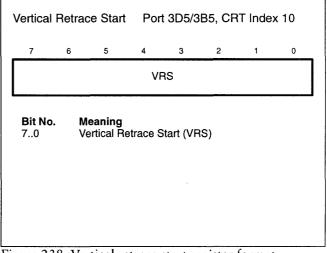

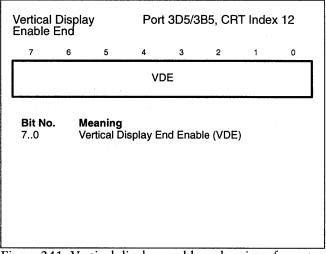

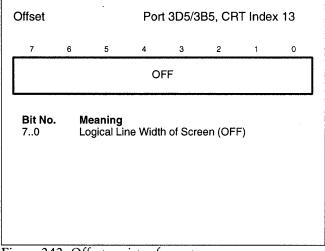

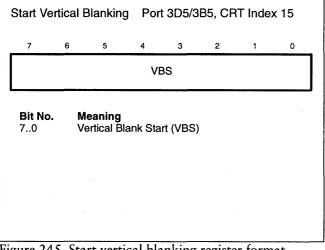

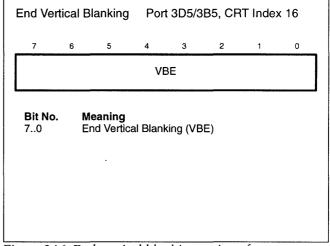

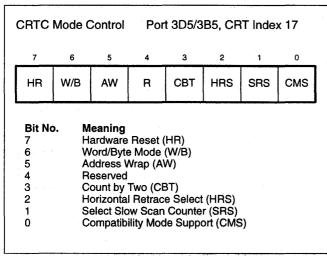

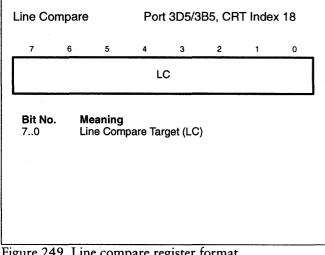

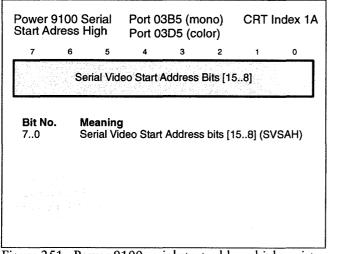

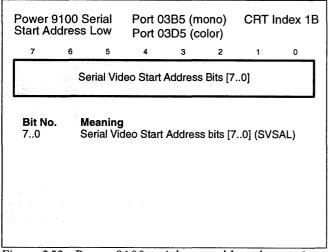

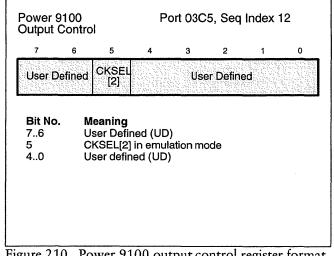

12.1. WEITEK-Specific Registers, 113 12.1.1. Power 9100 Extended Registers, 113 12.1.2. Power 9100 Additional I/O Port, 114 12.1.3. Power 9100 Extended Bit Definitions, 114 12.2. Register Groups, 115 12.2.1. VGA and WEITEK Register Groups, 115 12.2.2. Registers Organized by Group, 115 12.3. Memory Map, 122 12.4. General Registers, 127 12.4.1. VGA Enable Register, 128 12.4.2. VGA Enable Register, 128 12.4.3. Miscellaneous Output Register, 129 12.4.4. Input Status 0 Register, 130 12.4.5. Input Status 1 Register, 131 12.4.6. Feature Control Register, 132 12.4.7. VGA Enable Register, 132 12.4.8. DAC Status Register, 133 12.4.9. VGA Enable Register, 133 12.4.10. Power 9100 Bank Select Register, 134 12.5. Sequencer Registers, 135 12.5.1. Sequencer Index Register, 135 12.5.2. RESET Register, 136 12.5.3. Clocking Mode Register, 137 12.5.4. Map Mask Register, 138 12.5.5. Character Map Select Register, 139 12.5.6. Memory Mode Register, 140 12.5.7. Power 9100 Control Register 0, 141 12.5.8. Power 9100 Control Register 1, 142 12.5.9. Power 9100 Revision Register, 143 12.5.10. Power 9100 ID Register, 143 12.5.11. Power 9100 Miscellaneous Register, 144 12.5.12. Power 9100 Output Control Register, 145 12.6. CRT Controller Registers, 146 12.6.1. CRT Controller Index Register, 146 12.6.2. Horizontal Total Register, 147 12.6.3. Horizontal Display Enable End Register, 147 12.6.4. Start Horizontal Blanking Register, 148 12.6.5. End Horizontal Blanking Register, 148 12.6.6. Start Horizontal Retrace Pulse Register, 149 12.6.7. End Horizontal Retrace Register, 149 12.6.8. Vertical Total Register, 150 12.6.9. Overflow Register, 150 12.6.10. Preset Row Scan Register, 151 12.6.11. Maximum Scan Line Register, 152 12.6.12. Cursor Start Register, 153 12.6.13. Cursor End Register, 154 12.6.14. Start Address High Register, 154 12.6.15. Start Address Low Register, 155 12.6.16. Cursor Location High Register, 155 12.6.17. Cursor Location Low Register, 156 12.6.18. Vertical Retrace Start Register, 156 12.6.19. Vertical Retrace End Register, 157 12.6.20. Vertical Display Enable End Register, 158 12.6.21. Offset Register, 158 12.6.22. Underline Location Register, 159 12.6.23. Start Vertical Blanking Register, 160 12.6.24. End Vertical Blanking Register, 160 12.6.25. CRTC Mode Control Register, 161 12.6.26. Line Compare Register, 162 12.6.27. Power 9100 Interlace Register, 162 12.6.28. Power 9100 Serial Start Address High Register, 16312.6.29. Power 9100 Serial Start Address Low Register, 164 12.6.30. Power 9100 Serial Offset Register, 165

12.6.31. Power 9100 Total Characters Per Line Register, 166

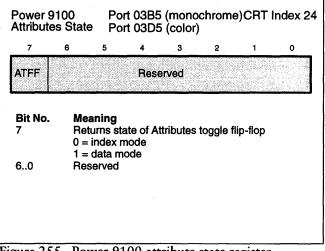

12.6.32. Power 9100 Attributes State Register, 167

## PRELIMINARY DATA November 1993

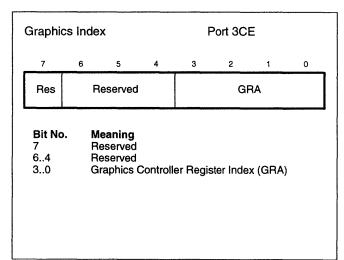

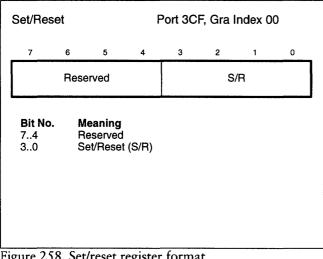

12.7. Graphics Controller Registers, 168

12.7.1. Graphics Index Register, 168

12.7.2. Set/Reset Register, 169

12.7.3. Enable Set/Reset Register, 169

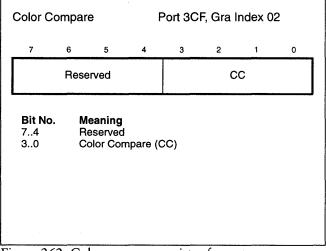

12.7.4. Color Compare Register, 170

12.7.5. Data Rotate Register, 171

12.7.6. Read Map Select Register, 172

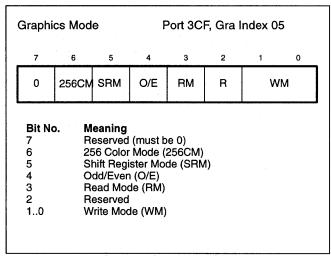

12.7.7. Graphics Mode Register, 173

12.7.8. Miscellaneous Register, 174

12.7.9. Color Don't Care Register, 175

12.7.10. Bit Mask Register, 175

Chapter 13. Specifications, 183

13.1. DC Specifications, 183

13.1.1. Absolute Maximum Ratings, 183

13.1.2. Recommended Operating Conditions, 183

13.1.3. Pin Capacitance, 183

13.1.4. DC Characteristics, 183

13.2. Supported Components, 184

13.2.1. Compatible VRAMs, 18413.2.2. Compatible RAMDACs, 18413.2.3. Compatible Clock Generators, 184

- 12.8. Attribute Controller Registers, 176

12.8.1. Attribute Index Register, 176

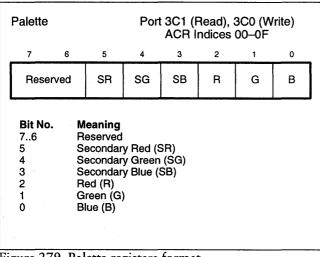

12.8.2. Palette Registers, 177

12.8.3. Attribute Mode Control Register, 178

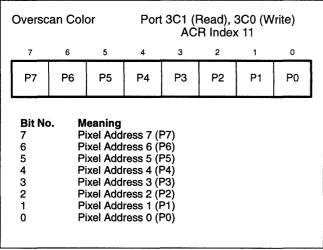

12.8.4. Overscan Color Register, 179

12.8.5. Color Plane Enable Register, 180

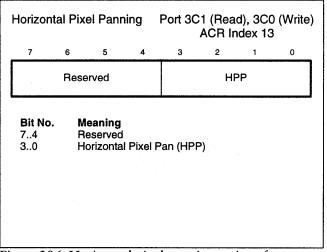

12.8.6. Horizontal Pixel Panning Register, 181

12.8.7. Color Select Register, 182

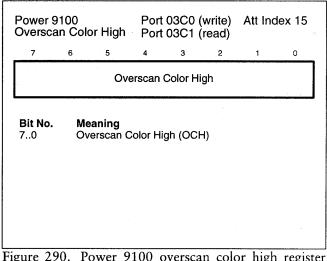

12.8.8. Power 9100 Overscan Color High Register, 182

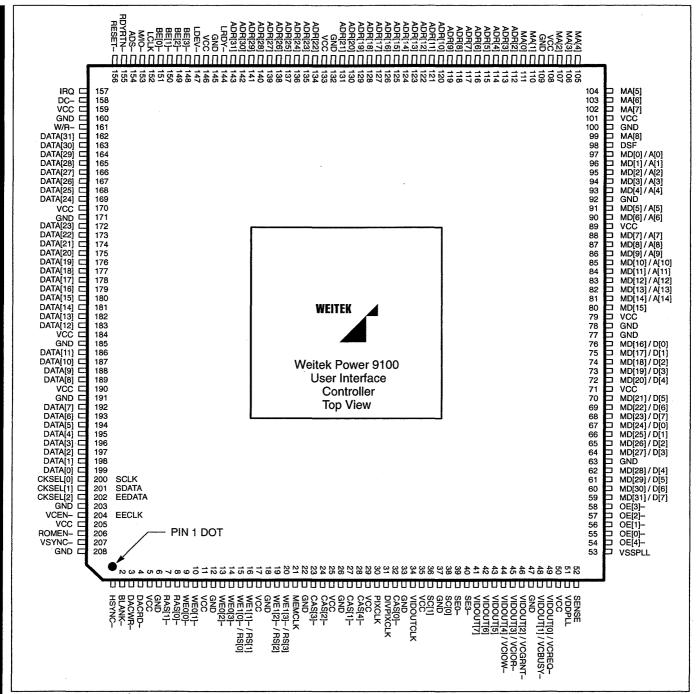

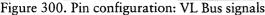

- 13.3. AC Specifications, 18513.4. VL Bus Pin Configuration, 189

- 13.5. PCI Bus Pin Configuration, 190

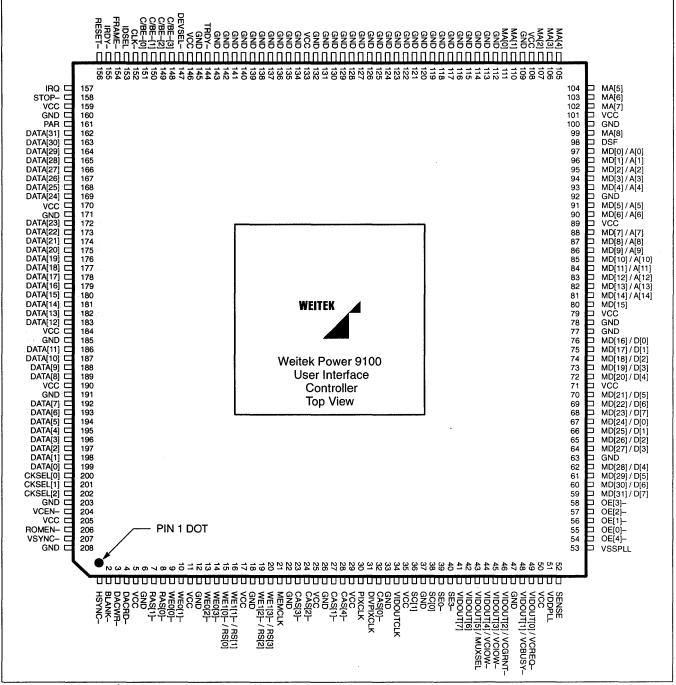

- 13.6. Pin Assignments, 191

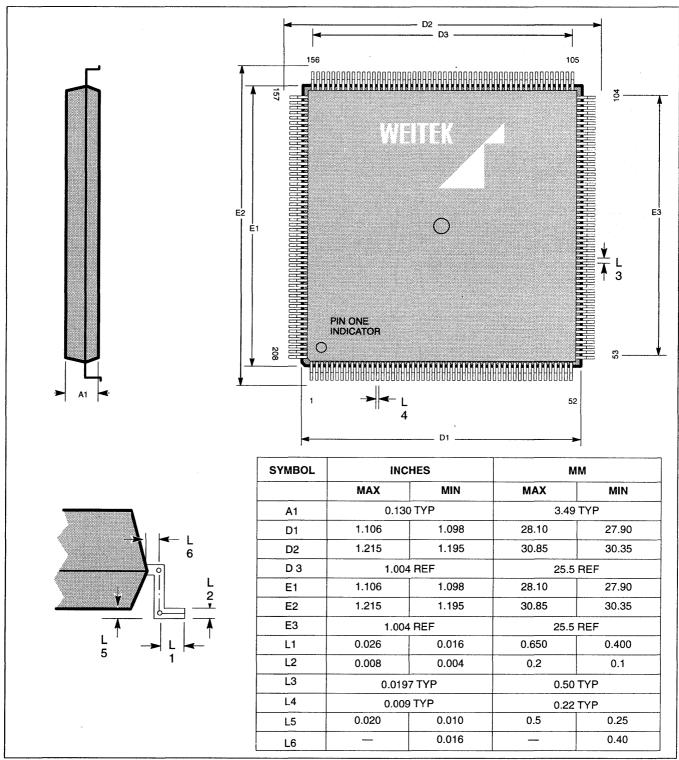

- 13.7. Mechanical Specifications, 199

- 13.8. Test Conditions, 200

v

- 13.9. I/O Characteristics, 201

- 13.10. Ordering Information, 202

## PRELIMINARY DATA November 1993

# Chapter 1. Technical Overview

## Single-Chip 2-D Graphics Accelerator

- Oltra-high-speed local-bus display controller uses workstation display technology to give maximum acceleration with graphical user interfaces such as Microsoft Windows

- Sophisticated architecture, full-custom chip design, and advanced 0.8 micron process technology deliver maximum power at an affordable cost

- ♦ On-chip SVGA unit for DOS compatibility

- ◇ 208-pin plastic QFP package

## High Bandwidth

- ♦ Interleaved VRAM controller uses a PLL timing generator to extract 100% of VRAM bandwidth

- ♦ Sophisticated local-bus controller extracts full bandwidth from PCI and VL host buses

- Supports 32- and 64-bit RAMDACs at speeds up to 200 MHz for maximum display bandwidth

- Pipelined internal architecture is 32 bits wide throughout to ensure maximum throughput

### Full Software Support

- ♦ Drivers for Windows 3.1, Windows NT, OS/2 Presentation Manager, and AutoCAD R10–R12

- ♦ VESA-compatible BIOS

- $\diamond$  DOS application drivers

## Powerful Graphics Features

- ♦ Supports high- and true-color at large screen sizes:

- 24-bit true-color to 1280x1024 pixels

- 16-bit high-color to 1600x1200 pixels

- ♦ Fully accelerates 8-, 15-, 16-, 24- and 32-bits/pixel

- ♦ Draws lines and polygons (with optional pattern fill) at full VRAM bandwidth

- Performs bit block-transfer (BitBlt) from screen to screen at VRAM bandwidth, and from host to screen (with color expansion) at host bus bandwidth

- Provides automatic clipping against window and screen edges

- Supports patterning, plane masking, and boolean operations of pixels during drawing; supports polylines and mesh polygons; supports pick mode

- Oirectly mapped linear frame buffer allows efficient CPU access to frame-buffer memory without banking

- Multimedia support via frame-buffer coprocessor interface

- ♦ Supports VESA power management

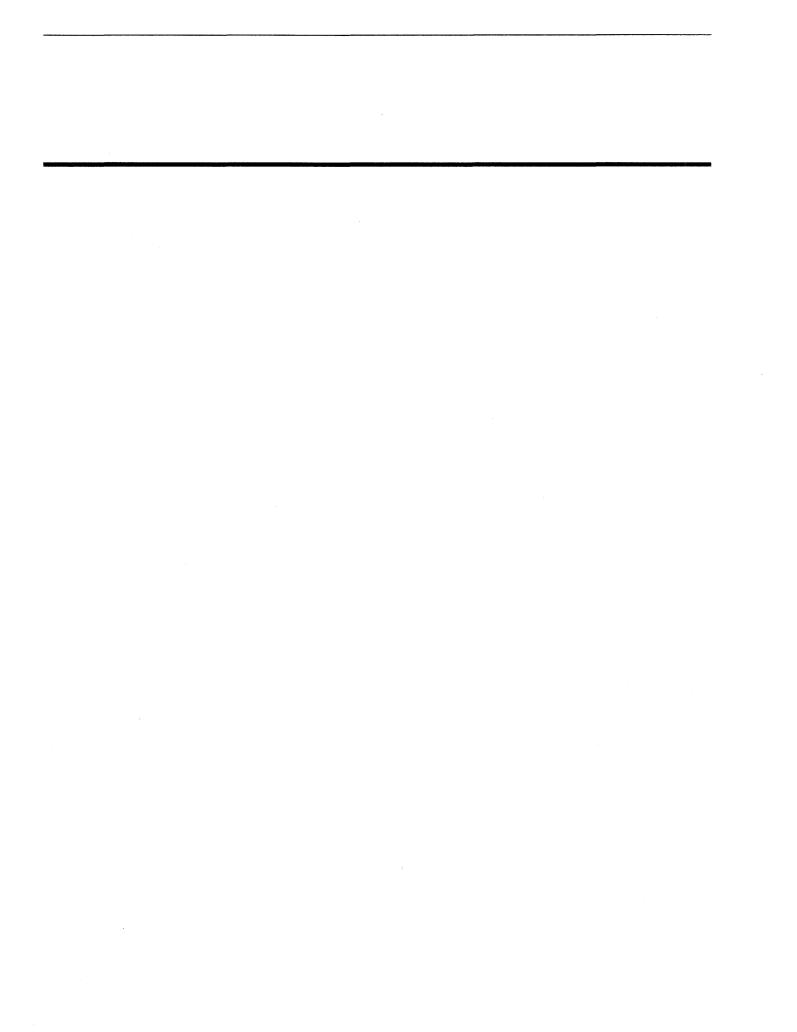

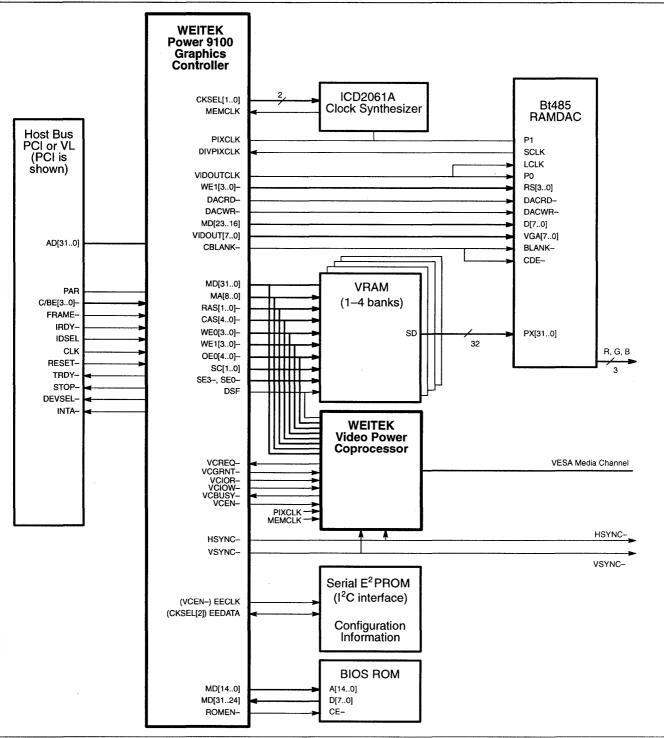

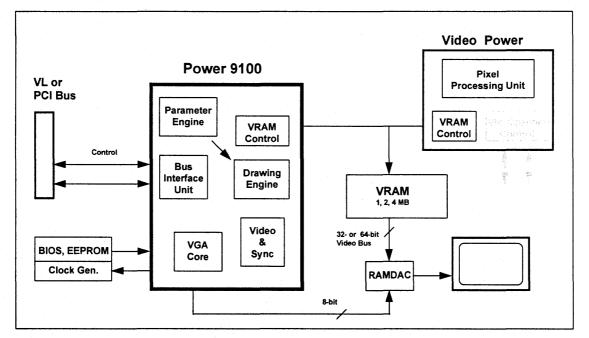

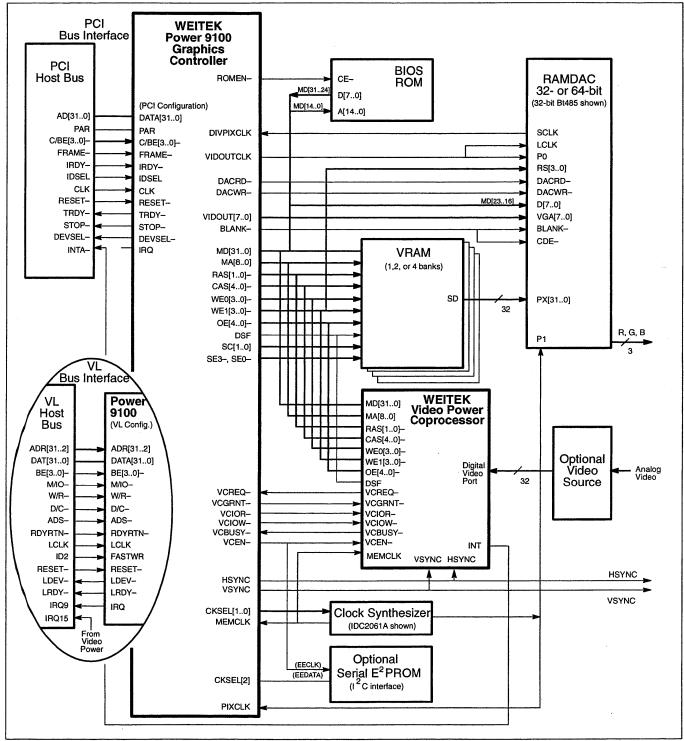

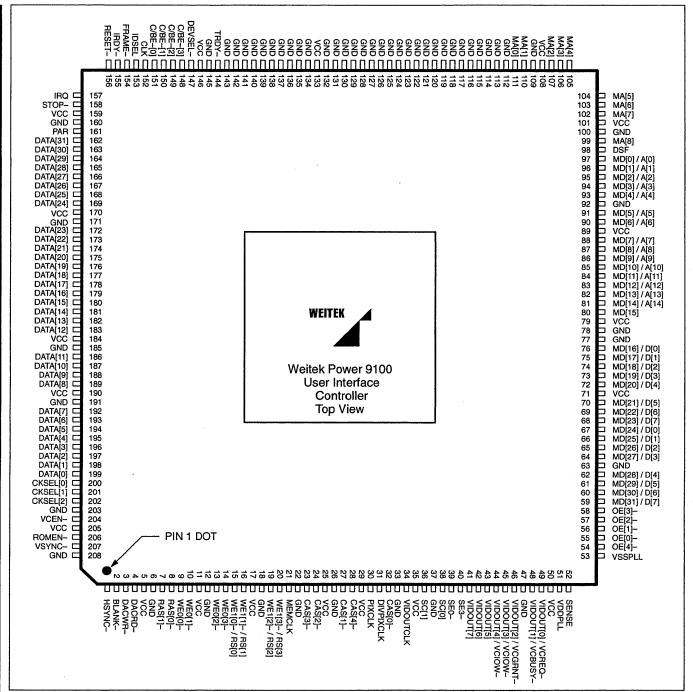

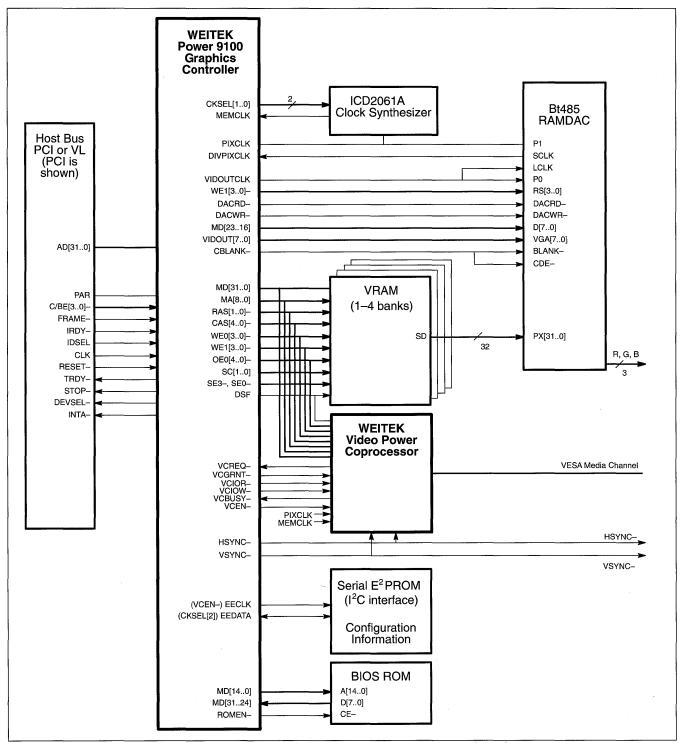

Figure 1. System block diagram

## 1.1. Architecture

The WEITEK Power 91000 is a hard-wired display processor. Designed specifically for high-performance personal computers, its architecture takes full advantage of the speed of video RAM and high-speed local-bus interfaces.

Based on WEITEK's workstation display controllers, the Power 9100 is the latest in a series of controllers designed from an architectural strategy that can be summarized in two sentences:

- 1. Get the highest possible bandwidth.

- 2. Use all of it.

We have found that these simple statements capture the essence of high-performance controller design.

The following sections describe how these principles were applied in the main sections of the Power 9100:

- 1. Frame buffer controller

- 2. Parameter engine

- 3. Drawing engine

- 4. Host bus interface

- 5. Video controller

The Power 9100 contains an additional unit:

6. SVGA unit

for backward compatibility.

## 1.1.1. FRAME BUFFER CONTROLLER

Capturing the highest possible bandwidth starts at the frame buffer. The Power 9100 uses three techniques to achieve (and use) the highest possible frame buffer bandwidth:

- 1. VRAM frame buffer

- 2. Interleaving

- 3. PLL-controlled memory timing

#### VRAM FRAME BUFFER

The Power 9100 uses a VRAM frame buffer for maximum performance. While VRAM is more expensive than DRAM, it is dual-ported; the stream of pixel data needed to refresh the display does not detract from the drawing rate. DRAM systems, in contrast, divide their bandwidth between these two functions, causing drawing rates to degrade as screen sizes increase. The Power 9100 supports screen sizes of up to four megapixels, and full drawing bandwidth is retained even at these large screen resolutions.

#### INTERLEAVING

The Power 9100's two 32-bit banks of VRAM are interleaved for maximum performance.

Interleaving is a technique that takes advantage of the fact that RAM access times are much longer than their writeenable times. Two banks of RAM are placed in parallel, with common address and data lines, but separate write enable lines. One bank contains the even-numbered data words; the other contains the odd-numbered words. With interleaved RAM, writing two words of data only takes one cycle longer than writing one, giving the performance of 64-bit memory, while saving pins and giving a better architectural match to a 32-bit controller.

## PLL-CONTROLLED MEMORY TIMING

To get maximum speed out of memory devices, you have to precisely match a large number of timing specifications. Typical memory controllers approximate this with timing patterns based on the system clock. Since memory speeds and system clock speeds are similar, this approach is too granular to match the memory parameters closely, and it results in significant performance loss.

The Power 9100 can match memory parameters exactly, using a PLL (phase-locked loop) timing generator and a programmable memory controller. This allows the frame buffer to be used at its full theoretical capacity.

### **1.1.2. PARAMETER ENGINE**

The graphics core of the Power 9100 is crucial to using all of the frame buffer's bandwidth. In addition to providing a low-latency path between the host and the frame buffer, the core must provide large amounts of acceleration if the full frame buffer bandwidth is to be used. The importance of acceleration stems from three factors:

- 1. Local-bus interfaces, while fast, are not as fast as the Power 9100's frame buffer.

- 2. General-purpose CPUs are inefficient at simple drawing operations, and cannot perform them at full hostbus bandwidth (let alone full frame-buffer bandwidth).

- 3. The user is better served if the CPU is running applications, not serving as an inefficient graphics controller.

## PRELIMINARY DATA November 1993

## 1.1. Architecture, continued

The Power 9100's graphics accelerator is divided into two loosely coupled graphics engines: the *parameter engine* and the *drawing engine*. The *parameter engine* prepares drawing operations for execution by the drawing engine (which is described in the next section). The parameter engine's basic function is to take input coordinates from the host and convert them to a form usable by the drawing engine. The input parameters include the x,y vertices of polygons and the corners of bit block-transfer (*BitBlt*) regions. The parameter engine tests the vertices against window and screen boundaries, tests for exceptions, and performs trivial rejection. Finally, it transfers commands that pass these tests to the drawing engine to be rendered into the frame buffer.

The parameter engine works independently of the drawing engine; the parameters for a new operation can be loaded while the drawing engine is busy.

The parameter engine prepares four kinds of "polygons" for drawing: quadrilaterals, triangles, lines, and points." It also handles screen-to-screen BitBlt and host-to-screen BitBlt.

The parameter engine handles all exception testing, trivial rejection, status reporting, and access to parameter engine registers. Once the parameter engine verifies that a drawing command should be performed (that is, it has valid parameters and has not been trivially rejected), it passes the operation to the drawing engine. The parameter engine's exception testing is very fast, completing in a few cycles.

#### **1.1.3. DRAWING ENGINE**

The drawing engine performs three basic functions:

- 1. It draws quadrilaterals, triangles, and lines (the *quad* operation).

- 2. It performs screen-to-screen BitBlt (the *blit* operation).

- 3. It performs host-to-screen BitBlt (the *pixel1* and *pixel8* operations).

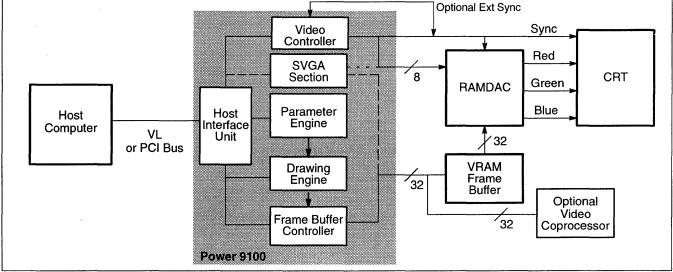

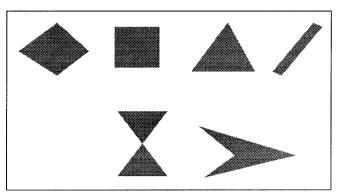

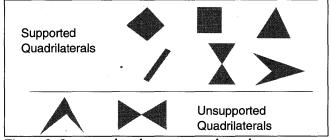

The quad operation draws quadrilaterals, triangle, lines, and points (the last three being treated by the hardware as special cases: quadrilaterals with one or more identical vertices). Triangles, lines, and points can always be rendered correctly, but the drawing engine cannot draw horizontally convex quadrilaterals. That is, it cannot cross from the inside to the outside of the same object more than once per scan line. This means that "bow ties" cannot be drawn (such quads are decomposed into two triangles by the driver software), though "hourglasses" can. See figure 2.

The blit operation copies a rectangular area of the display from one screen location to another.

The pixel1 operation takes monochrome, one-bit-per-pixel data from the host, expands the pixels internally to the current pixel depth (typically by assigning the foreground and background colors to one and zero bits), and writes them to the frame buffer. Up to 32 pixels can be transferred to the Power 9100 in a single word.

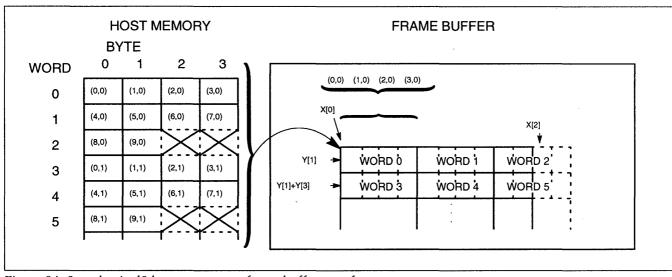

The pixel8 operation takes color pixels of 8, 16, or 32 bits, packed as four, two, or one pixel per word, respectively, and writes them to the frame buffer.

Figure 2. Supported and unsupported quads

### 1.1.4. HOST BUS INTERFACE

The Power 9100 connects directly to PCI and VESA local buses. With small amounts of glue logic it can be connected directly to processor buses.

The Power 9100 itself runs asynchronously to its bus clock. It supports both big-endian and little-endian address formats.

The Power 9100 is memory-mapped; each command has a unique memory address. In many cases, this means that command and data are given in a single write operation: the address specifies what operation is to be performed on the data being transferred.

#### 1.1. Architecture, continued

## 1.1.5. VIDEO CONTROLLER

A typical board design feeds the VRAM shift registers into a RAMDAC, which converts digital pixel data into an analog RGB video signal. The host initializes the control registers and look-up tables in the RAMDAC through the Power 9100's RAMDAC access instructions.

The Power 9100 also generates horizontal and vertical synchronization and blanking signals, and controls the clocking of the video data. The timing of these signals is programmed through the video controller registers. The Power 9100's divided dot clock is completely asynchronous to the Power 9100's main system clock.

The Power 9100 supports 32- and 64-bit RAMDACs, such as the IBM RGB525, the Brooktree Bt 484 and Bt

485, and the Texas Instruments TVP3010 and TVP3020. By supporting RAMDACs with wide input buses at speeds of up to 200 MHz, the Power 9100 has no difficulty supporting large screens at high color depths and ergonomic refresh rates.

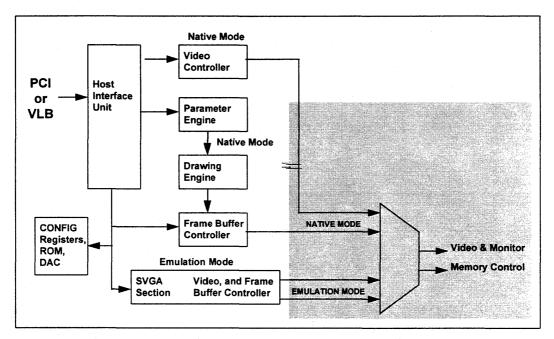

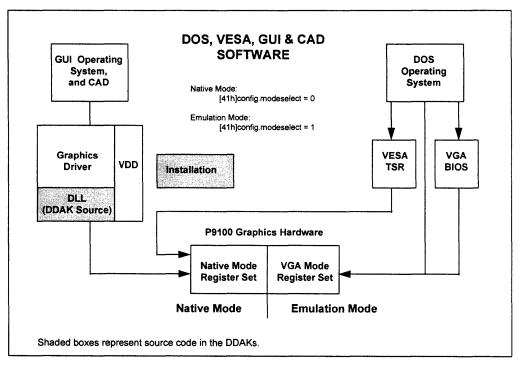

### 1.1.6. SVGA UNIT

For compatibility with older applications, the Power 9100 contains an on-chip SVGA unit which supports screen sizes to 1280x1024, and color depths of up to 24 bits. This SVGA unit is independent of the main graphics engine of the Power 9100, although the two share bus, frame buffer, and video interfaces. Control can be switched between the two graphics units under software control.

## 1.2. Major Differences Between the Power 9100 and the Power 9000

The Power 9100 builds upon the strengths of its predecessor, the Power 9000. This section summarizes the most important differences between the two.

#### **1.2.1. ADDITIONAL FEATURES**

- 1. On-chip VESA Local (VL) Bus interface

- 2. On-chip PCI Bus interface

- 3. On-chip SVGA unit

- 4. Native and SVGA modes

- 5. Full acceleration of 16- through 32-bit graphics

- 6. Higher clock speeds

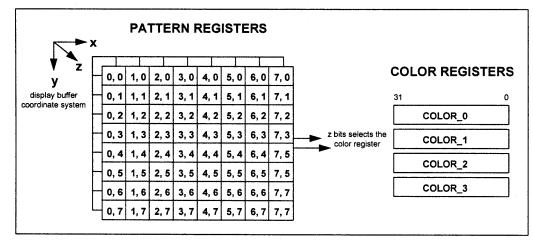

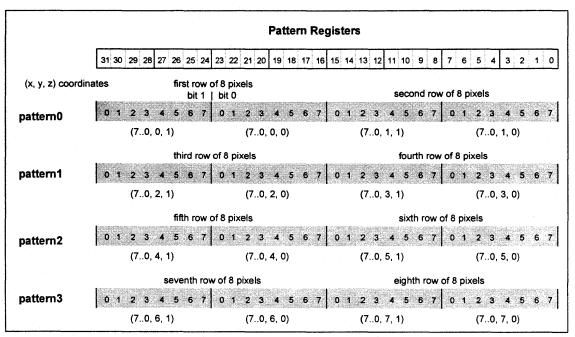

- 7. Four-color pattern RAM (but reduced from 16x16 to 8x8) can be used for four-color dither at full speed

- 8. Aperture memory mapping (frame buffer can be mapped into a 64 KB aperture in addition to its usual 4 MB linear mapping)

- 9. Video coprocessor support

- 10. ROM BIOS control logic

- 11. Configuration EEPROM control logic

- 12. Clock generator control logic

- 13. Serial clock and serial enable generation for VRAMs

- 14. Text transparency

- 15. 256 raster-ops

#### **1.2.2. ADDRESSING**

Power 9100 addressing and general address formats are different from those on the Power 9000.

PRELIMINARY DATA November 1993

## 1.3. Details of Graphics Operation

### **1.3.1. THE GRAPHICS PIPELINE**

Graphics operations flow through the *graphics pipeline*, first through the parameter engine, and then through the stages of the drawing engine.

#### THE PARAMETER ENGINE

*Functions.* The parameter engine determines what will happen as the result of each drawing operation. It calculates status information, including whether the operation is clipped by the viewing window or the screen edge, and whether the operation can be drawn at all before passing the operation to the drawing engine. If the drawing engine is busy, or if the request contains illegal parameters, the parameter engine does not pass on the request. (The parameter engine performs these tests only on coordinate register loads and drawing commands. Other operations, such as setting color registers or video timing registers, bypass the parameter engine.)

The parameter engine performs clipping calculations on each x, y vertex. It compares these points against all four edges of the screen and viewing window, and against each other. It also tests for trivial rejection and trivial acceptance.

The parameter engine detects, but cannot correct an illegal request, such as a request for a horizontally convex quad. Such quadrilaterals must be rendered in software. The status register flags such problems. In addition, the interrupt signal can be used to interrupt the host when such exceptions occur.

*Access*. All accesses to parameter engine functions and registers complete in a few cycles; the parameter engine is always accessible.

#### THE DRAWING ENGINE

*Functions*. The drawing engine accepts one drawing operation at a time from the parameter engine. When processing a drawing operation, it first determines which pixels are "touched" by the drawing process (*scan conversion*), then determines the color value of each touched pixel (*raster ops*).

Scan conversion. Two line-drawing engines follow the left and right edges of the quadrilateral on each scan line, and a pixel-processing engine fills the region between these edges. (Pixel1, pixel8, and blit operations are limited to rectangular areas, while the quad operation can have edges at any angle).

*Raster ops.* The color of each touched pixel is determined by the raster-op function, which is further conditioned by the contents of other registers (see section 1.3.5).

Access. The drawing engine can remain busy for long periods when drawing large quads or performing a blit operation on a large portion of the screen. The quad and blit operations are started by a read operation. The read requests that the operation take place, and returns the contents of the status register, which indicates whether or not the request has been granted. The Power 9100 does not accept a request if the drawing engine is busy, or if an exception has occurred, nor does it queue requests. Therefore, the software must check the status register, which contains both exception and drawing engine status bits, and resubmit any quad or blit request that is not accepted. While no new drawing operations can be started until the drawing engine is idle, the host can load the parameter engine's coordinate registers with the vertices of a new operation while the drawing engine is busy, thereby overlapping the processing of two objects.

### **1.3.2. DRAWING QUADRILATERALS**

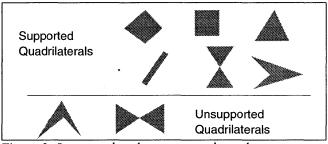

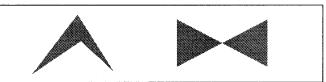

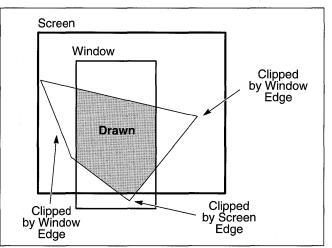

The drawing engine assigns the two edges at either the topmost or bottom-most vertex to its two Bresenham *line-drawing engines*. These engines do not actually draw anything in the frame buffer, but they traverse the boundaries of the quadrilateral on each scan line. The *pixel-processing engine* then fills in the pixels between the boundaries found by the line-drawing engines. (This filling operation is also clipped against the clipping window and screen boundaries.) See figure 3. When a line-drawing engine reaches another vertex, it starts down the new edge.

In *oversized* mode, the Power 9100 draws perimeter pixels according to the Bresenham algorithm. Oversized mode must be selected to draw points and lines, as X11's drawing rules do not "touch" pixels in zero-width objects (meaning nothing is drawn).

Figure 3. A quad clipped against window and screen

## 1.3. Details of Graphics Operation, continued

In X11 mode, the Power 9100 draws only those pixels whose centers lie within the perimeter of the quad. Pixels whose centers lie precisely on the perimeter are drawn in accordance with X11's tie-breaker rules. (See figure 4.) Coordinates can either be specified relative to the clipping window or relative to the previous vertex.

Polylines, meshed triangles, and meshed quadrilaterals are all supported; they are drawn by transferring the new vertices and issuing another draw command.

## 1.3.3. DRAWING BIT MAPS

To transfer a bit map to the screen, the host first sets up the x, y coordinates of the destination, and then transfers data to the Power 9100 with the pixel1 and pixel8 operations. The Power 9100 draws the pixels on the screen, auto-incrementing the current x, y location after each pixel. Bit-map drawing proceeds from left to right; when it reaches the right-hand edge of the target bit map, the Power 9100 automatically wraps to the next line.

The pixel8 operation draws colored pixels; up to four eight-bit pixels (or two 16-bit pixels, or one 32-bit pixel) are transferred and drawn through a single bus transfer from the host. This mode is used to transfer color images.

The pixel1 operation, which draws monochrome bit maps, is ideal for text transfer. Its basic operation is similar to pixel8, but instead of transferring, say, four eight-bit pixels per operation, it transfers up to 32 one-bit pixels. The Power 9100 expands the one and zero bits of the data word into pixels at the current color depth. (The Power 9100 expands these values according to the raster-op function described in section 1.3.5.)

Pixel data must be padded out to multiples of 32 bits per scan line for pixel8 transfers; leftover pixels in the current word do not wrap to the next line. Pixel1 allows the left-over pixels to wrap, however, making it especially suitable for sending narrow blocks of monochrome data, such as character bit maps.

### **1.3.4. BIT BLOCK TRANSFER**

The blit operation moves a rectangular block of pixels from one part of the screen to another. It handles overlapping source and destination blocks properly; the source block arrives unchanged at the destination, as if it were moved off-screen, then copied back at its new destination.

Like quad, blit is a "fire-and-forget" operation; once initiated, it runs to completion without additional attention from the host. As a large blit can involve over a million pixels, the host driver code should test the busy bit in the Power 9100's status register before attempting another drawing operation when a blit could be in progress.

## **1.3.5. COLOR SELECTION**

Once a pixel has been touched, there still remains the question of what color it will be. Screen color is selected at five levels:

- 1. the initial (source) color

- 2. the pattern color

- 3. the raster-op color

- 4. the plane mask

- 5. the RAMDAC look-up table color (8-bit modes only; higher pixel depths use direct color)

The Power 9100 applies each of these in turn. The *pattern* RAM allows imposition of an 8x8-bit repeating pattern on the data. See figure 5. The *raster-op* function is a three-input boolean function controlled by an eight-bit minterm array. The three inputs are:

- 1. The source color

- 2. The destination color (the color value currently at the *x*,*y* location being written)

- 3. The color registers color[3..0].

The Power 9100 applies the same function to each of the bits in the pixel.

PRELIMINARY DATA November 1993

## 1.4. Host Bus Interface

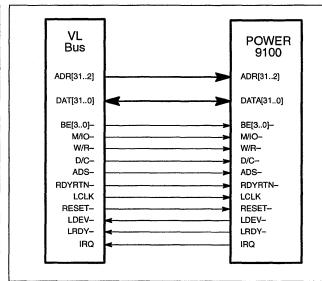

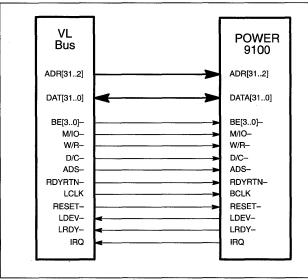

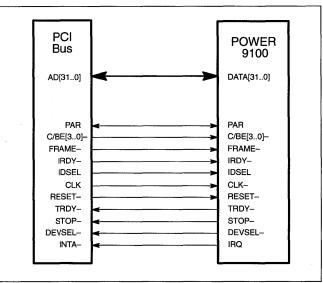

The Power 9100 supports the VL and PCI buses directly, with no glue logic. See figures 6 through 9. Other buses can be accommodated with a small amount of external glue logic.

Some pins on the Power 9100 change function depending on which bus is selected. Rather than introduce a confus-

Figure 6. VL bus interface connection

|           | VL Bus |                      |  |  |  |  |  |  |  |  |  |  |  |

|-----------|--------|----------------------|--|--|--|--|--|--|--|--|--|--|--|

| Signal    | I/O    | Description          |  |  |  |  |  |  |  |  |  |  |  |

| DATA[310] | I/O    | Data bus             |  |  |  |  |  |  |  |  |  |  |  |

| ADR[312]  | Input  | Address bus          |  |  |  |  |  |  |  |  |  |  |  |

| BE[30]-   | Input  | Byte enable          |  |  |  |  |  |  |  |  |  |  |  |

| W/R-      | Input  | Write or read status |  |  |  |  |  |  |  |  |  |  |  |

| M/IO-     | Input  | Memory or I/O status |  |  |  |  |  |  |  |  |  |  |  |

| FASTWR    | Input  | ID2 identifier       |  |  |  |  |  |  |  |  |  |  |  |

| ADS-      | Input  | Address data strobe  |  |  |  |  |  |  |  |  |  |  |  |

| LDEV-     | Output | Local device         |  |  |  |  |  |  |  |  |  |  |  |

| LRDY-     | Output | Local ready          |  |  |  |  |  |  |  |  |  |  |  |

| RDYRTN-   | Input  | Ready return         |  |  |  |  |  |  |  |  |  |  |  |

| IRQ       | Output | Interrupt request    |  |  |  |  |  |  |  |  |  |  |  |

| BCLK      | Input  | VL clock             |  |  |  |  |  |  |  |  |  |  |  |

| RESET-    | Input  | Reset                |  |  |  |  |  |  |  |  |  |  |  |

| D/C-      | Input  | Data or code status  |  |  |  |  |  |  |  |  |  |  |  |

Figure 8. VL bus interface signals

ing third signal nomenclature to that of PCI and VL, we have provided two pin configuration diagrams: one for each bus, each using that bus' signal naming conventions. See section 13.4 for the pin configuration.

Figure 7. PCI bus interface connection

|           | F      | PCI Bus                      |

|-----------|--------|------------------------------|

| Signal    | I/O    | Description                  |

| DATA[310] | I/O    | Address and data bus         |

| C/BE[30]- | Input  | Bus command/byte enable      |

| PAR       | I/O    | Parity                       |

| IDSEL     | Input  | Initialization device select |

| STOP      | Output | Stop                         |

| FRAME-    | Input  | Cycle frame                  |

| DEVSEL-   | Output | Device select                |

| TRDY-     | Output | Target ready                 |

| IRDY-     | Input  | Initiator ready              |

| IRQ       | Output | Interrupt request            |

| CLK-      | Input  | PCI clock                    |

| RESET-    | Input  | Reset                        |

|           |        |                              |

|           |        |                              |

Figure 9. PCI bus interface signals

## 1.5. Frame Buffer and Video Interfaces

Figure 10 illustrates Power 9100 RAMDAC, frame buffer, and video pin connections.

Figure 10. RAMDAC, frame buffer, and video connections

# PRELIMINARY DATA

November 1993

# 1.5. Frame Buffer and Video Interfaces, continued

# 1.5.1. SIGNAL DESCRIPTIONS

| Signal   | Туре   | Description                                                                                                                                                                                                                                             |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD[310]  | 1/0    | Memory data bus                                                                                                                                                                                                                                         |

| MA[80]   | Output | Memory address bus                                                                                                                                                                                                                                      |

| RAS[10]- | Output | Row address strobes                                                                                                                                                                                                                                     |

| CAS[40]- | Output | Column address strobes. CAS[0]- controls the least-significant 16 bits of bank 0; CAS[4]-<br>controls the most-significant bits of bank 0 (necessary for VGA transfers). Note that in two-<br>bank systems, bank 1 is controlled by CAS[3]-, not CAS[1] |

| WE0[30]- | Output | Write-enable for the individual bytes in bank 0 (2-bank systems), or banks 0–1 (4-bank systems)                                                                                                                                                         |

| WE1[30]- | Output | Write-enable for the individual bytes in bank 1 (2-bank systems), or banks 2-3 (4-bank systems)                                                                                                                                                         |

| OE[40]-  | Output | Output Enables. OE[0]- controls the least-significant 16 bits of bank 0; OE[4]- controls the most-significant bits of bank 0 (necessary for VGA transfers)                                                                                              |

| DSF      | Output | VRAM special function pin                                                                                                                                                                                                                               |

| DACRD-   | Output | RAMDAC control line                                                                                                                                                                                                                                     |

| DACWR-   | Output | RAMDAC write control signal                                                                                                                                                                                                                             |

| MEMCLK   | Input  | Main chip clock                                                                                                                                                                                                                                         |

| ROMEN-   | Output | BIOS ROM enable                                                                                                                                                                                                                                         |

| EECK     | Output | EEPROM clock control signal                                                                                                                                                                                                                             |

| EEDA     | 1/0    | EEPROM data control signal                                                                                                                                                                                                                              |

| VDDPLL   | Input  | Supply voltage for on-chip clock generator                                                                                                                                                                                                              |

| VSSPLL   | Output | Ground for on-chip clock generator                                                                                                                                                                                                                      |

Figure 11. Memory control signals

| Signal         | Туре   | Description                                                                                    |

|----------------|--------|------------------------------------------------------------------------------------------------|

| SE[3]–, SE[0]– | Output | VRAM serial shift enable                                                                       |

| SC[10]         | Output | VRAM serial shift clock                                                                        |

| VIDOUT[70]     | Output | Video data out (SVGA modes)                                                                    |

| VIDOUTCLK      | Output | Video data clock out                                                                           |

| HSYNC-         | 1/0    | Horizontal synchronization. Normally an output; can also be used as an input for external sync |

| VSYNC-         | 1/0    | Vertical synchronization. Normally an output; can also be used as an input for external sync   |

| BLANK-         | Output | Blanking interval                                                                              |

| PIXCLK         | Input  | Pixel clock                                                                                    |

| DIVPIXCLK      | Input  | Divided pixel clock                                                                            |

| CKSEL[20]      | Output | Frequency synthesizer control                                                                  |

Figure 12. Video control signals

| 1.5. Frame Buffer and Video Int | erfaces, continued |

|---------------------------------|--------------------|

|---------------------------------|--------------------|

| Signal  | Туре   | Description                                                                                                                                                          |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCBUSY- | Input  | Video coprocessor busy. Video coprocessor is busy; I/O reads and writes will not succeed. This signal should be pulled up to VCC with a 10 K $\Omega$ resistor       |

| VCEN-   | Output | Video coprocessor enable. When asserted, video coprocessor is active. Resets video co-<br>processor when de-asserted                                                 |

| VCGRNT- | Output | Video coprocessor bus grant. Signals that the Power 9100 has released the frame buffer                                                                               |

| VCIOR-  | Output | Video coprocessor I/O read. Requests a read from a video coprocessor register                                                                                        |

| VCIOW-  | Output | Video coprocessor I/O write. Requests a write to a video coprocessor register                                                                                        |

| VCREQ-  | Input  | Video coprocessor bus request. Requests that the video coprocessor be given control of the bus. This signal should be pulled up to VCC with a 10 K $\Omega$ resistor |

Figure 13. Video coprocessor signal description

## 1.6. Video Coprocessor Interface

The video coprocessor interface allows a separate coprocessor to share the Power 9100's frame buffer and host interface. Such a coprocessor could provide features to accelerate still pictures, video animation, or 3-D rendering.

The video coprocessor interface allows the host to read and write data from the video coprocessor, while the video coprocessor grant and release functions allow the video coprocessor to take and relinquish control of the frame buffer. The video coprocessor pre-empt function lets the Power 9100 regain control to perform high-priority tasks such as memory refresh.

# 1.7. Related Documents

For availability of Power 9100 documentation, see your WEITEK sales representative. Upcoming titles include:

*Power 9100 Programmer's Reference Manual.* Full information on registers and commands for both P9100 and SVGA modes.

*Power 9100 Application Notes.* Practical techniques for Power 9100 design, including examples of complete board designs for both VL and PCI.

*Power 9100 Manufacturing Kits.* Artwork, programmable logic equations, and manufacturing drawings for tested, cost-effective Power 9100 designs.

# PRELIMINARY DATA

November 1993

# Chapter 2. Quick Reference

[Editor's Note: Will necessarily be completed last.]

# 1.2. Major Differences between the Power 9100 and the Power 9000, continued

| Registers<br>(# of regs)                  | Power 9000 or<br>Power 9100 | New/Changed/<br>Replaced | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|-------------------------------------------|-----------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Configuration (8)                         | Power 9100                  | New                      | These registers specify device and vendor identifiers; enable<br>the RAMDAC pallet, memory space access, and I/O space ac-<br>cess; specify base addresses; enable VGA; and select P9100<br>or SVGA mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| Color (color[0] through color[3])         | Power 9100                  | New                      | color[0] replaces Power 9000 foreground register; color[1] re-<br>places Power 9000 background register. Both are used in two<br>color patterns. Color[2] and color[3] are used in new four-colo<br>patterns. Each register is 32 bits wide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| Pattern (pattern[0]<br>through pattern[3] | Power 9100                  | New                      | Replace Power 9000 pattern registers. (Each register is 32 bits wide.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| alt_read_bank<br>alt_write_bank           | Power 9100                  | New                      | These registers specify the high-order address bits (in register<br>bits 22–14) when alternate aperture frame buffer banking logic<br>is used to read/write directly from the frame buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Software (4)                              | Power 9100                  | New                      | These registers are reserved for the system software to use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| SVGA                                      | Power 9100                  | New                      | The Power 9100 has all of the registers found on the W5286 on its SVGA unit; they are identical to the W5286 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| System configuration (sysconfig)          | Both                        | Changed                  | New field: bits 28–26 specify 8, 16, or 32 bits per pixel for the drawing engine<br>Deleted field: version (bits 2–0), which is now contained in a configuration register; bits 2–0 are always zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Memory configuration<br>(mem_config)      | Both                        | Changed                  | New fields:<br>bits 31–29 are reserved<br>bits 28–27 control the delay for blank generation<br>bit 26 inverts the MUXSEL pin<br>bits 25–24 set the timing patterns for shift clocks<br>bits 23–22 set timing patterns for shift clocks as well<br>bits 21–19 set the frequency of the DAC load clock<br>bit 18 controls the skew between the DAC load clock and the<br>VRAM shift clocks<br>bits 17–14 set the frequency of the internal crtc divided dot<br>clock (DDOTCLK)<br>bits 13–10 set the frequency of the VRAM shift clock state ma-<br>chine<br>bit 9 forces memory and video into reset state<br>bit 8 is reserved<br>bit 7 enables RAMDAC back-to-back transfer checking<br>bit 6 specifies an adjustment for VRAM write timing<br>bit 4 specifies an adjustment for VRAM read timing<br>bit 3 specifies an adjustment for VRAM read timing<br>bit 3 specifies the number of bits for the CAS section of the<br>VRAMs<br>bits 1–0 specify the number of VRAM banks connected |  |  |  |  |  |  |  |  |  |

Figure 14. Register differences between the Power 9100 and the Power 9000

POWER 9100 GRAPHICS

# PRELIMINARY DATA

November 1993

# 1.2. Major Differences between the Power 9100 and the Power 9000, continued

| Register(s)                                  | Power 9000 or<br>Power 9100 | New/Changed/<br>Replaced | Notes                                                                                                                                                                                                                                                     |

|----------------------------------------------|-----------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Raster                                       | Both                        | Changed                  | New fields:<br>bit 15 enables pixel1 transparent mode<br>bit 14 specifies pattern depth (2-color or 4-color pattern)<br>Changed fields:<br>bit 17 enables transparent pattern<br>bits 7–0 minterms (bits 15–0 on Power 9000)<br>bits 12–8 now always zero |

| Foreground (fground)<br>Background (bground) | Power 9000                  | Replaced                 | Replaced by new Power 9100 color registers.                                                                                                                                                                                                               |

| Pattern                                      | Power 9000                  | Replaced                 | Replaced by new Power 9100 pattern registers.                                                                                                                                                                                                             |

Figure 14, continued. Register differences between the Power 9100 and the Power 9000

5

.

.

14

PRELIMINARY DATA November 1993

# Chapter 3. Memory Map

### 3.1. Overview

.

The host controls the Power 9100 by setting registers, loading pseudo-registers, and issuing commands. Power 9100 registers, all of which are 32 bits wide, contain the parameters for Power 9100 operations and maintain status information. *Pseudo-registers* minimize the number of parameters that must be specified per drawing operation. *Commands* initiate the drawing operations whose parameters are defined by register and pseudo-register settings.

The Power 9100 is memory-mapped: The address is divided into control fields that determine the actions to be performed. The sections of memory reserved for Power 9100 addresses must be marked as non-cacheable; because the Power 9100 alters its own register contents, memory caching would give invalid data.

The Power 9100 performs all tasks sequentially. The host must ensure that requests for drawing operations are accepted, either by checking Power 9100 status to verify that the previous drawing operation has completed before issuing a new request, or, for operations that return status, by checking the status of a requested operation before issuing a new request. The status register contents reflect status conditions, as defined in section 4.4.2. The host processor is also responsible for proper byte alignment of data it sends across the bus to the Power 9100.

This chapter describes all Power 9100 address formats and registers. Subsequent chapters describe the Power 9100 registers, pseudo-registers, and commands, and define the specific address format for accessing each. For illustrations and examples of Power 9100 operation, see Chapter 5.

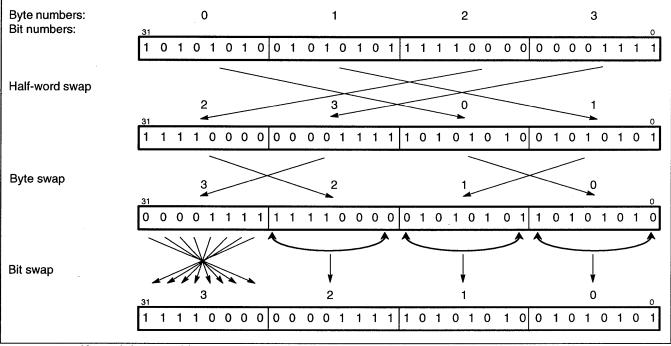

# 3.1.1. BIG-ENDIAN AND LITTLE-ENDIAN MODES

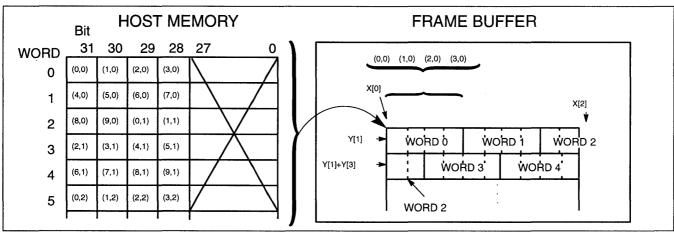

The Power 9100 data bus connects to the host bus so that transfer of a 32-bit word preserves the significance of the data bits (bit 0 is the least significant bit and bit 31 is the most significant bit). Because the Power 9100 stores all data in big-endian mode, it is necessary to convert the mode when transferring data to and from a host system that uses little-endian mode. The H, B, and b bits enable swapping of half-words, bytes, and bits respectively. This is used most often when accessing the frame buffer. Figure 15 illustrates the swapping effect of setting the H, B, and b bits. The H, B and b bits are derived from different registers depending on the address format used.

Figure 15. Half-word, byte, and bit swapping

## 3.2. Conventions and Notation

The conventions and notation defined in this section are used throughout this chapter.

All discussions of registers and address formats define all 32 bits. Illustrations appear as shown in the example in figures 16 and 17, with bit numbers identified across the top of the illustration and field sizes called out below. The field contents are identified in the illustration and defined in a table that accompanies the illustration.

The prefix "c." on a field name indicates that the most-significant bit in the field is a field write control bit. When writing to a register, it is not always desirable to replace the entire register contents. For example, clearing a bit in the interrupt register is a function that needs to be done without altering the information contained in other register fields. When writing to a register, setting a field write control bit to 1 replaces that field with the new data; setting a field write control bit to 0 leaves the contents of the field unaltered. On a register read, field write control bits are always 1, which makes it easy to save and restore all of the fields of a register.

|                        | Bit numbers:      | 31 24            | 23 | ·        | 210 |

|------------------------|-------------------|------------------|----|----------|-----|

| Field lengths:         | Address contents: | CONFIG[19].WBASE |    | Register | 0 0 |

| rieid ierigins. 8 22 2 | Field lengths:    | 8                |    | 22       | 2   |

Figure 16. Sample address format illustration

| Bit numbers:      | 31 |   |   |   |   |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |   |   |   |   |     | 6    | 5         | 4   | 3   | 2 | 1         | ( |

|-------------------|----|---|---|---|---|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|---|---|---|---|-----|------|-----------|-----|-----|---|-----------|---|

| Address contents: | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0    | Γ         |     |     |   |           |   |

| Field lengths:    |    |   |   |   |   |   |   |   |   |   |   |   | 2 | 26 |   |   |   |   |   |   |   |   |   | 0 | .vt | olan | kec<br>c. | pic | ked |   | 2<br>idle |   |

Figure 17. Sample register illustration

PRELIMINARY DATA

November 1993

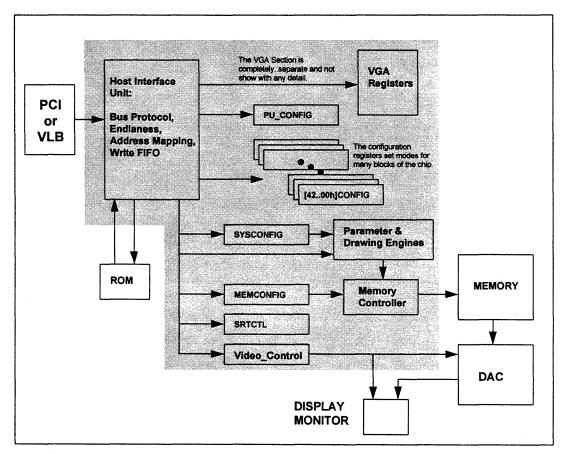

## 3.3. Configuration Registers

The PCI bus specification requires a group of configuration registers be present in the configuration address space. These registers are used to control memory and I/O mapping as well as various other control functions. The Power 9100 fully supports the requirements of the PCI specification.

When operating in the VL bus mode the same functionality is supported by mapping the configuration registers into the I/O address space. Two double words of I/O address space are used to access the configuration registers. The first is used as an index into the configuration address space, the second is used as the data transfer register. These configuration registers are present independent of the mode (VGA or native) that the device is currently operating in. The index registers can be placed at several locations in the I/O address space. The actual location of these registers is controlled by the setting of the PU\_CON-FIG.CFGBA field. The value of this field is determined during the reset sequence (see section 3.3.1).

Configuration registers that are not implemented must follow the absent PCI configuration register convention – ignore all writes, read as all zeroes. When accessed through I/O space all operations must be a single byte, no assembly or disassembly of data is supported.

| 31 | Index Register | 16 | 15 3            | 2 | - | 0 |   |

|----|----------------|----|-----------------|---|---|---|---|

|    | 0              |    | PU_CONFIG.CFGBA | 0 | 0 | 0 |   |

|    | 16             |    | 13              |   | 3 |   |   |

| 31 | Data Register  | 16 | 15 3            | 2 |   | 0 |   |

|    | 0              |    | PU_CONFIG.CFGBA | 1 | 0 | 0 |   |

|    | 16             |    | 13              |   | 3 |   | _ |

Figure 18. Configuration Index Registers I/O space mapping (VL bus mode)

## 3.3.1. POWER-UP CONFIGURATION

The deassertion of reset- forces the system to sample the frame buffer data bus to determine its power-up configuration. Data bus drivers have built-in pull-down resistors causing the bus to eventually float to a low state. By placing large (~10K $\Omega$ ) pull-up resistors on the data bus selected bits can be forced into the high state. The initial settings of the data bus is preserved in the read-only PU\_CONFIG register.

| Power-up Configuration | Bits       | (PU | _CONFIG register)                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 30 29 27            | 26         | 25  | 24 5 4 3 1 0                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BUS CFGBA              |            |     | Reserved Reserved                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2 3<br>INIT_MODESELEC  | 1<br>T     | 1   | 19<br>INIT_VGA_PRESENT<br>INIT_VGA_PRESENT<br>MEM_DEPTH                                                                                                                                                                                                                                                                                                                                                                       |

| Field                  | Bit        | ts  | Contents                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BUS<br>CFGBA           | 31–<br>29– |     | The bus signalling protocol.<br>11 = Reserved<br>10 = VESA Local Bus<br>01 = PCI Bus<br>00 = Reserved (internal Testing mode)<br>I/O address for configuration register index and data registers.<br>000 = $\$9100$ , $\$9104$ 001 = $\$9108$ , $\$910C$<br>010 = $\$9110$ , $\$9114$ 011 = $\$9118$ , $\$911C$<br>100 = $\$9120$ , $\$9124$ 101 = $\$9128$ , $\$912C$<br>110 = $\$9130$ , $\$9134$ 111 = $\$9138$ , $\$913C$ |

| INIT_MODESELECT        | 26         | 6.  | The initial value for CONFIG[65].MODESELECT                                                                                                                                                                                                                                                                                                                                                                                   |

| INIT_VGA_PRESENT       | 25         | 5   | The initial value for CONFIG[10].VGA_PRESENT                                                                                                                                                                                                                                                                                                                                                                                  |

| MEM_DEPTH              | 4          |     | Depth of memory Chips.<br>0 = 256K $1 = 128K$                                                                                                                                                                                                                                                                                                                                                                                 |

| MBOARD                 | 0          |     | Motherboard VGA address decode control.<br>0 = On motherboard 1 = On add-in board                                                                                                                                                                                                                                                                                                                                             |

Figure 19. Power-up Configuration bits. (PU\_CONFIG register)

# 3.3. Configuration Registers, continued

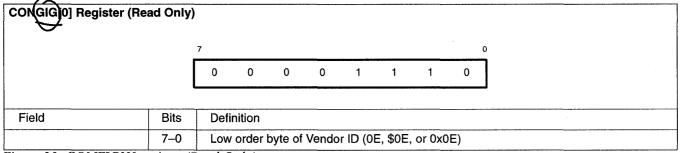

# 3.3.2. CONFIG[0] REGISTER

Figure 20. CONFIG[0] register (Read Only)

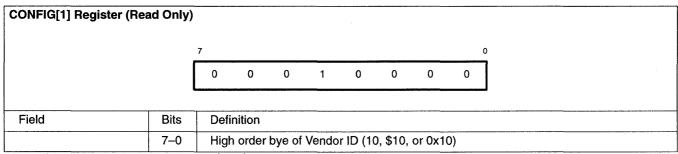

# 3.3.3. CONFIG[1] REGISTER

Figure 21. CONFIG[1] register (Read Only)

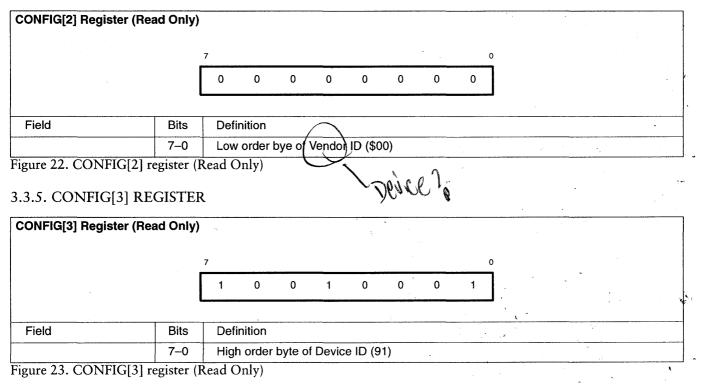

# 3.3.4. CONFIG[2] REGISTER

# PRELIMINARY DATA

November 1993

# 3.3. Configuration Registers, continued

# 3.3.6. CONFIG[4] REGISTER

#### **CONFIG[4] Configuration Register** 7 0 3 2 5 4 1 1 0 0 0 0 1 1 1 1 1 SHADOW DAC MEM\_ENABLE-**IO\_ENABLE** Field Bits Contents SHADOW\_DAC 5 Shadow access to the RAMDAC palette. 0 = shadow disabled, Power 9100 responds to palette accesses. 1 = shadow enabled, Power 9100 does not respond to palette write accesses (default). MEM\_ENABLE 1 Memory space enable. 0 = disabled, Power 9100 doesn't respond to any memory accesses. (default) 1 = enabled, Power 9100 responds to memory space accesses. **IO\_ENABLE** 0 I/O space enable. 0 = disabled, Power 9100 does not respond to any I/O space accesses. (PCI default) 1 = enabled, Power 9100 responds to I/O space accesses. (VL default)

Figure 24. CONFIG[4] configuration register

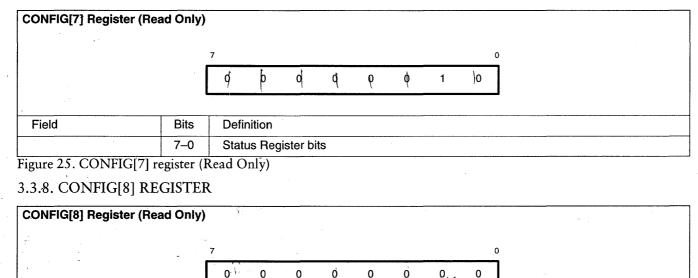

# 3.3.7. CONFIG[7] REGISTER

|       | · •        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field |            | Bits | Definition of the second secon |  |

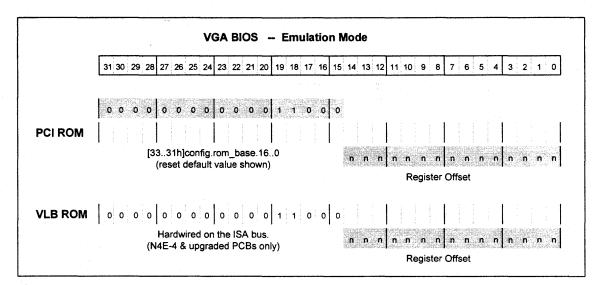

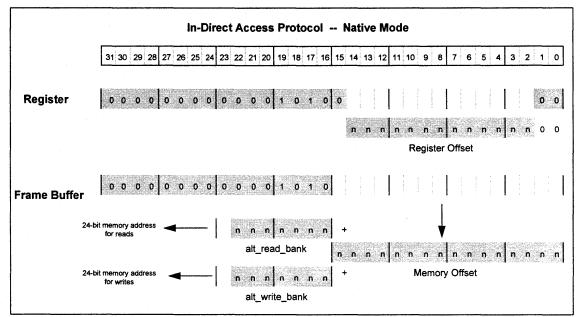

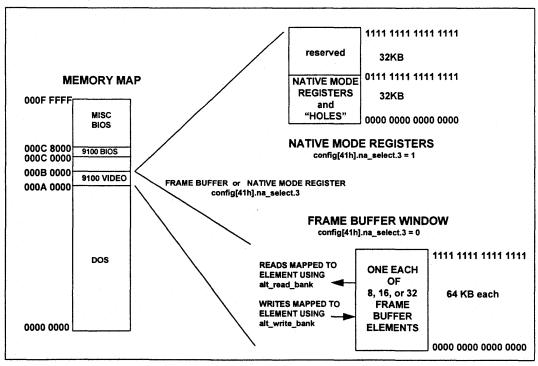

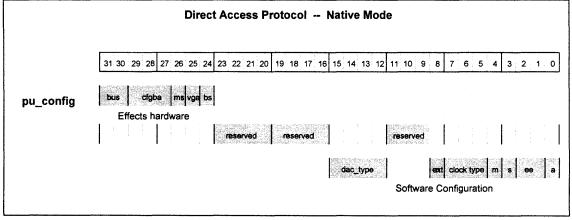

|       |            | 70   | Revision ID. Current revision ID.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |